Fターム[5F033KK38]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 透光性導電膜材料 (79)

Fターム[5F033KK38]に分類される特許

1 - 20 / 79

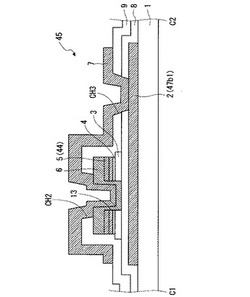

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

液晶表示装置

【課題】製造コストを削減するとともに歩留まりを向上し、かつプロセス設計が容易である液晶表示装置を提供すること。

【解決手段】液晶表示装置1において、半導体層ASIと半導体層ASIの液晶材側の面に形成された金属層Mとの積層部分であり、かつ画素電極MITの液晶材側の面に重なる部分である重なり部50を含むソース電極SD2を有し、第2の絶縁層PAS2は、ソース電極SD2の液晶材側の面から重なり部の50端部、及び画素電極MITの一部を開口するように形成されており、ソース電極SD2の液晶材側の面から重なり部50の端部上、及び画素電極MIT上に、ソース電極SD2の液晶材側の面から重なり部50の端部、及び画素電極MITを導通させる導体膜70が形成されている。

(もっと読む)

多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法

【課題】上部配線層と下部配線層とを、微細なコンタクトホールを介して接続する多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法を提供する。

【解決手段】基板10上に形成された第1の導電層20と、層間絶縁層30と、第2の導電層70とを有し、前記層間絶縁層に形成されたコンタクトホール40を介して前記第1の導電層と前記第2の導電層とが電気的に接続された構造を有する多層配線基板において、

前記層間絶縁層は、前記コンタクトホールを含まない第1の領域50と、前記コンタクトホールを含み、該第1の領域よりも表面エネルギーが高く形成された第2の領域60とを有し、

前記第1の導電層の前記コンタクトホール内の領域は、前記第2の領域よりも表面エネルギーが高く、

前記第2の導電層は、前記層間絶縁層の前記第2の領域に接触して堆積形成され、前記コンタクトホールを介して前記第1の導電層と接続されている。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

回路基板及び表示装置

【課題】 配線の特性の劣化を生じさせることなく、額縁面積を削減することが可能な回路基板、及び、該回路基板を備える表示装置を提供することを目的とする。

【解決手段】 支持基板上にトランジスタ及び外部接続端子が載置されたトランジスタ基板と、該トランジスタ基板上に取り付けられた外付け部材とを含んで構成される回路基板であって、上記外付け部材は、導電部材を介して外部接続端子と電気的かつ物理的に接続されており、上記トランジスタは、外部接続端子と横並びに配置されている回路基板である。

(もっと読む)

回路基板の製造方法、タッチパネル、電気光学装置、電子機器

【課題】互いに交差し、絶縁膜を介して前記絶縁膜上を配線するブリッジ配線の導通不良の原因の絶縁膜のしみ上がりを防ぐ。

【解決手段】互いに交差する複数の配線と、前記複数の配線の交差部において、前記配線間に形成される絶縁層とを含む回路基板の製造方法であって、基板配線形成工程と、絶縁層を形成する絶縁層形成工程と、前記絶縁層の表面に前記基板配線に交差するブリッジ配線を形成するブリッジ配線形成工程とを含み、前記絶縁膜形成工程は、前記絶縁膜の材料を含む機能液を液滴として吐出する液滴吐出工程を含み、前記機能液はレベリング剤を含む。

(もっと読む)

電極基板の製造方法、電極基板、及び薄膜トランジスタ

【課題】製造工程の複雑化と製造コストの高価格化を招くことなく、多層電極間の接続を容易に行うことが可能な電極基板の製造方法、電極基板、及び薄膜トランジスタを提供する。

【解決手段】下地層の上に、下層電極、層間絶縁膜、上層電極がこの順番で積層され、下層電極と上層電極とが層間絶縁膜に形成された開口部を介して電気的に接続された電極基板の製造方法であって、下地層の上に、電極材料を含有する溶液を塗布した後、乾燥させて下層電極を形成する工程と、下層電極が形成された下地層の上に、開口部を有する層間絶縁膜を形成する工程と、開口部に溶液の溶媒を滴下し、開口部に位置する下層電極を溶解した後、乾燥させることにより、電極材料を開口部の内壁に沿ってコーヒーステイン形状に形成する工程と、電極材料が開口部の内壁に沿ってコーヒーステイン形状に形成された層間絶縁膜の上に上層電極を形成する工程と、を有する。

(もっと読む)

光学装置および光学装置の製造方法

【課題】より効率良く光学装置を製造できる光学装置の製造方法を提供すること。

【解決手段】 複数の光学素子1を備える光学素子シート6を、配線パターン3が形成された基板シート7に接合する工程と、上記接合する工程の後に、光学素子シート6を切断することにより、複数の光学素子1どうしを分離する工程と、上記接合する工程の後に、基板シート7を切断することにより、光学素子1と接合している配線基板を形成する工程と、を備える。

(もっと読む)

薄膜トランジスタアレイの製造方法

【課題】凹凸のあるスルーホール部分であっても、層間絶縁膜の上下の導電層間で良好な電気的な接続が得られる、版を用いた印刷法による薄膜トランジスタアレイの製造方法を提供すること。

【解決手段】版に形成された画素電極パターンのスルーホールに対向する位置に保持されたインクの量を、画素電極パターンのスルーホールに対向する位置以外の部分に保持されたインクの量よりも多くすることによって、凹凸のあるスルーホール部分であっても、層間絶縁膜の上下の導電層間で良好な電気的な接続が得られる、版を用いた印刷法による薄膜トランジスタアレイの製造方法を提供することができる。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】IGZO層とITO層とを電気的に接続する場合には、易加工性を備え電気抵抗率が低いアルミ等の金属と高融点金属としてのチタン等との積層構造を用いる必要があるが、積層構造を形成する場合、複数の金属層を形成する必要がある。そのため製造工程が増えると共に、パーティクル等の発生確率が増え、歩留まりを落とすという課題がある。

【解決手段】ITO等の金属酸化物を用いた画素電極2aが、層間絶縁層9に形成されたコンタクトホール9aを介してIGZO層を用いた配線層7aと電気的に接続している。画素電極2aとAl−Nd合金を用いた上電極6cと直接接触させた場合、コンタクト抵抗が高くなるが、配線層7aにIGZO層を用い、画素電極2aにITO等の第2金属酸化物配線層を用いた場合、互いの構造が類似していることから、密接させるだけで接触抵抗の増大を招くことなく電気的に導通を取ることが可能となる。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

1 - 20 / 79

[ Back to top ]