Fターム[5F033LL04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142) | As、B、P系 (585)

Fターム[5F033LL04]に分類される特許

161 - 180 / 585

無電解銅めっき液、無電解銅めっき方法、及び埋め込み配線の形成方法

【課題】孔の内径の大小にかかわらず、該孔の奥まで均一な無電解銅めっき層を形成しうる無電解銅めっき液および無電解銅めっき方法を提供する。また、該無電解銅めっき層を形成することにより孔の内部に信頼性の高い埋め込み配線を形成することのできる埋め込み配線の形成方法を提供する。

【解決手段】チオール基又はジスルフィド結合を有するポリエチレングリコール化合物、及び銅イオンを含有することを特徴とする無電解銅めっき液、さらに、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6を形成することを特徴とする無電解銅めっき方法、及び、該無電解銅めっき液に、孔2の形成された基板1を浸漬し、該孔の内部に無電解銅めっき層6からなる埋め込み配線を形成することを特徴とする埋め込み配線の形成方法。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

半導体基板表面を活性化するための溶液及びプロセス

【課題】半導体基板表面を活性化するための溶液及びプロセスの提供。

【解決手段】本発明は、その後の工程で無電解法により金属層を堆積させて被覆できるように、ポリマーから形成される少なくとも1つの領域を含む基板表面を活性化するための溶液及びプロセスに関する。また、本発明によれば、この組成物は、A)1以上のパラジウム錯体から形成される活性化剤と;B)少なくとも2つのグリシジル官能基及び少なくとも2つのイソシアネート官能基を含む各化合物から選択される1以上の有機化合物から形成される結合剤と;C)上記活性化剤及び上記結合剤を溶解可能な1以上の溶媒から形成される溶媒系とを含有する。用途:特に集積回路、とりわけ3次元集積回路、などの電子デバイスの製造。

(もっと読む)

有機発光表示装置及びその製造方法

【課題】酸化物半導体層と多結晶シリコン半導体層を共に用い得る有機発光表示装置及びその製造方法を提供する。

【解決手段】基板本体と、基板本体上に形成された第1ゲート電極及び第2半導体層と、第1ゲート電極及び第2半導体層の上に形成されたゲート絶縁膜と、ゲート絶縁膜を介在して第1ゲート電極及び第2半導体層上にそれぞれ形成された第1半導体層及び第2ゲート電極と、第1半導体層と少なくとも一部が相接して重畳した複数のエッチングストッパ層と、複数のエッチングストッパ層をそれぞれ露出する複数のコンタクトホールを有し、第1半導体層及び第2ゲート電極上に形成された層間絶縁膜と、層間絶縁膜上に形成され、複数のエッチングストッパ層を通じて第1半導体層とそれぞれ直接的/間接的に接続された第1ソース電極及び第1ドレイン電極と、層間絶縁膜上に形成され、第2半導体層と接続された第2ソース電極及び第2ドレイン電極とを含む。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

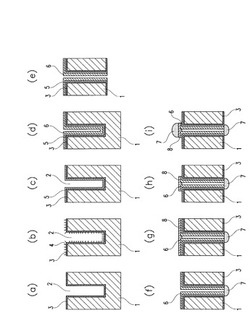

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置およびその製造方法

【課題】貫通電極を有し縦方向に積層される半導体装置であって、設計の自由度を拡大することができる半導体装置およびその製造方法を提供することを目的とする。

【解決手段】半導体基板1と、相互に離間して第1の主表面10から半導体基板1の深さ方向に向かって設けられた電極30aおよび電極30bと、電極30aおよび電極30b同士の間を結び半導体基板1を貫通することなく第1の主表面10から半導体基板1の深さ方向に向かって設けられた配線部40aとを備えている。電極30aは、半導体基板1を貫通して第2の主表面20に達する貫通電極となっている。貫通電極を有し縦方向に積層される半導体装置において、配線部40aを備えていることにより設計の自由度を拡大することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

構造体および構造体を形成する方法

【課題】 サブリソグラフィ・ピッチの構造体とリソグラフィ・ピッチの構造体との相互接続を形成する。

【解決手段】 サブリソグラフィ・ピッチを有する複数の導電線をリソグラフィでパターン形成し、複数の導電線の縦方向から45度より小さい角度の線に沿って切断することができる。代わって、ホモポリマーと混合した共重合体を陥凹エリア内に入れて自己整合し、一定幅領域内にサブリソグラフィ・ピッチを有し、台形領域で隣接線間にリソグラフィ寸法を有する複数の導電線を形成することができる。さらに代わって、サブリソグラフィ・ピッチを有する第1の複数の導電線と、リソグラフィ・ピッチを有する第2の複数の導電線は、同じレベルでまたは異なるレベルで形成することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】階段状に加工された複数層の電極層とコンタクト電極との接触抵抗を低減する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】本発明の半導体装置の製造方法は、電極層WL1〜WL4と絶縁層25とを交互に複数積層する工程と、その積層体の一部を階段状に加工すると共に各段の表面に電極層WL1〜WL4を露出させる工程と、露出された電極層WL1〜WL4に接する金属膜43を形成する工程と、電極層WL1〜WL4における少なくとも金属膜43と接する部分に金属化合物44を形成する工程と、金属膜43の未反応部を除去した後層間絶縁層46を形成する工程と、層間絶縁層46を貫通しそれぞれが対応する各段の電極層WL1〜WL4の金属化合物44に達する複数のコンタクトホール47を形成する工程と、コンタクトホール47内にコンタクト電極50を設ける工程とを備えた。

(もっと読む)

整列したナノ構造物を含む回路基板

【課題】 整列したナノ構造物を含む回路基板を提供する。

【解決手段】 回路基板は、基板と、基板に配置された極性分子層パターンおよび非極性分子層パターンと、基板に配置された第1の電極および第2の電極と、極性分子層パターンに配置され、線状ナノ構造物を含む1つ以上のチャネルとを含む。1つ以上のチャネルは、第1の電極を第2の電極に電気的に結合するのを促す。

(もっと読む)

半導体装置の製造方法

【課題】銅を用いた多層配線を有する半導体装置を高性能化する。

【解決手段】シリコン基板上に第1配線層用絶縁膜Z1を形成し、第1配線層用絶縁膜Z1に第1配線用孔部H1を形成する。その後、第1配線用孔部H1の側壁および底面を覆うようにして、タンタルまたはチタンを含む下部バリア導体膜eb1と、ルテニウムを主体とする上部バリア導体膜et1とからなる第1配線用バリア導体膜EM1を形成する。続いて、上部バリア導体膜et1をシード層として、電気めっき法により、銅を主体とする第1配線用導体膜EC1を形成し、CMP法により第1配線用導体膜EC1を第1配線用孔部H1に埋め込む。特に、上部バリア導体膜et1として、1〜5%の濃度で炭素を含ませるようにして、ルテニウムを主体とする導体膜を形成する。

(もっと読む)

配線形成方法

【課題】樹脂基板上に、接着層等を形成するための別の工程を加えることなく、基板との密着性の高い導電性配線を簡単に形成することができる配線形成方法を提供することを目的とする。

【解決手段】樹脂基板1上に、導電性微粒子を含有する分散溶液の塗布層3を形成する工程と、レーザ光6を塗布層3の特定領域に連続的に照射していくことで、導電性微細配線4を形成する工程と、導電性微細配線4以外の領域の材料を除去する工程とを備え、塗布層3の厚さをd、塗布層3の光吸収係数をα、レーザ光6の入射光強度をI0、樹脂基板1上に到達するレーザ光6の透過光強度をI1とするとき、以下の関係式から成り立つことを特徴とする。

log(I1/I0)=−αd

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

不揮発性記憶装置

【課題】第1の配線と第2の配線との交差部に整流素子と不揮発性記憶素子を有する不揮発性記憶装置で、従来に比して高さを抑えることができる不揮発性記憶装置を提供する。

【解決手段】第1の方向に延在するビット線BLと、ビット線BLとは異なる高さに形成され、第2の方向に延在するワード線WLと、ビット線BLとワード線WLとが交差する位置にビット線BLとワード線WLの間に挟持されるように配置される抵抗変化型メモリセルと、を備え、抵抗変化型メモリセルは、抵抗変化素子20がN型半導体層10とP型半導体層30で挟まれた構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】エロージョンの発生及び研磨残渣の発生がない金属からなる配線又はプラグを形成できるようにする。

【解決手段】半導体基板1上の層間絶縁膜3にコンタクトホール3aを形成する。続いて、層間絶縁膜3上に金属を含む化合物及び第1の還元性ガスを供給することにより、コンタクトホール3aを含む層間絶縁膜3の上に第1のシード層5を形成する。続いて、第1のシード層5上に金属を含む化合物及び第2の還元性ガスを供給することにより、第1のシード層5の上に第2のシード層6を形成する。続いて、第2のシード層6の上に、金属をコンタクトホール3aを埋め込むように形成する。続いて、CMP法により、層間絶縁膜3のコンタクトホール3aを除く上面に残存する金属、第2のシード層6及び第1のシード層5を除去することにより、コンタクトホール3aにプラグ7Aを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

161 - 180 / 585

[ Back to top ]