Fターム[5F033LL04]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142) | As、B、P系 (585)

Fターム[5F033LL04]に分類される特許

141 - 160 / 585

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

成膜方法、半導体装置の製造方法及び半導体装置

【課題】表面の平坦性の優れたシリコン膜を形成する成膜方法、半導体装置の製造方法及び半導体装置を提供する。

【解決手段】基体上にジシラン及びトリシランの少なくともいずれかを用いて第1温度で第1膜を形成する第1膜形成工程と、前記基体及び前記第1膜を、水素を含む雰囲気中において、前記第1温度から、前記第1温度よりも高い第2温度に向けて昇温する昇温工程と、前記昇温の後に、前記第1膜の上に、シランを用いて前記第2温度で第2膜を形成する第2膜形成工程と、を備えたことを特徴とする成膜方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜のスリミング時にその膜厚の消費を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上に複数の絶縁層25と複数の導電層WLとを交互に積層して積層体を形成する工程と、積層体上にレジスト膜50を形成する工程と、レジスト膜50をマスクにして絶縁層25及び導電層WLをプラズマエッチングする工程と、ホウ素、リン及びヒ素の少なくとも1つを含むガスを用いたプラズマ処理により、レジスト膜50の上面に、ホウ素、リン及びヒ素の少なくとも1つを含む硬化層51を形成する工程と、レジスト膜50の上面に硬化層51が形成された状態で、酸素を含むガスを用いたプラズマ処理によりレジスト膜50の平面サイズをスリミングする工程と、を備えた。

(もっと読む)

半導体装置、半導体装置の製造方法、および、リソグラフィマスクの製造方法

【課題】リソグラフィを用いて形成される半導体装置を高性能化させる。

【解決手段】互いに同じ材質からなる第1導体パターンPE1および第1ダミー導体パターンDM1を含む第1の層L1と、第2導体パターンPE2を含む第2の層L2とがシリコン基板SUB1上に積層されている。第2導体パターンPE2は、第1導体パターンPE1または第1の層L1より下層の導電部と、コンタクトプラグCP1によって電気的に接続されている。第1ダミー導体パターンDM1のうち、コンタクトプラグCP1と重なる部分には、それよりも断面積の大きい孔部HL1が形成されている。そして、コンタクトプラグCP1は孔部HL1内を通って配置されることで、第1ダミー導体パターンDM1と接触しないようにして形成されている。

(もっと読む)

半導体装置とその製造方法、及び半導体ウエハ

【課題】半導体装置とその製造方法、及び半導体ウエハにおいて、個片化後の半導体チップがもとの半導体ウエハのどこに位置していたかを容易に特定すること。

【解決手段】複数のチップ領域Rcとスクライブ領域Rsとを有するシリコン基板20と、複数のチップ領域Rcの各々に対応する複数のモニタ素子Mと、スクライブ領域Rsに形成され、複数のモニタ素子Mの各々を電気的に接続する配線2とを有し、スクライブ領域RsにおけるダイシングラインX1〜X7、Y1〜Y7の位置をずらしたときに、配線2の異なる部分がダイシングされるようにして、配線2と複数のモニタ素子Mとの結線状態をダイシングラインX1〜X7、Y1〜Y7の位置に応じて可変にした半導体ウエハWによる。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

半導体装置

【課題】本発明は、半導体基板とコンタクト部材との接触抵抗をより低減可能な半導体装置を提供する。

【解決手段】

第1の方向に延在し第1の方向と直交する第2の方向に所定の間隔で設けられた活性領域AAと、前記活性領域AAを分離する素子分離絶縁膜11とが設けられた半導体基板21aと、前記半導体基板21aの主表面上に形成された第2の層間絶縁膜24と、前記第2の層間絶縁膜24内に設けられ、前記半導体基板21a上方の配線と電気的に接続された第1の部分及び、前記第1の部分と接続され、上面視すると前記第1の部分から、はみ出した形状である第2の部分を有するコンタクト部材22とを備え、前記第1の方向における前記第2の部分最大幅は、前記第1の方向における前記第1の部分の幅よりも広く、前記第2の部分は、前記第1の部分を包囲する前記第2の層間絶縁膜24に接触していることを特徴とする半導体装置。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

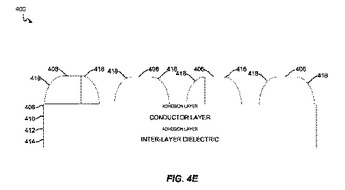

4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いたメモリ線および構造を形成する装置および方法

本発明は、4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いてメモリ線および構造を製作する装置、方法およびシステムを提供する。本発明は、基板の上方に配される第1のテンプレート層からフィーチャを形成することと、フィーチャに隣接してハーフピッチの側壁スペーサを形成することと、ハーフピッチの側壁スペーサをハードマスクとして用いることによって第2のテンプレート層内により小さいフィーチャを形成することと、より小さいフィーチャに隣接して4分の1ピッチの側壁スペーサを形成することと、4分の1ピッチの側壁スペーサをハードマスクとして用いることによって導体層から導体フィーチャを形成することとを含む。多数の追加の態様が開示される。  (もっと読む)

(もっと読む)

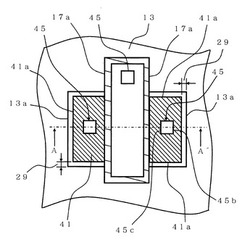

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

141 - 160 / 585

[ Back to top ]