Fターム[5F033MM19]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面形状 (637) | 台形 (227)

Fターム[5F033MM19]に分類される特許

21 - 40 / 227

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

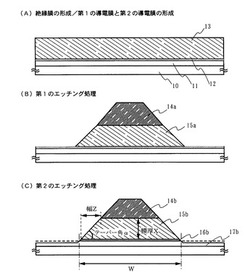

多層薄膜パターン及び表示装置の製造方法

【課題】間便に所望の形状のパターンを得ることのできる多層薄膜パターン及び表示装置の製造方法を提供すること。

【解決手段】基板上に層間絶縁膜1を形成する工程と、層間絶縁膜1上に導電性を有する第1の薄膜2を形成する工程と、第1の薄膜2上に第2の薄膜3を形成する工程と、第2の薄膜3上に、複数階調露光によって膜厚差を有するレジストパターン5を形成する工程と、膜厚差を有するレジストパターン5を介して、第2の薄膜3及び第1の薄膜2をエッチングして、レジストパターンの存在しない領域の層間絶縁膜1を露出させる工程と、膜厚差を有するレジストパターン5をアッシングして、レジストパターンの薄膜部5bを除去する工程と、薄膜部5bが除去されたレジストパターン5cを介して、第2の薄膜3をエッチングする工程と、を順次実施する。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

配線基板の製造方法、発光装置及び電子機器

【課題】多層配線構造を有する配線基板において、上層配線の断線等による歩留まりの低下を抑制し、信頼性を向上させることのできる配線基板の製造方法、発光装置及び電子機器を提供する。

【解決手段】配線基板の製造方法は、基板100上に形成されたAl−Ni合金膜102上に保護膜としてMo合金膜104を形成する工程と、Mo合金膜104上にレジスト105を形成する工程と、Al−Ni合金膜102をエッチングして、基板100側の幅がその反対側の幅よりも大きい順テーパ形状を有する信号線Ldを形成する工程と、を備える。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

配線構造及び配線構造の形成方法

【課題】配線の洗浄液への溶解を低減する配線構造の形成方法を提供する。

【解決手段】絶縁層13に犠牲配線溝21及び主配線溝31を形成し、犠牲配線溝21及び主配線溝31内にバリア層16を形成し、バリア層16が形成された犠牲配線溝21及び主配線溝31内に導電層17を埋め込んだ後に、絶縁層13上の導電層17の部分を研磨する工程と、犠牲配線溝21及び主配線溝31内の露出したバリア層16及び導電層17の表面を洗浄する工程と、を備え、研磨する工程の後における絶縁層13の平面視において、犠牲配線溝21内のバリア層16の部分の面積と導電層17の部分の面積との比S1が、主配線溝31内のバリア層16の部分の面積と導電層17の部分の面積との比S2よりも大きくなる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

液晶表示装置の製造方法

【課題】配線破断を軽減する構造を有する液晶表示装置の製造方法を提供する。

【解決手段】基板上にゲート配線及び信号配線、ゲート絶縁膜、半導体パターン、データ配線、保護膜、ドレーン電極を露出させる第1接触孔及び信号配線を露出させ、側辺の長さが幅より大きく形成される複数の第2接触孔、第1及び第2接触孔を通じてドレーン電極に連結される画素電極及び信号配線に連結される信号配線補助パッドを形成する液晶表示装置の製造方法であって、信号配線を形成する段階では、信号配線に一対一に対応する複数の信号リードを有する信号伝送用フィルムを含み、信号伝送用フィルムには複数の信号リードのうちの高電圧信号を伝送する第1信号リードと低電圧信号を伝送する第2信号リードとの間にダミーリードが形成され、ダミーリードに対応するダミー配線が基板に形成され、ダミー配線は信号配線より酸化傾向が小さい特性を有する導電物質で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。更に、その回路基板とその他のチップとを積層して、それらをボンディングワイヤで絶縁基板に支持されないリードへ接続する。

(もっと読む)

21 - 40 / 227

[ Back to top ]