Fターム[5F033NN01]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462)

Fターム[5F033NN01]の下位に属するFターム

介在層を有するもの (6,157)

深さの異なる複数のコンタクトホールの穴埋め (88)

大きさの異なるコンタクトホールの穴埋め (26)

Fターム[5F033NN01]に分類される特許

21 - 40 / 191

電子装置、電子装置の製造方法、電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる電子装置、電子装置の製造方法、電子機器を提供する。

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに半導体基板10の能動面10A側に部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】複数の半導体集積回路を接続する配線の位置を容易に決定することを課題にする。

【解決手段】第1の基板上に第1の分離層と第1の半導体素子層を形成し、第1の半導体素子層に第1のレーザビームを照射することにより第1の開口部を形成し、第1の開口部に第1の半導体素子層と接続する第1の配線を形成し、第1の半導体素子層上に第1の保護材を形成し、第1の保護材に第1の配線に接続する第1の電極を形成し、第1の分離層に沿って第1の基板と第1の半導体素子層を分離し、上述の作製工程により第2の基板上に、第2の分離層、第2の半導体素子層、第2の配線、第2の保護材、第2の電極を作製し、第2の電極と第1の配線を接続するように第2の保護材上に第1の半導体素子層を貼り合わせ、第2の分離層に沿って第2の基板と第2の半導体素子層を含む積層構造を分離する半導体装置の作製方法に関する。

(もっと読む)

集積回路のシールリング構造

【課題】

デジタル回路によるデジタル雑音結合を低減できる、改良されたIC(集積回路)チップのシールリング構造を提供する。

【解決手段】IC用のシールリング構造は、ICの周辺に沿って設けられ、少なくとも第一部分と、アナログ及び/またはRF(無線周波数)回路ブロックに対向して同アナログ及び/またはRF回路ブロックを雑音から遮蔽するように設けられる第二部分に分けられたシールリングと、第二部分の下に位置し、P型基板の中に設けられるP+領域と、P+領域を囲み、第二部分の導電壁の下で横方向に延びるSTI(シャロートレンチアイソレーション)構造とを含む。

(もっと読む)

半導体装置、半導体装置の製造方法及びパワーアンプ素子

【課題】ウェハー上面側から基板までの電流経路を低抵抗にできる半導体装置およびその製造方法を提供する。

【解決手段】第一導電型高濃度半導体基板101と、第一導電型高濃度半導体基板101上に設けられた低濃度不純物エピタキシャル層103と、105とを含み、第一導電型高濃度半導体基板101に接続するトレンチ110が低濃度不純物エピタキシャル層103、105に設けられている半導体装置であって、トレンチ110の内壁に沿って少なくとも低濃度不純物エピタキシャル層103、105中に形成されるとともに、第一導電型高濃度半導体基板101に接続する、第一導電型高濃度半導体基板101と同一導電型の第一導電型高濃度不純物領域112と、第一導電型高濃度不純物領域112上に形成されたコンタクト111とを含む、半導体装置を提供する。

(もっと読む)

高ストレス薄膜の成膜方法及び半導体集積回路装置の製造方法

【課題】プロセス条件で与えられるストレス以上に大きなストレスを薄膜に与えることが可能な高ストレス薄膜の成膜方法を提供すること。

【解決手段】水素を含む成膜原料ガスをチャンバー内に供給し、水素が取り込まれた薄膜を半導体基板上に成膜する工程(ステップ1)と、薄膜から水素を離脱させる物質を含む水素離脱ガスを前記チャンバーにパルス的に供給しながら薄膜から水素を離脱させる工程(ステップ2、ステップ11及び12)と、を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】複数枚のウエハを貼り合わせる際に、電気信号接続部に発生する損傷を効果的に防止することができ、信頼性に優れ、安定した性能の得られる半導体装置を提供する。

【解決手段】素子の形成された基板1SA,1SBからなる複数枚のウエハ1WA,1WBが貼り合わされてなり、各ウエハ1WA,1WBにおける別のウエハとの貼り合わせ面30a、30bには電気信号接続部9、26が設けられ、対向する電気信号接続部9、26同士のうちの少なくとも一方が、基板1SAが露出されている貼り合わせ面30aから突出して形成された凸状接続部であり、凸状接続部の形成されている貼り合わせ面30a上における前記電気信号接続部の配置されていない領域に、基板1SAと同じ材料からなり、半導体回路と絶縁され、貼り合わされたウエハ1WA,1WB間の間隔の寸法と同じ高さで貼り合わせ面30aから突出する補強凸部52が形成されている半導体装置とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】データ線から発生する電気力線が画素電極に進入することを防止し、開口率を大きくすることができる液晶表示装置を提供する。

【解決手段】第1基板100Aは、データ線12を覆う無機絶縁膜15と、データ線12の上方において無機絶縁膜15上に設けられた突起状の有機絶縁膜21と、有機絶縁膜21を覆い、かつ、上方から見たときにデータ線12を覆うシールド共通電極26と、を有する。

(もっと読む)

配線構造及びその形成方法

【課題】低抵抗及び高信頼性の金属配線構造を提供する。

【解決手段】配線構造は、下層配線(2)上に形成された層間絶縁膜(4)と、層間絶縁膜(4)に形成され、下層配線(2)を露出する接続口(5)と、接続口(5)の底部に形成された複数のカーボンナノチューブ(8)と、複数のカーボンナノチューブ(8)間を充填するように、接続口(5)の内部に埋設された配線金属(10、11)と、接続口(5)の上部に形成された上層配線(15)とを備える。複数のカーボンナノチューブ(8)と上層配線(15)との間には、Ti層9が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

半導体素子及びその製造方法

【課題】コンタクトプラグの形成のための平坦化工程で障壁層が損傷することを防止することができる半導体素子及びその製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、半導体基板上に複数の導電性構造物間の空間を埋め立てて上面が平坦化された絶縁膜を形成し、絶縁膜を部分的に除去して基板の一部を露出する開口を形成する。その後、開口の下部側壁及び底面に沿って形成された残留金属膜と開口の上部側壁及び残留金属膜の表面に沿って形成された金属窒化膜とを含む障壁層を形成する。障壁層を含む開口を埋め立てて金属プラグを形成する。

(もっと読む)

配線、電子装置及び電子装置の製造方法

【課題】性能劣化を抑制することが可能な高信頼性の配線を提供する。

【解決手段】第1導電膜に一端を接続し、第1導電膜と離間した第2導電膜に他端を接続する束状のカーボンナノチューブからなる複数の導電部材20と、導電部材20の間に分散されたダイヤモンド結晶構造を有する炭素粒子22とを備える。

(もっと読む)

配線、電子装置及び電子装置の製造方法

【課題】抵抗を低減することが可能な配線を提供する。

【解決手段】第1導電膜12と第1導電膜12の上層の第2導電膜26とを電気的に接続する配線24であって、第1導電膜12の上の複数の第1金属粒子16と、複数の第1金属粒子16のそれぞれを介して第1導電膜12の表面に一端を接続する複数の導電部材18と、複数の導電部材18のそれぞれの他端側の側面上の複数の第2金属粒子20と、複数の第2金属粒子20のそれぞれを介して複数の導電部材18のそれぞれの表面に一端を接続し、第2導電膜26にそれぞれ接続する複数の導電部材22とを備える。

(もっと読む)

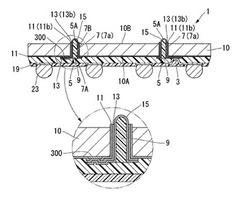

半導体装置とその製造方法および電子機器

【課題】生産効率を低下させることなく、接続信頼性の高い貫通電極を備えた半導体装置とその製造方法および電子機器を提供する。

【解決手段】基体2の能動面3上に形成された電極パッド5,6と、基体2の裏面7から電極パッド5,6に向けて形成された貫通電極8,9とが、電極パッド5,6から貫通電極8,9に向けて立設された平面視リング状のプラグ15,16を介して電気的に接続されており、貫通電極8,9の外周からプラグ15,16の表面にかけて、基体2との間に絶縁膜4a,14が連続形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ライナー膜やポーラスlow−k膜内に、十分な膜厚を有するバリアメタルを自己形成することを目的とする。

【解決手段】層間絶縁膜10内に下層配線12が形成される。層間絶縁膜10及び下層配線12上にライナー膜20と層間絶縁膜22とが順次形成される。ライナー膜20と層間絶縁膜22内にビア28と上層配線30とが形成される。下層及び上層配線12,30とビア28とは、バリアメタル14,32とCu18,36とを有している。バリアメタル14,32は、Ru膜16A,34Aと、MnOx16B,34Bとが積層されてなる。MnOx16B,34Bは、RuO2膜から供給された酸素を用いて自己形成される膜である。

(もっと読む)

処理方法および記憶媒体

【課題】良好な処理特性を維持しつつ従来よりも高スループットでシリル化処理を行うことができる処理方法を提供すること。

【解決手段】被処理基板を処理室に搬入後、SiとCH3との結合を有するガスを処理室内に導入し、被処理基板に対してシリル化処理を施す処理方法であって、処理室内にSiとCH3との結合を有するガスを供給して処理室内の圧力を上昇させ、所定圧力に到達してから処理室内の圧力を搬出圧力まで低下させるまでの間、SiとCH3との結合を有するガスの供給による前記処理室内の圧力と供給時間を、所定のシリル化処理を施すことが可能な範囲とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】動作が安定であって信頼性が良好である抵抗変化メモリ素子を備えた半導体装置を提供する。

【解決手段】電圧の印加によって抵抗値が変化する抵抗変化層41が下部電極42と上部電極43に挟まれてなる構造を有する抵抗変化メモリ素子40を備えた半導体装置であって、前記2つの電極のうちの少なくともいずれか一方の電極の前記抵抗変化層に面する側に凸部43Aが形成され、抵抗変化層41には凸部43Aに対応する凹部41Aが形成され、凹部41Aに相当する部分では抵抗変化層41(遷移金属酸化物、例えばニッケル酸化膜)の厚さが薄くなって、凹部41Aの周囲に対して大幅に抵抗値が小さくなるため、抵抗変化層41のうち、メモリの動作に実質的に寄与する面積は凸部43Aに対応した面積となる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層相互間で絶縁破壊が生じることを抑制できる半導体装置を提供する。

【解決手段】本発明に係る半導体装置において、第1配線層は、第1素子領域1aの上方に位置する第1配線11aと、第2素子領域1bの上方に位置する第2配線11dと、第2素子領域1bの上方に位置していて第2配線11dとは異なる電位になる第3配線11bを具備する。第2配線層は、第1素子領域1aの上方に位置する第4配線14aと、第3配線11bの一部の上方に位置していて第3配線11bに電気的に接続している接続用導電パターン14bを具備する。第3配線層は、第1素子領域1aの上方に位置する第5配線17aと、第2素子領域1bの上方に位置していて接続用導電パターン14bを介して第3配線11bに電気的に接続する第6配線17bを具備する。第2配線層は、第2素子領域1bの上方には配線を具備していない。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】半導体装置100は、シリコン基板の上部に形成され、所定の箇所に凹部103が設けられた層間絶縁膜101、層間絶縁膜101の内壁を覆うバリアメタル膜105、バリアメタル膜105に接して設けられるとともに凹部103の内部に埋設された下層銅配線107、および、下層銅配線107の上部に接して設けられるとともに下層銅配線107の上部の実質的に全面に設けられた保護膜115を含む。下層銅配線107の上面は、凹部103の側壁におけるバリアメタル膜105の上面より基板側に後退して設けられている。保護膜115は、構成元素としてCoまたはNiを含み、バリアメタル膜105の側壁近傍における保護膜115中のCo濃度またはNi濃度が、凹部103の中央部におけるバリアメタル膜105中のCo濃度またはNi濃度よりも高い。

(もっと読む)

半導体素子製造方法及び半導体素子製造装置

【課題】半導体素子においてコンタクト孔の深さが異なるデュアルダマシン構造を形成する場合に、配線溝の深さが不均一となる。

【解決手段】コンタクト孔60が形成された層間絶縁膜54の表面に、2層のBARC膜62,64を順次形成し、コンタクト孔60を段階的に埋め、当該表面を平坦化する。BARC膜62は、BARC材をスピンコートしベークして形成する。BARC膜62のベーク後、間断なく、BARC膜64を形成するBARC材の塗布を行う。これにより、異なる深さのコンタクト孔60-1〜60-3の上に形成されるBARC膜62,64の厚みを均等とすることができ、エッチバックにてBARC膜62,64から層間絶縁膜54の上部まで掘り下げて形成される配線溝68の深さも均等とすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 高容量のMIMキャパシタを有する半導体装置を提供することを目的とする。

【解決手段】 半導体装置内部に、第一のキャパシタ電極103と、第一のキャパシタ電極103表面に形成された薄膜かつ膜質の良好な絶縁性の窒素含有銅シリサイド膜104aを有するキャパシタ絶縁膜104と、キャパシタ絶縁膜104上に形成された第二のキャパシタ電極108により構成されるMIMキャパシタを備えることにより、半導体装置のMIMキャパシタの容量を向上する。

(もっと読む)

21 - 40 / 191

[ Back to top ]