Fターム[5F033NN03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | 積層 (371)

Fターム[5F033NN03]に分類される特許

121 - 140 / 371

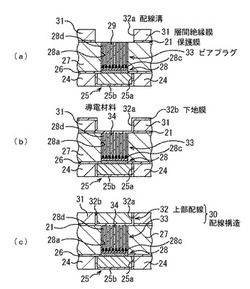

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

配線構造

【課題】断線が発生することを抑制可能な配線構造を提供する。

【解決手段】始めに、半導体装置の表面にアルミニウム金属膜5を形成する。次に半導体装置の表面に窒化チタン膜6を形成する。そして最後に半導体装置の表面にアルミニウム金属膜7を形成する。すなわち、シリコン基板1と電極4とを接続する電気配線を金属膜の3層構造により段階的に形成する。これにより、シリコン基板1と絶縁膜2との間に形成される段差の底部部分において金属膜の被覆率が低くなることによって断線が生じることを防止できる。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁信頼性の劣化を低減し、銅配線の信頼性を改善する。

【解決手段】本発明の半導体装置は、半導体基板10と、シリコン(Si)と炭素(C)と酸素(O)とを含み、半導体基板10に形成された第一の多孔質絶縁膜11a及び第二の多孔質絶縁膜11bと、第一の多孔質絶縁膜11a中に埋め込まれた第一の銅配線12aと、第二の多孔質絶縁膜11b中に、それぞれ、埋め込まれた第二の銅配線12b及び銅ビア22と、第二の銅配線12a上に形成された第一のメタルキャップ膜13aと、第二の銅配線12b上に形成された第二のメタルキャップ膜13bと、を有する。第一、第二の多孔質絶縁膜11a、11bは、少なくとも上層のC/Si比が1.5以上であり、かつ、第一、第二の多孔質絶縁膜11a、11bの少なくとも上層に含有される空孔の最大径が1.3nm以下である。

(もっと読む)

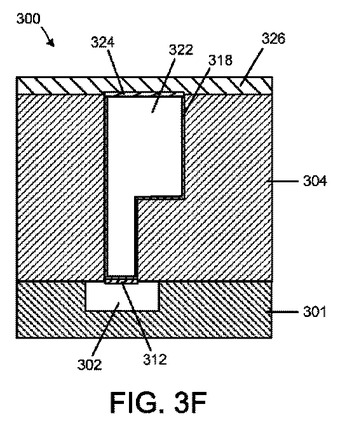

一体型ビア及びビア端子を有する半導体回路基板、並びに関連するシステム及び方法

一体型ビア及びビア端子を有する半導体回路基板と、関連のシステム及び方法とが開示されている。特定の実施例に従う代表的な方法は、半導体回路基板に非貫通ビア(140)を形成することと、ビアの側壁面に保護層(122)を塗布することと、保護層が塗布された回路基板材料の除去から保護している間に、ビアの端面から回路基板材料を選択的に除去することにより端子穴(111)を形成することと、を含む。この方法は、ビア内の導電性材料が単一である導電性端子を形成するためにビア及び端子穴の双方に導電性材料を配置することをさらに含むことができる。端子に隣接する回路基板材料は、その後、回路基板の外部の導電性構造体に接続することができる端子を露出させるために除去することができる。 (もっと読む)

半導体装置およびその製造方法

【課題】電極上に膜(水素バリア膜、バリアメタル)が形成される場合に、電極上での膜のカバレッジ不良の発生を防止することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1では、強誘電体膜13上に、強誘電体膜13に接する電極下層15とこの電極下層15上に積層される電極上層16との積層構造を有する上部電極14が積層されている。そして、電極上層16の上面は、平坦化により、強誘電体膜13の表面モホロジーと無関係な平坦面となっている。したがって、電極上層16上で水素バリア膜17およびバリアメタル28をほぼ均一な厚さに形成することができ、上部電極14上での膜のカバレッジ不良の発生を防止することができる。

(もっと読む)

ルテニウム金属キャップ層を形成する方法

ルテニウム(Ru)金属の堆積を半導体デバイスの製造に統合することで、銅(Cu)金属のエレクトロマイグレーション及びストレスマイグレーションを改善する方法が供される。本発明の実施例は、NHx(x≦3)ラジカル及びHラジカルによって、金属層及びlow-k誘電材料を含むパターニングされた基板を処理することで、前記low-k誘電材料に対する前記金属層上でのRu金属キャップ層の選択形成を改善する方法を有する。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

集積回路装置及びその製造方法

【課題】絶縁体上にもグラファイト層を容易に形成することができる集積回路装置及びその製造方法を提供する。

【解決手段】絶縁基板1上に触媒層2を形成し、その上にサポート層3を形成しておく。触媒層2としてCo層を形成し、サポート層としてTiN層を形成する。これらは、例えばスパッタリング法により形成する。次いで、アセチレンを含む原料ガスを用いて熱CVD処理を行う。この結果、触媒層2が絶縁基板1及びサポート層3に挟み込まれているが、カーボン原料はサポート層3を透過して触媒層2まで到達するので、グラファイト11が絶縁基板1と触媒層2との間に成長する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の高抵抗化を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板10の表面に設けられ、上面がほぼ同一平面をなすメモリセル部6の不純物拡散層11a及び周辺回路部7の不純物拡散層11bと、不純物拡散層11a、11bの上面を被うように形成さられた膜厚がほぼ一定の絶縁膜12、14と、絶縁膜12、14内に形成され、不純物拡散層11aと接続されたメタルプラグ13aと、絶縁膜12の内に形成され、メタルプラグ13aより短く形成され、不純物拡散層11bと接続されたメタルプラグ13bと、メタルプラグ13aの上端部と接続され、上面が絶縁膜14と面一に埋め込まれたメタル配線15aと、メタルプラグ13bの上端部と接続され、上面が絶縁膜14と面一に埋め込まれたメタル配線15bとを備えている。

(もっと読む)

高周波デバイス及びその製造方法

【課題】コンタクトの剥がれ、絶縁膜表面の段差、及び、コンタクトの両端に発生する気泡を防止し、信頼性が高く、拡散工程の短い高周波デバイスを提供する。

【解決手段】本発明の高周波デバイス200は、Si基板201上に形成された能動素子と、前記Si基板201上に積層して形成されている10GHz以上の周波数における誘電正接が0.02以下で膜厚が10μm以上の絶縁膜205と、前記絶縁膜205上に形成されている受動素子を主に形成する配線層207と、前記能動素子と前記受動素子を主に形成する配線層207とを前記絶縁膜205を介して、前記Si基板201に対して垂直方向に接続する金属であるコンタクト206とを備え、前記コンタクト206は、無電解メッキによって形成されている。

(もっと読む)

集積回路構造、そのスタック構造及びこれらの製造方法

【課題】導電性電極の連結信頼性を高めることができる集積回路構造、スタック構造及びこれらの製造方法を提供する。

【解決手段】第1面106上の少なくとも一つの導電性パッド120と、少なくとも一つの導電性パッド及び集積回路基板105を貫通する貫通ホールとを持つ集積回路基板である。少なくとも一つの導電性電極150は、貫通ホール内に前記導電性パッドを貫通して前記導電性パッド上に延び、その内部に該第2面107から露出されたボイド160aを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】簡便な方法により、マスク側壁への反応生成物の堆積を防止することができる半導体装置を製造する方法を提供する。

【解決手段】下部電極21、強誘電体、常誘電体、反強誘電体等による誘電体層22、及び上部電極23を含むキャパシタを複数備える半導体装置の製造方法は、上部電極層をパターニングして、複数の上部電極23、23’、23”を形成する工程と、複数の上部電極23、23”を被覆し、かつ最端に配置された上部電極23’の少なくとも一方側の端部を露出する第1マスクパターンを形成する工程と、第1マスクパターンを用いて、誘電体層22をパターニングする工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】より微細化が可能な半導体装置を提供する。

【解決手段】基板の表面から所定の深さまでの領域に設けられたソース電極およびドレイン電極と、これら2つの電極よりも基板内の深い位置に設けられたゲート電極とを含むMOSトランジスタが複数設けられ、複数のMOSトランジスタのソース電極またはドレイン電極と接続され、基板においてソース電極およびドレイン電極と同層または基板の表面よりも深い位置に設けられた配線を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビットコンタクトと容量コンタクトとの接触を防止する。

【解決手段】拡散層領域121,122を有するトランジスタ111と、層間絶縁膜151に埋め込まれ、それぞれ拡散層領域121,122に接続されたセルコンタクト131,141と、層間絶縁膜152に埋め込まれ、セルコンタクト131に接続されたビットコンタクト132と、層間絶縁膜153に埋め込まれ、ビットコンタクトと接続されたビット線130と、層間絶縁膜152,153に埋め込まれ、セルコンタクト141と接続された容量コンタクト142とを備える。ビット線130の側面130aは、ビット線130の延在方向に沿ったビットコンタクト132の側面132aと一致している。これにより、ビットコンタクトと容量コンタクトが直接短絡することがなくなるため、容量コンタクトの形成マージンが拡大する。

(もっと読む)

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

半導体チップ

【課題】 外部基板との熱膨張差により発生する応力を吸収し得る半導体チップを提供する。

【解決手段】 第2絶縁層236は、熱膨張率の相対的に低い絶縁膜236Aと、熱膨張率の相対的に高い絶縁膜236Bとの2層構造からなる。半導体チップ30と基板90との熱膨張率は異なり、半導体チップ30の動作時に発生する熱によって半導体チップ30と基板90との間に応力が発生するが、熱膨張率の異なる絶縁膜236A、236Bによりそれぞれ応力を吸収できる。

(もっと読む)

積層トレンチコンタクトを形成する方法および当該方法によって形成される構造

【解決手段】 マイクロ電子デバイスを形成する方法および対応して形成される構造を説明する。当該方法は、基板のソース/ドレインコンタクト上に配設されている第1のコンタクト金属と、第1のコンタクト金属の上面に配設されている第2のコンタクト金属とを含む構造を形成する段階を備えるとしてよい。第2のコンタクト金属は、基板上に配設されている金属ゲートの上面に配設されているILDの内部に配設されている。 (もっと読む)

半導体装置の製造方法

【課題】ビアホールの形成に関連する歩留まりの低下を抑制し、また、スループットを向上することができる半導体装置の製造方法を提供する。

【解決手段】絶縁性基板1上にGaN層2及びn型AlGaN層3を形成し、その後、ゲート電極4g、ソース電極4s及びドレイン電極4dを形成する。次に、ソース電極4s、GaN層2及びn型AlGaN層3に、少なくとも絶縁性基板1の表面まで到達する開口部6を形成する。次いで、開口部6内にNi層8を形成する。その後、Ni層8をエッチングストッパとするドライエッチングを高速で行うことにより、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを、冷却等によりその側壁に化合物膜19を堆積させながら形成する。そして、ビアホール1s内から絶縁性基板1の裏面にわたってビア配線16を形成する。

(もっと読む)

トランス素子が形成されている半導体装置とその製造方法

【課題】トランス素子のコイル間絶縁膜をSiO2で形成すると、形成範囲を規制するのが困難である。有機質絶縁材料を利用すれば形成範囲を自在に調整できが、厚くなってしまい、2次側コイルに生じる電圧が小さくなる。

【解決手段】半導体基板上に、下側コイル135とコイル間絶縁膜140と上側コイル154の積層構造でトランス素子155が形成されている。コイル間絶縁膜140が絶縁性無機質粒子の集積物で形成されている絶縁層141aを備えている。絶縁性無機質粒子の集積物でコイル間絶縁膜を形成すると、必要な耐圧特性を得るのに必要な厚みが薄くてすむ。従って、1次側コイル154と2次側コイル135の磁気的結合係数を高め、2次側コイル135に大きな電圧を生じさせることができる。しかも、絶縁性無機質粒子の集積物でコイル間絶縁膜を形成すると、コイル間絶縁膜の形成範囲を規制しやすい。

(もっと読む)

121 - 140 / 371

[ Back to top ]