Fターム[5F033NN03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | 積層 (371)

Fターム[5F033NN03]に分類される特許

161 - 180 / 371

スパッタターゲットの製造方法

【課題】ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止した低抵抗な配線膜を再現性よく成膜することができ、かつスパッタ時におけるダスト発生を抑制したスパッタターゲットの製造方法を提供する。

【解決手段】Y、Sc、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Th、Sr、Ti、Zr、V、Nb、Ta、Cr、Mo、W、Mn、Tc、Re、Fe、Co、Ni、Pd、Ir、Pt、Cu、Ag、Au、Cd、Si、PbおよびBから選ばれる少なくとも1種の第1の元素を0.001〜30原子%の範囲で含み、残部がAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、インゴットまたは焼結体にCを第1の元素量に対して20原子ppm〜37.8原子%の範囲で含有させ、得られたインゴットや焼結体を加工してスパッタターゲットを作製する。

(もっと読む)

半導体装置

【課題】この発明は、薄膜抵抗体を水分から保護することができる配線コンタクト構造を備えた半導体装置を提供することを目的とする。

【解決手段】半導体基板2上の薄膜抵抗体10を覆うように、中間金属層12を設ける。中間金属層12を覆うように絶縁膜14、16を積層するとともに、中間金属層12の一部を露出させるべく絶縁膜14、16に径L1のコンタクトホールを設ける。コンタクトホールを介して配線18と中間金属層12を接続し、最終的にパッシベーション膜40で配線18を覆う。中間金属層12に接する絶縁膜14は、上層に位置する絶縁膜16よりも耐湿性の高い膜にする。

(もっと読む)

半導体装置およびその製造方法

【課題】 メタルの侵入を防ぎ、コンタクトホール下部への侵入による消費電流の増大を無くした半導体装置を提供する

【解決手段】 コンタクトホール底面に低濃度不純物層をエピタキシャル成長させることでアスペクト比を小さくしコンタクトホール側壁部の窒化チタン膜のカバレッジを良くし、メタルのコンタクトホール側壁部からの高不純物ドープ活性領域への侵入を防止する。

(もっと読む)

コンタクトを一体化した集積回路システム

集積回路システム(1000)を形成するための方法は、集積回路デバイス(104)を提供するステップと、前記集積回路デバイス(104)の上に一体化コンタクト(102)を形成するステップと、を有し、該一体化コンタクト(102)を形成するステップは、前記集積回路デバイス(104)の上にビア(112)を提供するステップと、前記ビア(112)内に選択的金属(114)を形成するステップと、前記選択的金属(114)の上に少なくとも1のナノチューブ(116)を形成するステップと、前記ナノチューブ(116)の上にキャップ(118)を形成するステップと、を有する。  (もっと読む)

(もっと読む)

配線構造および半導体装置

【課題】電気を流すことができる。

【解決手段】基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14と、を有する配線構造10により、基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14とにより、筒状炭素構造体14が金属性を示す。

(もっと読む)

半導体装置およびその製造方法

【課題】 第1の導電体と第2の導電体とのショートを防止することができる半導体装置を提供する。

【解決手段】 半導体装置は、半導体基板上における複数の第1の導電体上に形成された中間絶縁膜と、中間絶縁膜に形成されかつ複数の第1の導電体上に位置する複数のコンタクトホールと、複数のコンタクトホール内にそれぞれに埋め込まれた複数のコンタクトプラグと、中間絶縁膜上の複数のコンタクトプラグそれぞれの上に形成されかつコンタクトプラグを介して複数の第1の導電体に電気的に接続された複数の第2の導電体と、を有する半導体装置であって、半導体基板には、複数の第1の導電体およびコンタクトプラグを第1の密度で有する第1の素子領域と、第1の素子領域の周囲に近接され複数の第1の導電体およびコンタクトプラグを第1の素子領域より低い第2の密度で有する第2の素子領域と、が形成されていること、第1の素子領域は、コンタクトプラグが中間絶縁膜の途中で終端して埋設された第2の素子領域に近接する最外周領域を有する。

(もっと読む)

半導体素子及びその製造方法

【課題】金属配線を電気的に連結させるビアプラグを形成する工程過程で発生する素子の信頼性を低下させる問題を解消すること。

【解決手段】半導体基板上に多数の金属配線を形成する段階;ビアホールが形成される領域の前記金属配線上に反応防止膜を形成する段階;前記反応防止膜を含む前記半導体基板上に層間絶縁膜を形成する段階;前記反応防止膜の上部の前記層間絶縁膜をエッチングしてビアホールを形成する段階;前記ビアホール内部にビアプラグを形成する段階を含む半導体素子の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】内部に貫通電極を容易に形成することができ、製造歩留を向上させることのできる半導体装置を提供する。

【解決手段】半導体シリコン層上に、導電性ポリシリコンから構成される第1コンタクトパッドを有する第1絶縁層、第2コンタクトパッドを有する第2絶縁層を形成する。この後、貫通電極用のビアホールを、少なくとも半導体シリコン層および第1コンタクトパッドを貫通して第2コンタクトパッドに到達するまで形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】工程数を増やすことなく安価にカーボンナノチューブからなる横方向の配線を提供することである。

【解決手段】半導体装置は、半導体基板または導電層(第1の導電層)101と、第2の導電層107と、触媒層106と、導電体104とを備えている。第2の導電層107は、第1の導電層101とは間隔を開けて第1の導電層101と略平行に配置されており、カーボンナノチューブからなる。触媒層106は、第2の導電層107の側面に設けられ、カーボンナノチューブを形成するための触媒を含んでいる。導電体104は、第1の導電層101に対して垂直に配置され、第1の導電層101に電気的に接続されているとともに触媒層106を介して第2の導電層107に電気的に接続されている。

(もっと読む)

ルテニウムの選択堆積を半導体デバイスの作製に統合する方法

Ruの選択堆積を半導体デバイスの作製に統合することで、Cuメタライゼーションにおけるエレクトロマイグレーションとストレスマイグレーションを改善する方法。当該方法は、熱化学気相成長法によって、Ru3(CO)12先駆体蒸気及びCOガスを有するプロセスガスを用いて、メタライゼーション層(302)上及びバルクCu(322)上にRu金属膜を選択的に堆積する工程を有する。1つ以上の選択的に堆積されたRu金属膜を有する半導体デバイスが記載されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】半導体基板101と、前記半導体基板の上方に設けられた、誘電体膜116を下部電極115と上部電極117とで挟んでなるキャパシタと、を備え、前記下部電極は、貴金属膜115aと、前記貴金属膜上に島状に複数形成された導電性酸化物膜115bと、を有する。

(もっと読む)

半導体装置、及びその製造方法

【課題】特性を低下させることなく歩留まりを向上させた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置100は、基板10と、基板10上に形成された第1絶縁層33と、第1絶縁層33を貫通して形成された株コンタクトホール34、下部コンタクトホール34の内部に第1絶縁層33の表面まで形成された第1プラグ電極35、第1プラグ電極35上の第1領域Aに形成されたキャパシタ層、第1プラグ電極35上の第1領域Aと異なる第2領域Bに形成された第2プラグ電極39を備える。キャパシタ層は、順次積層された下部電極15、強誘電体膜16、及び上部電極17を有する。第1プラグ電極35は、基板10の表面から形成されたプラグ導電層351、プラグ導電層351上から第1絶縁層33の上面まで形成され且つ下部電極15よりもエッチングに対する選択比が高いプラグバリア層352を有する。

(もっと読む)

デュアル・ストレス・ライナ・プロセスと共存できる逆テーパ・コンタクト構造

【課題】デュアル・ストレス・ライナ・プロセスと共存できる逆テーパ・コンタクト構造を提供する。

【解決手段】半導体デバイスは、シリコン層と、該シリコン層中に電気的接続領域を有するトランジスタと、該電気的接続領域上に形成されかつ該領域と電気的に接触する導電性プラグとを有し、該プラグは該シリコン層から離れると内側に傾斜する側壁を有する。

(もっと読む)

配線構造体、半導体装置および配線構造体の製造方法

【課題】製造プロセスを容易にして、特性を向上させる。

【解決手段】導電部14aと、導電部14aと対向する導電部14bと、導電部14aと導電部14bとを接続するシート状炭素構造体15aと、を有する配線構造体10により、シート状炭素構造体15aのカイラリティの制御が容易にできて、シート状炭素構造体15aの電子状態に従って、シート状炭素構造体15aにバリスティック伝導を発現させることができるようにした。これにより、理想的な抵抗を得ることができ、配線にCNTを利用した場合と、同等もしくはそれ以上の特性を実現することができる。

(もっと読む)

半導体素子のコンタクトプラグ形成方法

【課題】セル領域及び周辺回路領域のコンタクトプラグ形成工程の単純化及びコスト削減をする方法を提供する。

【解決手段】セル領域A及び周辺回路領域Bが定義され、上記周辺回路領域Bに第1のコンタクトプラグ110が形成された半導体基板100上に第1の絶縁膜108を形成する段階と、上記第1の絶縁膜をエッチングして上記セル領域Aには接合領域104が露出され、上記周辺回路領域Bでは上記第1のコンタクトプラグが露出される第2のコンタクトホールを形成する段階と、上記第2のコンタクトホール内に第2のコンタクトプラグ116を形成する段階と、上記周辺回路領域Bの上記第2のコンタクトホール内に形成された上記第2のコンタクトプラグを除去する段階と、上記第2のコンタクトホール側壁にスペーサ120を形成する段階と、上記第2のコンタクトホール内に第3のコンタクトプラグ124を形成する段階を含む。

(もっと読む)

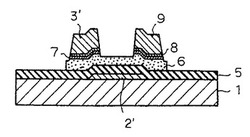

TFT基板及びその製造方法

【課題】生産性を向上させることができるTFT基板及びその製造方法を提供すること。

【解決手段】本発明にかかるTFT基板100は、ソース領域4a及びドレイン領域4bを有する半導体膜4と、ソース領域4aに電気的に接続され、透明導電膜21によってソース領域4a上に形成されるソース電極11と、ドレイン領域4bに電気的に接続され、透明導電膜21によってドレイン領域4b上に形成されるドレイン電極12と、ドレイン電極12から延在し、半導体膜4からはみ出すように形成される画素電極13と、ソース電極11に電気的に接続され、ソース電極11上において、ソース電極11からはみ出さないように、上部導電膜22によって形成された配線14とを有するものである。

(もっと読む)

半導体装置

【課題】対向配置されたウエハ間において電極部同士の接続されない部分が発生しにくい半導体装置を提供する。

【解決手段】貫通配線部9とバンプ26とが電気的に接続されることにより複数のウエハ間接続部30cが形成されて所望の半導体回路が形成されている半導体装置において、ウエハ間接続部30cが、隣接する別のウエハ間接続部30cと絶縁されたものであり、バンプ26の貼り合わせ面30bにおける平面形状が、貼り合わされるウエハ同士の位置合わせを行う際の位置合わせマージン寸法の幅で、ウエハ1WAに設けられた貫通配線部9の貼り合わせ面30aにおける面積の半分が重なり合う平面形状を取り囲んでなる位置合わせマージン形状よりも大きいものである半導体装置とする。

(もっと読む)

低コンタクト抵抗を示すMOS構造およびその形成方法

低コンタクト抵抗を示すMOS構造(100,200)と、このようなMOS構造の形成方法が提供される。一方法では、半導体基板(106)が提供され、前記半導体基板上にゲートスタック(146)が形成される。前記半導体基板内に、前記ゲートスタックと整合された不純物ドープ領域(116)が形成される。前記不純物ドープ領域から延びる隣接するコンタクトフィン(186)が形成され、前記コンタクトフィン上に金属シリサイド層(126)が形成される。前記コンタクトフィンの少なくとも1つに存在する前記金属シリサイド層の少なくとも一部に対するコンタクト(122)が形成される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】表面が平坦なバンプ電極を有する半導体装置及び半導体装置の製造方法を提供する。

【解決手段】表面に電極パッド13が形成された半導体チップ11、電極パッド13の上に配置され、半導体チップ11と対向する上面が平面をなす上部配線層17、上部配線層17の上面と同一面をなし、上部配線層17の側面と接し、半導体チップ11の表面を被うパシベーション膜15、上部配線層17及び上部配線層17の周囲のパシベーション膜15の上に配置され、上部配線層17と接続されたバンプ下地金属21、及び平面をなすバンプ下地金属21の上に側面を共有して配置され、所定の膜厚の金バンプ25とを備える。

(もっと読む)

半導体装置の製造方法および半導体記憶装置の製造方法

【課題】セルサイズを縮小することのできるSRAMを提供する。

【解決手段】駆動MISFETおよび転送MISFETの上部には、縦型MISFET

が形成されている。縦型MISFETは、下部半導体層(ドレイン)57、中間半導体層

58、上部半導体層(ソース)59を積層した四角柱状の積層体(P1、P2)と、この積層体(P1、P2)の側壁にゲート絶縁膜63を介して形成されたゲート電極66とによって構成されている。縦型MISFETは、下部半導体層57がドレインを構成し、中間半導体層58が基板(チャネル領域)を構成し、上部半導体層59がソースを構成している。下部半導体層57、中間半導体層58、上部半導体層59の夫々は、シリコン膜で構成され、下部半導体層57および上部半導体層59はp型にドープされ、p型シリコン膜で構成される。

(もっと読む)

161 - 180 / 371

[ Back to top ]