Fターム[5F033NN03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | 積層 (371)

Fターム[5F033NN03]に分類される特許

101 - 120 / 371

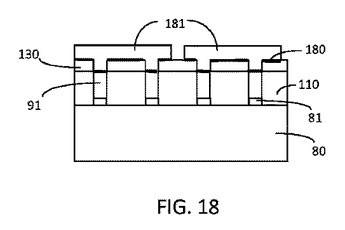

金属/有機誘電体界面でのクラックの低減

有機誘電体材料(110)中に埋め込まれた第2構造(91)への金属相互接続(181)を提供する方法であって、有機誘電体材料(110)中に埋め込まれた、例えば金属ピラー(91)のような第2構造を有する第1構造を得る工程と、少なくとも第1構造のいくつかの位置で、有機誘電体材料(110)の上に硬い層(130)を提供する工程であって、硬い層(130)は有機誘電体材料(110)の剛性より高い剛性を有する工程とを含む方法。この方法は、第1構造(91)と有機誘電体材料(110)との間の界面でクラックの無い相互接続構造を提供する。  (もっと読む)

(もっと読む)

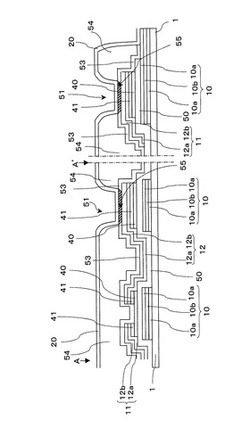

アクティブマトリクス基板およびその製造方法

【課題】従来よりも高い効率で製造することが可能な、コンタクトホールの段差部における画素電極の断線を防止したアクティブマトリクス基板およびその製造方法を提供する。

【解決手段】ゲート電極10と、ゲート電極を覆うように形成されたゲート絶縁層50と、ゲート絶縁層の上に形成された半導体層40と、半導体層と接触するように形成されたソース電極11およびドレイン電極12と、ソース電極およびドレイン電極の上に形成された第1層間絶縁層54と、第1層間絶縁層の上に形成された画素電極20と、第1層間絶縁層に形成された第1コンタクトホール51と、第1コンタクトホール内に形成された第1金属層55であって、厚さが第1コンタクトホールの深さより小さく、且つ、第1コンタクトホール内においてドレイン電極と電気的に接続された第1金属層55とを備え、画素電極は第1コンタクトホール51内で第1金属層に接触している。

(もっと読む)

フレキシブル半導体デバイスを高温で提供する方法およびそのフレキシブル半導体デバイス

いくつかの実施例は、半導体デバイスを提供する方法を含む。当該方法は、

(a)フレキシブル基板を提供する段階、(b)フレキシブル基板上に少なくとも1つの材料層を堆積させる段階であって、そのフレキシブル基板上の少なくとも1つの材料層の堆積は、少なくとも180℃の温度で生じる、段階、および(c)金属層とa−Si層との間に拡散バリアを提供する段階を含む。他の実施例も本願において開示される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 炭化珪素の半導体装置において、電極材料と、内部配線の材料とが異なるとき、これら異種金属の接触界面における不具合のおそれを無くして、長期間使用後にも高い信頼性を得ることができる、半導体装置等を提供する。

【解決手段】 炭化珪素14,18に接触する接触電極16と、該接触電極と導通する配線19とを備え、接触電極16が、チタン、アルミニウム、および珪素を含有する合金で形成され、配線19は、アルミニウムまたはアルミニウム合金で形成され、該配線は接触電極と接触することで該接触電極と導通をとることを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながら、高いドレイン電流を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたソース電極5s、ドレイン電極5d及びゲート電極5gと、が設けられている。更に、ソース電極5sとゲート電極5gとの間の化合物半導体積層構造2上に形成され、シリコンを含む第1の保護膜6と、ドレイン電極5dとゲート電極5gと間の化合物半導体積層構造2上に形成され、第1の保護膜6より多くシリコンを含む第2の保護膜7と、が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】加工マージンの大きい半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、主面を有する半導体基板と、半導体基板上に形成された第1絶縁膜と、第1絶縁膜に形成された複数のコンタクト孔と、複数のコンタクト孔内にそれぞれ形成された複数の第1コンタクトプラグと、第1絶縁膜上に形成され、該第1絶縁膜の複数の第1コンタクトプラグが形成された領域を含む所定領域を露出させる開口部を有する第2絶縁膜と、第1絶縁膜のうち開口部で露出した部分に形成され、半導体基板の主面に対して垂直方向に見て、開口部が形成されていない第1絶縁膜の上面の位置よりも低い上面の位置を有する凹部と、開口部を横切り、かつ複数の第1コンタクトプラグのそれぞれの上面に接続されるように、第1絶縁膜の凹部から第2絶縁膜の開口部を経て第2絶縁膜の上面にかけて形成された第2導電膜から成る複数の配線と、を有している。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体キャパシタの下部電極とバリアメタル膜との間の酸化膜の形成を防止する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、トランジスタTのソース/ドレイン拡散層11に接続するように形成された第1、第2のビアコンタクト23、24と、バリアメタル膜31を介して第1、第2のビアコンタクト23、24に接続された強誘電体キャパシタCとを備える。強誘電体キャパシタCは、バリアメタル膜31上に設けられた下部電極32と、強誘電体膜33と、上部電極34とを備える。下部電極32は、錐台形状の上部322と、この上部322に比べ水平方向に突出した鍔部を有する底部321とからなり、下部電極32の底部321は、バリアメタル膜31の上面を全て覆い、バリアメタル膜31の端面、鍔部の端面、及び強誘電体膜33の端面が水平方向において整合している。

(もっと読む)

デバイス及びその製造方法

【課題】微細孔の内壁と微細孔に充填した導電性物質からなる貫通電極との間で発生する隙間や拡散、酸化を抑制し、パッドと貫通電極との電気的接続の安定性を向上させることが可能なデバイスの製造方法を提供する。

【解決手段】第一基板と、該第一基板の一方の面側に配された、機能素子及び該機能素子に第一配線を介して電気的に接続されたパッドと、該パッドと電気的に接続され、前記第一基板の一方の面から他方の面に至る微細孔内に第一導電体を充填してなる貫通電極とを、少なくとも具備してなるデバイスの製造方法であって、前記第一基板の他方の面から、Deep-Reactive Ion Etching 法を用いて、前記パッドが露出するまで前記微細孔を形成する工程Aと、前記微細孔の内面の少なくとも一部に、前記第一導電体とは異なる第二導電体からなる導電部を形成する工程Bと、前記微細孔の内部に前記第一導電体を充填する工程Cと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

配線構造、及びそれを備えた液晶表示装置、並びに配線製造方法

【課題】配線を高精細化しても断線が生じ難い、信頼性の高い配線回路を実現する。

【解決手段】配線構造1は、ゲート電極17・17b・17cが配された基板9上に配される半導体層10と、ゲート電極17・17b・17c及び半導体層10が配された基板9上に配された第2層間絶縁膜13と、第2層間絶縁膜13上に配される配線18とを備え、第2層間絶縁膜13に形成されたコンタクトホール15内で、半導体層10と、配線18とが電気的に接続され、第2層間絶縁膜13は感光性樹脂材料からなり、さらに、コンタクトホール15内には導電性微粒子16が充填されており、導電性微粒子16によって、半導体層10と、配線18とが電気的に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】印加電界の履歴によって抵抗値が変化する抵抗変化層を有するスイッチ素子を多層配線中に形成し、かつ配線又は抵抗変化層の表面がダメージを受けることを抑制できるようにする。

【解決手段】この半導体装置は、第1配線層12、第2配線層16、及びスイッチビア35を備える。第1配線層12は第1配線32を有しており、第2配線層16は第2配線39を有している。スイッチビア35は、第1配線32と第2配線39を接続する。またスイッチビア35は、少なくとも底部に、抵抗変化層33を有しているスイッチ素子を有している。抵抗変化層33は、電界印加履歴に応じて抵抗値が変化する。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

ヒューズ式スルー・シリコン・ビアを有する3Dチップ・スタック

【課題】シリコン・チップ中のプログラム可能ヒューズ式スルーシリコン・ビア(TSV)を、同一のチップ中の非プログラム型TSVと併せ提供する。

【解決手段】該プログラム可能ヒューズ式TSVには、該TSV構造内に、チップ表面コンタクト・パッドに隣接するTSVの導電路の断面を限定する側壁スペーサを有する部域を用いることができる。プログラミング回路による十分な電流の印加により、金属のエレクトロマイグレーションが生じ、コンタクト・パッド中にボイド、しかしてオープン回路、が生成される。プログラミングは、多階層チップ・スタック中の2つの隣接するチップ上の相補的回路によって実行することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状構造体の形成の際のリソグラフィの合わせずれの許容度を拡大し、デバイス特性の劣化を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1層と、前記第1層の主面の上に設けられた第2層と、前記主面を貫通し、前記第1層と前記第2層とに延在する導電性の柱状構造体と、前記主面の前記第2層の側において前記柱状構造体の側壁に付設された側部と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

発光装置の作製方法

【課題】平坦性の向上により、TFTの移動度を向上させ、TFTのオフ電流を低減する

。

【解決手段】基板上に非晶質構造の半導体膜を形成する工程と、前記半導体膜上に結晶化

を促進する金属元素を添加する工程と、加熱処理を行って、前記半導体膜を結晶構造の半

導体膜とする工程と、前記結晶構造の半導体膜に第1のレーザー光を照射する工程と、前

記結晶構造の半導体膜に第2のレーザー光を照射する工程とを有する。レーザー光を照射

する工程を2回設けることにより、結晶構造の半導体膜の平坦化を向上させることができ

る。その結果、TFTの移動度を向上させ、TFTのオフ電流を低減させることができる

。

(もっと読む)

誘電ライン・バイアのエレクトロマイグレーション耐性が向上した界面層を有する相互接続構造およびその製造方法

【課題】 相互接続構造内にガウジング・フィーチャを導入することなくエレクトロマイグレーション耐性を向上させる相互接続構造を提供する。

【解決手段】 この構造は、バイア開口の底部に存在する金属界面層(または金属合金層)を含む。バイア開口は、第1の導電材料が埋め込まれた第1の誘電材料の上に位置する第2の誘電材料内に位置する。バイア開口の底部に存在する金属界面層(または金属合金層)は、第1の誘電体内に埋め込まれた下にある第1の導電材料と第2の誘電材料内に埋め込まれた第2の導電材料との間に位置する。また、エレクトロマイグレーション耐性が向上した相互接続構造を製造する方法も提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面照射型のCMOSイメージセンサにおいて、アライメントマークを微細に形成できるようにする。

【解決手段】たとえば、単位セルが形成されるSiエピタキシャル層10に、そのSiエピタキシャル層10を貫通するコンタクト孔21bを形成する。そして、その内壁を酸化させて、膜厚がほぼ均一で薄い絶縁膜21cを形成する。この絶縁膜21cを介して、コンタクト孔21b内に低抵抗ポリシリコンを埋め込んでコンタクト層21aを形成することにより、アライメントマークを兼用する裏面取り出し電極21を形成する構成となっている。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子及びその製造方法を開示する。

【解決手段】本発明は、コア/周辺回路領域でトランジスタの接合領域とメタルラインを、ビットラインを利用して連結せずメタルプラグを利用して連結することにより、コア/周辺回路領域に形成されるビットライン等もセル領域と同様に均一な形態のパターンを有することができるようにする。これを介し、本発明ではコア/周辺回路領域におけるビットラインパターニングの不良を防止し、ビットライン形成時にSPT(Spacer Pattern Technology)を適用することができる。

(もっと読む)

101 - 120 / 371

[ Back to top ]