Fターム[5F033NN03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | 積層 (371)

Fターム[5F033NN03]に分類される特許

21 - 40 / 371

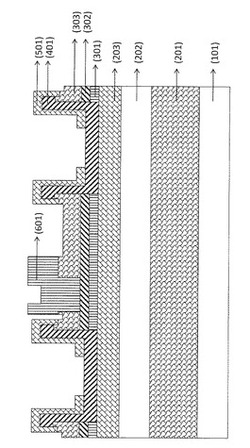

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の厚い応力緩和層を有するウェハレベルCSPと称される半導体装置において、第1電極と外部電極との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】(1)応力緩和層を半導体ウェハの上に形成する工程、(2)応力緩和層の一部を除去した開口部を形成し、半導体ウェハ上の第1電極を露出する工程、(3)第1電極と接続し、開口部を充填するポスト部を形成する工程、(4)外部電極とポスト部を接続するための再配線層を応力緩和層の上に形成する工程、(5)再配線層の上に再配線保護層を形成する工程、(6)再配線保護層の一部を除去して、外部電極を形成するための第2電極を露出する工程、(7)第2電極上に外部電極を形成する工程を含む半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20を窒素プラズマに曝露する。これにより、既存の側壁保護膜32にAlNが合わさって側壁保護膜32を分厚くすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2膜33およびSiC膜35からなる積層膜36を形成し、この積層膜36をパターニングすることによりハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、当該エッチングによりSiC膜35から解離したCを含む反応生成物を含む側壁保護膜32を、エッチング途中のAlCu膜30の側面に形成しながらAlCu配線層34をパターニングすることによって、第1AlCu配線20を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】SiCからなる第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、第2層間膜17をエッチングすることにより低段部28を形成する。このとき、第2層間膜17(SiC)からCを解離させ、その解離したCを含む反応生成物を側壁保護膜32に定着させることによって、側壁保護膜32を厚くする。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

半導体素子

【課題】熱(工程)に耐性のある配線構造を採用し、配線上の析出物の発生を抑制できる半導体素子を実現する。

【解決手段】半導体素子本体に接続する金材を含む配線パターンと、この配線パターンに一端側が接続され金材を含む接続端子と、前記半導体素子本体と前記配線パターンと前記接続端子とを覆う絶縁体と、を具備する半導体素子において、前記配線パターンあるいは接続端子の一方の面に一面が接し他面が前記絶縁体に接する面状のシリサイド体を具備したことを特徴とする半導体素子である。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 金属部材の表面に、再現性よくバリア膜を形成する技術が望まれている。

【解決手段】 基板の上に、下部バリア膜を形成する。下部バリア膜の上にシード膜を形成する。シード膜の一部の領域上に、導電部材を形成する。導電部材をエッチングマスクとして、シード膜をエッチングし、導電部材の形成されていない領域において、下部バリア膜を露出させる。下部バリア膜の表面には堆積しない条件で、導電部材の表面に選択的に上部バリア膜を成長させる。上部バリア膜をエッチングマスクとして、下部バリア膜をエッチングする。

(もっと読む)

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】一つの実施形態によれば、半導体装置は、電極、メッキ膜、半田、及びコネクタが設けられる。電極は、半導体チップ表面に設けられた第一の電極部と、第一の電極部上に設けられた絶縁膜の開口部を覆うように設けられ、第一の電極部に接続された突起状の第二の電極部とから構成される。メッキ膜は、第二の電極部上に設けられる。半田は、絶縁膜及びメッキ膜上に設けられる。コネクタは、一端の第一の構成部が半田上に設けられ、他端の第二の構造部が端子に接続され、電極と電極端子の間を接続する。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

21 - 40 / 371

[ Back to top ]