Fターム[5F033NN03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | 積層 (371)

Fターム[5F033NN03]に分類される特許

61 - 80 / 371

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

他の素子の処理の間のメモリセルの活性層の保護

【課題】メモリ構造に対して損傷を与えることを防止しながら選択された導電体から表面酸化物を適切に除去する。

【解決手段】導電層(102)を設け、その導電層(102)を覆うように誘電体(100)を設け、その誘電体(100)を貫通する第1および第2の開口(104,106)を設け、第1および第2の開口(104,106)内にそれぞれ第1および第2の導電体(108,110)を設けかつ第1および第2の導電体(108,110)を導電層(102)に接触させ、その第1の導電体(108)を覆うようにメモリ構造(126)を設け、そのメモリ構造(126)を覆うように保護要素(134)を設け、その第2の導電体(110)上に処理を施すことによる電子構造の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】余分な工程を追加することなく、コンタクト抵抗の増加を抑制する半導体装置を提供する。

【解決手段】半導体装置の製造方法では、Cu配線上の第2層間絶縁膜内に設けたコンタクトホール内に第1のTi膜、TiN膜、第2のTi膜、第1のAl膜、及び第2のAl膜をこの順に形成する。第1のTi膜を成膜する際には、コンタクトホール底面上の第1の部分と第2層間絶縁膜上の第2の部分の膜厚の比(第1の部分)/(第2の部分)を0.05以下とする。また、第2のAl膜はアルミ・リフロー法を用いて形成し、この際に第2のTi膜及び第1のAl膜をアルミニウム・チタン合金膜とする。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

光電変換装置及びその製造方法

【課題】 層間絶縁膜の厚膜化を抑制しつつ、周辺回路領域の配線層数を増加させることのできる光電変換装置を提供する。

【解決手段】 画素領域と、画素領域よりも多くの配線層を有する周辺回路領域とが配された半導体基板と、半導体基板の上部に配された配線部とを有する光電変換装置において、配線部は、第1の配線層と接続する第1の層間絶縁膜に配されたプラグを周辺回路領域に有し、第1の配線層よりも上部に配された第2の配線層と接続する第1の層間絶縁膜に配されたプラグと第2の層間絶縁膜に配されたプラグとを画素領域に有し、

半導体基板に最も近接して配された配線層は、周辺回路領域において第1の配線層であり、画素領域において第2の配線層である。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホール内のコンタクト材料としてカーボンナノチューブ(CNT)を用いつつ、ビア抵抗の低減及びプロセスの容易化をはかる。

【解決手段】配線層間のビアにCNTを用いた半導体装置であって、表面にCu配線17を有する基板上に設けられた層間絶縁膜19と、層間絶縁膜19に形成されCu配線17に接続されるビアホールと、ビアホール内に露出するCu配線17上に選択的に形成され、Cu配線17に対するバリアとなり、且つCNTの成長の助触媒となる第1の金属膜21と、ビアホール内の少なくとも第1の金属膜21上に形成された、CNTの成長の触媒となる第2の金属膜22と、第1及び第2の金属膜21,22が形成されたビアホール内に形成されたCNT23と、を備えた。

(もっと読む)

半導体装置及びその製造方法

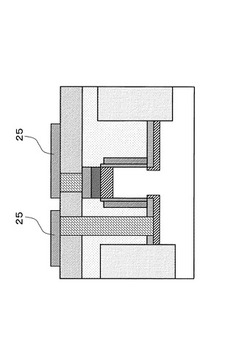

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

シリコンおよびIII−V族のモノリシック集積デバイス

【課題】シリコン基板上にIII−V族半導体で形成されたHEMTとシリコン面に形成されたショツトキーダイオードのモノリシック集積デバイスを開示する。

【解決手段】少なくとも1つのビアは、III−V族半導体を通じて延在して、III−V族トランジスタの少なくとも1つの端子をシリコン基板に形成されたシリコンデバイスに結合させる。シリコンデバイスはショットキーダイオードと、III−V族トランジスタはGaNHEMTとすることができる。ショットキーダイオードのアノードは、一実施形態においては、シリコン基板202に形成され、他の実施形態においては、シリコン基板上の低濃度にドープされたエピタキシャルシリコン層204に形成される。HEMTはGANで構成されたチヤネル層212、AlGaNで構成された電子供給層214より構成される。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体構成素子を電気接触接続するための層構造

【課題】とりわけ化学的に侵襲性の環境、および高温といったいわゆる「過酷な環境」で使用するのに適した、半導体構成素子を電気接触接続するための層構造を提供する。

【解決手段】半導体構成素子を、集積された回路素子および該回路素子のための集積端子線路と電気接触接続するための層構造であって、

i. 少なくとも1つボンディングパッド(61)が形成された少なくとも1つの貴金属層(6)を備え、該貴金属層(6)は、少なくとも1つの誘電層(3,4)によって半導体構成素子の基板(1)に対して電気絶縁されており、

ii. 前記貴金属層(6)と集積端子線路(2)との間に少なくとも1つのオーム接点(5)を備える層構造において、

前記貴金属層(6)が、前記オーム接点層(5)の上に直接施されている、ことを特徴とする層構造。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置の薄膜トランジスタ基板において、水素プラズマ処理時の水素による影響を低減する。

【解決手段】非晶質ケイ素の膜により形成された非晶質ケイ素層上に形成される銅配線において、第1添加元素として水素化物の生成エネルギーが負の元素、さらに第2添加元素を含む銅を主成分とする合金により形成された銅合金層107Aと、前記銅合金層の上に純銅により形成された純銅層107Bとを有する薄膜トランジスタ基板を備える。

(もっと読む)

導電構造物を含む半導体装置及びその製造方法

【課題】容易に抵抗を調節することができ、高集積化が可能な導電構造物を含む半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に配置され、基板の導電領域を露出させる開口部を含む絶縁膜と、開口部内に配置されるバリア膜パターンと、バリア膜パターン上に配置され、開口部の外部に延長される酸化された部分及び開口部内に位置する酸化されなかった部分を含む導電パターンと、を具備し、導電パターンの幅がバリア膜パターンの厚さによって決定される。

(もっと読む)

半導体ダイのコンタクト構造および方法

【課題】他の物体によって損傷、剥離、または亀裂を生じることなく、より粗野な処理、運送、および使用を可能にするよりよい緩衝を、半導体デバイスの金属化層に配置された低k誘電体層、ELK誘電体層、および/またはULK誘電体層の半導体ダイのコンタクトを形成するシステム、方法を提供する。

【解決手段】複数の誘電体層および導電層を含む基板101、複数の導電層の最上層115の1つと電気的に接続し、約15,000Åより大きい厚さを有する金属コンタクト105、および金属コンタクトと電気的に接続したコネクタを含む半導体デバイス。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

61 - 80 / 371

[ Back to top ]