Fターム[5F033NN03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | 積層 (371)

Fターム[5F033NN03]に分類される特許

141 - 160 / 371

導電部材の形成方法、電子デバイスの製造方法、および、電子デバイス

【課題】基板に与える損傷を抑制できる導電部材の形成方法を提供する。アンダーカットの発生を抑制できる導電部材の形成方法を提供する。

【解決手段】基板を準備する段階と、基板の少なくとも一部を覆うリフトオフ層を形成する段階と、リフトオフ層に、基板の表面の一部を露出させる第1開口部を形成する段階と、リフトオフ層と第1開口部に露出した基板の表面とを覆うシード層を形成する段階と、シード層の表面に、レジスト層を形成する段階と、レジスト層に、少なくとも一部が第1開口部と重なり、かつ、シード層の一部を露出させる第2開口部を形成する段階と、第2開口部の内部に、導電部材を形成する段階と、レジスト層の少なくとも一部を除去する段階と、リフトオフ層をリフトオフ法により除去して、レジスト層とリフトオフ層との間のシード層を除去する段階とを備える。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理後も十分に低い電気抵抗率を示し、かつ直接接続された透明画素電極とのコンタクト抵抗が十分に低減されると共に、耐食性および耐熱性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Niを0.05〜0.5原子%、Geを0.4〜1.5原子%、および希土類元素群から選ばれる少なくとも1種の元素を合計で0.05〜0.3原子%含有すると共に、NiおよびGeの合計量が1.7原子%以下である。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】単位面積あたりのインダクタンス値が従来よりも大きいインダクタを内蔵した半導体装置を実現する。

【解決手段】本発明に係る半導体装置の製造方法は、第1領域2Aと第2領域2Bに区分された半導体基板2に対して、第1の配線層によって第1のインダクタ配線と第1の回路配線とを形成する工程と、第2の配線層によって第2のインダクタ配線と第2の回路配線とを形成する工程とを、複数回にわたって繰り返すことにより、半導体基板2の第1領域2Aに積層構造をなす渦巻き状のインダクタ3を形成する。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

下向き半円筒アレイのグラフォエピタキシャル自己組織化

自己組織化ブロック共重合体を使用して、ラインアレイにおいて、サブリソグラフィーでナノスケールの微細構造を作製するための方法、ならびに、これらの方法から形成される膜およびデバイスが提供される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト歩留を向上させる、スタックドコンタクト構造を有する半導体装置を提供する。

【解決手段】NAND型フラッシュメモリのビット線コンタクトには、スタックドコンタクトを構成する第1のコンタクト開口部CH1、第2のコンタクト開口部CH2a、及び第3のコンタクト開口部CH2bが設けられる。下層の第1のコンタクト開口部CH1はビット線コンタクトの中央部に配置され、上層の第2のコンタクト開口部CH2aはビット線コンタクトの左部に配置され、その中心位置がビット線コンタクトの中心位置に対して第2のコンタクト開口部CH2aのズレ量だけ左方向に配置され、上層の第3のコンタクト開口部CH2bはビット線コンタクトの右部に配置され、その中心位置がビット線コンタクトの中心位置に対して第3のコンタクト開口部CH2bのズレ量だけ右方向に配置される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】記憶情報を高速に読み出す半導体集積回路装置の製造方法を提供する。

【解決手段】本発明の半導体集積回路装置の製造方法は、半導体基板上に第1ゲート電極を形成する工程、この工程の後に第1ゲート電極を覆うように半導体基板上に導電性膜を形成する工程、この工程の後に導電性膜の一部を覆うように半導体基板上にマスクパターンを形成する工程、この工程の後にドライエッチングを行いマスクパターンで覆われていない導電性膜をサイドスペーサ状の第2ゲート電極に加工する工程で、且つマスクパターンで覆われた導電性膜を第2ゲート電極のコンタクト領域としてパターニングする工程、この工程の後にマスクパターンを除去する工程、この工程の後に不揮発性メモリセルを覆うように半導体基板上に層間絶縁膜を形成する工程、この工程の後に層間絶縁膜中に第2ゲート電極のコンタクト領域に接続するプラグを形成する工程、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】低温シリサイド膜を使用する半導体素子において、コンタクトプラグ形成時に、CMP処理でスクラッチが発生し、隣接のプラグとの短絡が生じるのを防止する製造方法を提供する。

【解決手段】NANDフラッシュメモリのゲート電極MG、SG、PGにコバルトシリサイド膜4を設ける。これらのゲート電極の上にプラズマTEOS膜からなるシリコン酸化膜5、シリコン窒化膜7、プラズマTEOS膜からなるシリコン酸化膜9を形成し、その上面にプラズマシラン膜10を形成する。これらの絶縁膜膜を貫通してシリコン基板1の表面に達するコンタクトホールを形成し、内部に窒化チタン膜とタングステン膜を埋め込んでコンタクトプラグ11を設ける。スクラッチ耐性の高いプラズマシラン膜を設けたので、タングステン膜を成膜した後のCMP処理において、プラグに曲がりが発生せず、隣接のプラグとの短絡が生じない。

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

半導体装置及びその製造方法

【課題】アライメントマークの形成に関連する歩留まりの低下を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】GaN層2及びn型AlGaN層3に、絶縁性基板1の表面まで到達する開口部6を形成する。次に、開口部6内にソース電極4sに接続されるNi層8を導電性エッチングストッパとして形成すると共に、n型AlGaN層3上にアライメントマーク8aを形成する。次に、絶縁性基板1の裏面にフォトレジスト膜を形成し、アライメントマーク8aを基準として、ビア用遮光部及びアライメント用遮光部が設けられたフォトマスクの位置合わせを行う。次に、フォトマスクを用いてフォトレジスト膜からビアホール形成用レジストパターンを形成する。次に、ビアホール形成用レジストパターンを用いて、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを形成する。そして、ビア配線16を形成する。

(もっと読む)

半導体装置及びその製造方法

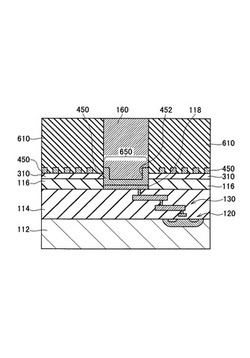

【課題】メモリセルトランジスタのコンタクト抵抗を低減する。

【解決手段】半導体装置70には、半導体基板1上に複数の絶縁ゲート型電界効果トランジスタが設けられる。絶縁ゲート型電界効果トランジスタのゲートの間に形成され、側面が側壁絶縁膜8及び絶縁膜9により絶縁ゲート型電界効果トランジスタのゲートと分離された自己整合コンタクト開口部の底部には凹部形状のポリシリコンプラグ11が設けられる。ポリシリコンプラグ11上にはバリアメタル膜12が設けられる。バリアメタル膜12上には、自己整合コンタクト開口部を覆うように金属プラグ13が埋設される。

(もっと読む)

半導体装置及びその製造方法

【課題】製造が容易であり、貫通金属と半田との接合強度が大きい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明は、基板12と、基板12を貫通し、基板12の表面に設けられた電極部16に接し、基板12の裏面側から凹部30が設けられている貫通金属32と、凹部30に埋め込まれるように、基板12裏面側の貫通金属32の露出面に設けられた半田34からなる導電材と、を具備する半導体装置及びその製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】レジストマスクを用いたフォトリソ工程を追加することなく、微細な容量コンタクトプラグ上部の面積を拡大させることが可能なCOB型DRAMの製造方法を提供する。

【解決手段】製造方法は、層間膜8にコンタクトホールを形成後、コンタクトホールに第一の導電材料を埋め込みエッチバックして、第一のコンタクトプラグ10を形成する工程、層間膜8をエッチングして第一のコンタクトプラグ10上部を露出させる工程、及び、層間膜8及び第一のコンタクトプラグ10上に第二の導電材料を成膜しエッチバックして、自己整合的に第一のコンタクトプラグ10上部周囲に第二の導電材料11を残すことで、プラグ10上部を拡大した第二のコンタクトプラグを形成する工程、とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ビット線間の間隔が狭くなった場合の配線間ショートに対するマージンや耐圧を確保する。

【解決手段】隣接配置される選択ゲートトランジスタのコンタクトプラグを、第1および第2のコンタクトプラグ4、5として交互に配置した構成とし、配線層を2層にして下層側を第1の配線層6、上層を第2の配線層7として形成する。第1のコンタクトプラグ4を第1の配線層6にヴィアプラグ13を介して接続し、第2のコンタクトプラグ5をヴィアプラグ13、16を介して第2の配線層7に接続する構成とする。第1の配線層6、第2の配線層7が共にコンタクトプラグのピッチの倍のピッチで配置できる。ショート不良、耐圧不良、リーク不良、配線間容量の増大を防止できる。

(もっと読む)

相互接続構造のための貴金属キャップおよびこれを形成する方法(相互接続構造のための貴金属キャップ)

【課題】 誘電率が約3.0以下の誘電材料(52)を含む相互接続構造を提供する。

【解決手段】 この低k誘電材料は、上面が埋め込まれた少なくとも1つの導電材料(60)を有する。また、誘電材料は、貴金属キャップ(62)の形成前に疎水性とされた表面層(52B)を有する。貴金属キャップは、少なくとも1つの導電材料の上面上に直接に配置されている。誘電材料上に疎水性表面層が存在するために、貴金属キャップは、少なくとも1つの導電材料に隣接した誘電材料の疎水性表面層上に実質的に延出せず、この疎水性の誘電表面上に貴金属キャップ堆積からの貴金属残留物は存在しない。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】窒化物半導体装置において、半絶縁性SiC基板と比較して安価に入手することができる導電性SiC基板を使用してコストを低く抑えながら、良好な出力特性及び高周波特性が得られるようにする。

【解決手段】窒化物半導体装置を、導電性SiC基板1上に形成された窒化物半導体積層構造2と、窒化物半導体積層構造2の活性領域の下方の領域に形成されたアモルファスカーボン層3とを備えるものとする。

(もっと読む)

半導体のマイクロパッド形成

第1の半導体素子(12,52,74)の外部コンタクト(14,54,78)に達するマイクロパッド(30,70,42)を形成する方法である。銅から成るスタッド(20,24,66,88,82)を外部コンタクトの上に形成する。スタッドは、第1の半導体素子の表面上を延在する。銅から成るスタッドを錫溶液に浸漬する。錫(28)で、スタッドの銅の少なくとも95パーセントを、好ましくは99パーセント超を置換する。結果として、5重量パーセント未満の銅を含む錫マイクロパッドが得られる。マイクロパッドがほぼ純粋な錫であるので、金属間化合物ボンドは、第1の半導体素子のマイクロパッドがボンディングされない状態が続いている間は形成されない。より小さいマイクロパッド寸法が、金属間化合物ボンドが形成されないので得られる。第1の半導体素子を、当該第1の半導体素子に覆い被さる第2の半導体素子にボンディングする場合、ボンド寸法によって、積層チップの高さが極めて高くなることはない。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ビット線コンタクトの接続不良や高抵抗不良等の発生を防止する。

【解決手段】本発明の半導体装置は、半導体基板1上に不揮発性のメモリセルを行列状に配置したメモリセルアレイを備え、各メモリセルにおけるビット線コンタクトCBを1つおきにビット線方向にずらして2列に配置するように構成し、ビット線コンタクトCBを、活性領域3に下端を接続する下部コンタクトプラグ7と、下部コンタクトプラグ7に縦積みされビット線BLに上端を接続する上部コンタクトプラグ5とから構成し、更に、上部コンタクトプラグ5を、ビット線BLに接続される第1のプラグ部5aと、この第1のプラグ部5aの上端の内径寸法より内径寸法が大きな大径部を有し、下部コンタクトプラグ7に接続された第2のプラグ部5bとから構成した。

(もっと読む)

半導体装置

【課題】良好な特性を得ながら、小型化、高耐圧化および低消費電力化が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、シリコンよりも大きいバンドギャップを有し、パワートランジスタ2が形成されたSiC層11と、SiC層11の主表面11aよりも上側の所定領域に形成されるとともに、制御回路用のNMOSトランジスタ3およびPMOSトランジスタ4が形成され、SiC層11とは別の層からなるシリコン層21と、SiC層11のパワートランジスタ2とシリコン層21のNMOSトランジスタ3およびPMOSトランジスタ4とを接続するAl配線5とを備える。

(もっと読む)

141 - 160 / 371

[ Back to top ]