Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,441 - 2,460 / 2,805

半導体装置及びその製造方法

【課題】 隣接するゲート電極を狭ピッチで配置できる上、埋め込みによりシリコン基板面上での微細化を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】 シリコン半導体基板1上に形成された隣り合うトランジスタのゲート電極と、トランジスタ間に金属層を埋め込んでなり、各ゲート電極9,10の端部がゲート絶縁膜8を介して金属層の端面に重なるように配置された埋め込み金属層7と、各ゲート電極の他端部側に形成されたLDD領域16,17とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】エレクトロマイグレーション耐性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】第1金属配線8上の層間絶縁膜10に、第1金属配線8に達する接続孔10aおよび配線溝10bを形成する。第1金属配線8上に予めキャップ層9aを形成していたとしても、接続孔10aの形成の際に、接続孔10a内のキャップ層9aの一部あるいは全部が除去されてしまう。本発明では、接続孔10aを形成後に、接続孔10aの底部のみに選択的にキャップ層9bを形成する。キャップ層9bの形成後に、接続孔10aおよび配線溝10b内にバリアメタル層17および金属層18を埋め込んで、コンタクト19および第2金属配線20を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 トランジスタを形成する際に、そのトランジスタの下方に形成されている膜が受ける熱的ダメージを低減することができる半導体装置とその製造方法を提供すること。

【解決手段】 第1絶縁膜37の上に遮蔽膜38を形成する工程と、遮蔽膜38の上に第2絶縁膜39と非晶質半導体膜40とを順に形成する工程と、非晶質半導体膜40にエネルギービームを照射し、少なくとも薄膜トランジスタのチャネルとなる部分の非晶質半導体膜40を溶融して多結晶半導体膜41にする工程と、上記チャネルの上の多結晶半導体膜41上にゲート絶縁膜43aとゲート電極44aとを順に形成する工程と、ゲート電極44aの横の多結晶半導体膜41にソース/ドレイン領域41aを形成し、該ソース/ドレイン領域41a、ゲート絶縁膜43a、及びゲート電極44aでTFT60を構成する工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高速動作が可能なLDD型MISFETと、かつ高電圧駆動が可能なLDD型MISFETとを内蔵する半導体集積回路装置を低コストで実現する。

【解決手段】高速動作が可能なMISFETは、ゲートサイドウオール層に自己整合された高濃度領域に金属シリサイド層を有し、高電圧駆動が可能なMISFETは、上記ゲートサイドウオール層の幅よりも大きい幅を有するLDD部を有し、そのLDD部に接して高濃度領域を有し、そしてその高濃度領域に金属シリサイド層を有する。

(もっと読む)

電解研磨および電気メッキ方法

【課題】金属層を被着させ除去するための新しい処理技術を提供する。

【解決手段】本発明の一態様においては、ウェハ上に導電性フィルムを電気メッキするための方法例が提供されている。該方法は、第1の密度の凹部領域上で平面となる前に第1の電流密度範囲内で凹部領域および非凹部領域を有する半導体構造上に電気メッキする工程および金属フィルムを金属層が凹部領域上で平面となった後に第2の電流密度範囲内で電気メッキする工程を含む。第2の電流密度範囲は、第1の電流密度範囲よりも大きい。1つの例においては、該方法は更に、金属層が第2の密度の凹部領域上で平面となるまで第2の電流密度範囲内で電気メッキする工程およびその後第3の電流密度範囲内で電気メッキする工程を包含し、ここで第2の密度は第1の密度よりも大きい。

(もっと読む)

パターン形成方法及び半導体装置の製造方法

パターン形成方法は、流動性を有する物質よりなる流動性膜を形成する工程と、押圧面に凹部及び凸部のうち少なくとも一方を有する押圧部材の押圧面を流動性膜に押圧して、凹部及び凸部のうち少なくとも一方を流動性膜に転写する工程と、押圧面を流動性膜に押圧した状態で流動性膜を第1の温度に加熱して、凹部及び凸部のうち少なくとも一方が転写されている流動性膜を固化することにより、固化膜を形成する工程と、固化膜を第1の温度よりも高い第2の温度に加熱して、固化膜を焼成することにより、焼成された固化膜よりなるパターンを形成する工程とを備える。  (もっと読む)

(もっと読む)

1ないし5nmの厚さの金属キャップを用いる改良されたオンチップCu相互接続

【課題】 1から5nmの厚さの金属キャップを用いた改良されたオンチップCu相互接続を提供する。

【解決手段】 開示されているのは、層間の誘電体又は誘電体拡散障壁層の堆積に先立って、1から5nmの厚さの元素でCuダマシン配線の表面をコーティングする手順である。そのコーティングは、酸化に対する防御をもたらし、Cuと誘電体の間の密着力を増し、そしてCuの界面拡散を減少させる。さらに、その薄いキャップ層はCuのエレクトロマイグレーション寿命を増し、応力により誘起されたボイド発生を減らす。選択された元素は、Cu配線間のショートを引き起こすことなしに、下層の誘電体中に埋込まれたCuの上に直接堆積することができる。これらの選ばれた元素は、酸素及び水に関する負の高い還元電位と、Cuへの低い溶解度、及びCuとの化合物形成に基づいて選ばれている。

(もっと読む)

半導体装置及びその形成方法

【課題】Cuの拡散から生じるリーク電流の発生を低減し、オーバーハングを抑制することを目的とする。

【解決手段】半導体基板(図示せず)上に形成された下層配線101に絶縁性バリア膜102及び層間絶縁膜103を順次形成する。次に、層間絶縁膜103を除去して絶縁性バリア膜102に到達するビア104及びビア104に到達するトレンチ105を形成する。次に、層間絶縁膜103の露出している部分に改質層200を形成した後、改質層200を除去し、丸み105b、丸み105a及び丸み104aを形成する。次に、ビア104の底面の絶縁性バリア膜102を除去する。次に、ビア104及びトレンチ105にバリアメタル膜106を堆積し、リスパッタを行う。次に、バリアメタル膜106上にCu膜107を堆積し、Cu膜107及びバリアメタル膜106を研磨してビアプラグ108及び上層配線109を形成する。

(もっと読む)

表面被覆方法、及び該方法を使用するマイクロエレクトロニクス相互接続の作製、並びに集積回路

本発明は、基板の表面を、金属材料から作られる核生成フィルムで被覆する方法に関し、前記表面は、導電性又は半導電性表面であり、凹部及び/又は凸部を含む。 本発明方法は、有機フィルムを表面上に蒸着する工程であって、前記フィルムの厚さが、その自由面が、導電性又は半導電性表面(その上に、フィルムが蒸着されている)の凹部及び/又は凸部に共形的にならうものから成る工程;金属材料の前駆体を、表面上に蒸着した有機フィルムに挿入する工程であって、前記表面上に有機フィルムを蒸着させることから成る工程と同時の又はその後に続く工程;及び金属材料の前駆体を金属材料に変換する工程にある。 本発明方法は、集積回路、超小型電子相互接続及びマイクロシステムの製造のために使用することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】ストレスマイグレーションによる動作不良を抑制すること。

【解決手段】第1の層間絶縁膜13に形成された配線溝に第1のバリアメタル層14とCuを主とする配線材15が埋め込まれて下層配線16が形成されている。第1の層間絶縁膜13及び下層配線16上に絶縁膜17,18が形成されている。絶縁膜17,18に形成されたホール内に第2のバリアメタル層20とCuを主とするプラグ材21が埋め込まれてヴィアプラグ22a,及びスリット状ダミープラグ22bが形成されている。スリット状ダミープラグ22bは上層配線26aに接続しない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】白金族金属、白金族合金または白金族金属の導電性酸化物を主成分とする膜を電極材料に用いた容量素子を有するDRAMの微細化を推進する。

【解決手段】酸化シリコン膜43に溝44を形成した後、あらかじめ酸化シリコン膜43の下層に形成しておいた導電性下地膜42をカソード電極とする電解メッキ法によって、溝44の内部にPt膜45を形成する。その後、酸化シリコン膜43をエッチングで除去した後、Pt膜45をマスクにして導電性下地膜42をドライエッチングすることにより、Pt膜45とその下部に残った導電性下地膜42とで容量素子の下部電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 配線材料であるAlと電極材料であるPtとの反応を効果的に抑制することができる、金属酸化物誘電体を用いたキャパシタを備える半導体装置の製造方法を提供する。

【解決手段】 金属酸化物誘電体を容量絶縁膜に用いるキャパシタを備える半導体装置の製造方法であって、半導体基板の上方に第1絶縁膜を介して第1電極6及び容量絶縁膜7を形成する工程と、第1絶縁膜上に第2絶縁膜9を形成する工程と、容量絶縁膜7の上面を露出する工程と、酸素雰囲気中で熱処理する工程と、容量絶縁膜7の上面に第1導電膜10aと第2導電膜10b,10cとの積層膜からなる第2電極10を形成する工程と、第2絶縁膜9上に第3絶縁膜13を形成する工程と、第3絶縁膜に第2電極の一部を露出する開口部14を形成する工程と、開口部14内を覆うように第3導電膜15を形成する工程と、第3導電膜15上に配線層16を形成する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

半導体装置の製造方法は、基板の上に流動性を有する絶縁性物質よりなる流動性膜を形成する工程と、押圧部材の平坦な押圧面を前記流動性膜に押圧して流動性膜の表面を平坦化する工程と、押圧面を流動性膜に押圧した状態で流動性膜を第1の温度に加熱して表面が平坦化されている流動性膜を固化することにより、表面が平坦な固化膜を形成する工程と、表面が平坦な固化膜を前記第1の温度よりも高い第2の温度に加熱して固化膜を焼成することにより、表面が平坦な焼成膜を形成する工程とを備え

ている。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法

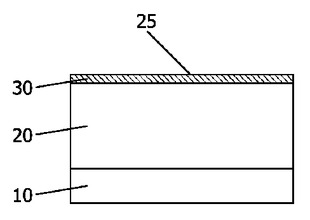

本発明は、半導体デバイスの製造方法に関するものである。この方法では、半導体デバイスは、基板(10)を具え、この基板(10)は、表面(25)を有する低−kの前駆物質層(20)で覆われている。この工程の後、部分硬化工程が行われ、前記低−kの前駆物質層(20)の表面(25)またはその近くに緻密層(30)が形成される。この緻密層(30)は、保護層(30)として作用することができる。前記低−kの前駆物質層(20)は、未硬化、または部分的に硬化された状態で適用できる特性を有する材料の群から選択される。この方法の主な利点は、前記緻密層(30)が、前記低−kの前駆物質層(20)自体から形成されるため、別個の保護層(30)を低−kの前駆物質層(20)に設ける必要がない点である。したがって、前記緻密層(30)は、前記低−kの前駆物質層(20)に対して良好な接着性を有する。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

ルテニウム層堆積装置及び方法

本発明の実施形態は、四酸化ルテニウム含有ガスから基板表面上にルテニウム含有層を形成するための装置及び方法を提供する。一般に、方法には、基板表面を四酸化ルテニウム蒸気にさらして、基板表面上に触媒層を形成するステップと、続いて基板表面上のデバイス構造を少なくとも1つの堆積プロセスによって充填するステップとが含まれる。一実施形態において、ルテニウム含有層は、外部容器内で四酸化ルテニウムを生成し、その後、生成した四酸化ルテニウムガスを処理チャンバ内に位置する温度制御された基板表面に分配することによって基板表面上に形成される。他の実施形態において、ルテニウム含有層が四酸化ルテニウム含有溶媒を用いて、基板表面上に形成される。他の実施形態において、溶媒は四酸化ルテニウム含有溶媒から分離され、残りの四酸化ルテニウムは基板表面上にルテニウム含有層を形成するために用いられる。 (もっと読む)

表面疎水化方法、ならびに半導体装置およびその製造方法

【課題】その後の加工プロセスとの整合性を有し、絶縁層の表面をより簡便にかつ効率良く疎水化することができ、かつ、絶縁層のより深い領域を疎水化することができる表面疎水化方法、ならびに半導体装置およびその製造方法を提供する。

【解決手段】絶縁層20を加熱により活性化する工程と、(A)反応性シラン化合物および(B)有機溶媒を含む表面疎水化用組成物を前記絶縁層の表面に接触させる工程とにより、前記絶縁層の表面に疎水性膜を形成する疎水化処理方法および前記疎水性膜を含む半導体装置。

(もっと読む)

半導体装置の製造方法

半導体装置の製造方法は、押圧面に凸部を有する押圧部材の押圧面を流動性膜に押圧して、流動性膜に凸部が転写されてなる第1の凹部を形成する。次に、押圧面を流動性膜に押圧した状態で流動性膜を第1の温度に加熱して流動性膜を固化して、第1の凹部を有する固化膜を形成する。次に、固化膜を第1の温度よりも高い第2の温度に加熱して固化膜を焼成して、第1の凹部を有する焼成膜を形成する。次に、焼成膜の上に、第2の凹部形成用の開口部を有するマスクを形成した後、焼成膜に対してマスクを用いてエッチングして、焼成膜に少なくとも第1の凹部と連通する第2の凹部を形成する。焼成膜の第1の凹部及び第2の凹部に金属材料を埋め込んで、金属材料よりなるプラグ及び金属配線を形成する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】簡易な方法により、導電体を確実に充填して貫通電極を形成することができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、開口部18aを有する支持体18を基板10表面側に取り付ける工程、基板10をその裏面側から薄化する工程、基板裏面に第1絶縁膜19を形成する工程、支持体18の開口部18aに繋がる貫通孔13を基板10に形成する工程、第2絶縁膜14を基板10の貫通口13内部に形成する工程及び基板10の貫通孔13内部に導電体16を充填する工程を備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】窒化膜5のエッチング時に、広ゲートピッチP1間において、拡散層4が損傷を受けることがあった。

【解決手段】はじめにシリコン基板1上に隣り合って複数の拡散層4、ゲート2およびサイドウォール3を形成する。次いで拡散層4、ゲート2およびサイドウォール3上に、表面がゲート2の上端よりも高い位置にあり、かつ、狭ゲートピッチP間の間隙の全体に充填されるように窒化膜5を積層する。つづいて窒化膜5上の表面を平坦化した後、窒化膜6上に酸化絶縁膜6を積層する。その後、コンタクト孔7を形成し、その内部に接続プラグ8を形成する。

(もっと読む)

2,441 - 2,460 / 2,805

[ Back to top ]