Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,241 - 2,260 / 2,805

半導体装置の製造方法

【課題】微細なメタル配線およびヴィアホールを寸法バラツキなく形成して、寸法バラツキが低減された半導体装置を製造する方法を提供する。

【解決手段】半導体基板10上に第一のメタル配線を形成する工程、前記第一のメタル配線上に無機絶縁膜14を形成する工程、前記無機絶縁膜上に有機絶縁膜15を形成する工程、前記有機絶縁膜に凹部を形成する工程、前記凹部が設けられた有機絶縁膜上に、加熱により有機絶縁膜と反応する上層膜を形成する工程、前記上層膜を加熱処理して前記上層膜を前記有機絶縁膜と反応させ、前記凹部の側面に反応層25を成長させる工程、および、未反応の上層膜を除去し、反応層が成長したことにより縮小した凹部26を得る工程を具備することを特徴とする。

(もっと読む)

半導体基板上に形成される高精度高周波数キャパシタ

【課題】高周波数用高精度キャパシタを提供すること。

【解決手段】高精度高周波数キャパシタは半導体基板102の表側に形成された誘電層104を有し、第一の電極106が誘電層上に形成される。半導体基板は高度にドープされ、それゆえ抵抗率が低い。第二の電極108は第一の電極106より絶縁され、また表側表面上に形成される。一つの実施例では、第二の電極108は金属を満たしたビア116によって裏面の導電層120と電気的に接続される。他の実施例ではビアは省略され、第二の電極は基板と電気的に接続されているか、誘電層上に形成されるかのどちらかであり、一対の連続して接続されたキャパシタを作り出す。

(もっと読む)

線路デバイスの製造方法

【課題】ストレスリリーフと接触窓構造の間隔距離の微小化を可能にする線路デバイス構造の製作過程及びその構造を提供する。

【解決手段】基板と、第一金属柱体68と、第二金属柱体と、を備え、第一金属柱体68は、基板上に位置し、第一金属柱体68の最大横寸法Hwを第一金属柱体68の高度Htで割ると4より小さく、かつ第一金属柱体68の高度が20μmから300μmの間であって、第二金属柱体は、基板上に位置し、第二金属柱体の最大横寸法を第二金属柱体の高度で割ると4より小さく、かつ第一金属柱体の中心点から第二金属柱体の中心点までの距離Hbが10μmから250μmの間である。

(もっと読む)

半導体装置、及びそれを用いた送受信装置、並びにその半導体装置の製造方法

【課題】 容量素子の占有面積を低減させながら、容量素子の寄生容量を低減できる技術を提供する。

【解決手段】 下部電極10、容量絶縁膜18および中間電極11よりなる容量素子上に、中間電極11、容量絶縁膜21および上部電極12よりなる容量素子を形成する。すなわち、容量素子を積層構造とする。そして、中間電極11に段差を設けることにより、容量形成領域以外の領域における中間電極11と下部電極10との間の距離および中間電極11と上部電極12との間の距離を容量形成領域における距離より大きくする。例えば、容量形成領域では、下部電極10と容量絶縁膜18が直接接するようにする一方、容量形成領域以外の領域では、下部電極10と容量絶縁膜18が直接接しないようにする。

(もっと読む)

ナノ・スケール・チャネルトランジスタのためのブロックコンタクトアーキテクチャ

ナノスケールチャネルデバイスのコンタクトアーキテクチャは、複数の並列半導体本体を有するデバイスのソースまたはドレイン領域に結合されかつその間に延びるコンタクト構造を有する。コンタクト構造は、サブリソグラフィックピッチを有する並列半導体本体と接触することができる。 (もっと読む)

半導体装置の製造方法

【目的】 基板上の膜に対し、膜の膜剥れやスクラッチを防止する半導体装置の製造方法を提供することを目的とする。また、露光装置におけるステージ上での基板のチャックエラーを抑制することを別の目的とする。

【構成】 基板200の表面にCu膜260を形成するめっき工程(S120)と、前記基板200の裏面を研磨する裏面研磨工程(S122)と、前記裏面が研磨された後、前記基板200の表面に形成された前記Cu膜260を研磨する表面研磨工程(S124)と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ダマシン法を用いて形成された銅配線の絶縁破壊耐性(信頼性)を向上する。

【解決手段】シリコン酸化膜39の配線溝40に埋め込むCu配線46a〜46eをCMPを用いた研磨で形成する。それから、CMP後の洗浄工程を経た後に、シリコン酸化膜39およびCu配線46a〜46eの表面を還元性プラズマ(アンモニアプラズマ)で処理する。その後、真空破壊することなく、連続的にキャップ膜(シリコン窒化膜47)を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 銅イオンの拡散防止機能を持つ低誘電率の層間絶縁膜の成膜初期における銅配線からの銅イオンの拡散を防止する。

【解決手段】 半導体装置の製造方法は、基板上の絶縁膜(1)に形成された銅配線(3b)における露出部位に、窒素を含む層(4a)を形成する。その後、シロキサン(Si−O−Si)結合を有する有機シリコン化合物を原料として用いて、プラズマCVD法により、窒素を含む層(4a)の上に層間絶縁膜(5)を形成する。

(もっと読む)

電子部品とその製造方法

【課題】高信頼性の電子部品の製造方法と、互いに接近した配置が可能な電子部品を提供する。

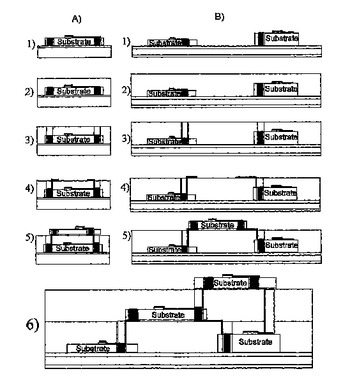

【解決手段】半導体基板(10、10′)に回路を形成するためのCMOS構造(20、20′)を形成し、CMOS構造(20、20′)の形成後、低温処理、特に450℃以下の温度での処理で、半導体基板(10、10′)の第1面(S1)とそれとは反対側の第2面(S2)との間で回路の接続を行うべく、半導体基板(10、10′)の開口内に少なくとも1つの電気導体(30、30′)を形成する。この電子部品は電子回路及びセンサ(80、80′)の狭小な配置を可能とし、特に医療機器用として適する。

(もっと読む)

線路デバイスの製造方法

【課題】小型化が図られる線路デバイスの製造方法を提供する。

【解決手段】基板の上に第一金属柱及び第二金属柱を設置する。第一金属柱の最大幅は、第一金属柱及び第二金属柱の高さで割ると4より小さい。また、第一金属柱の高さは、20μmから300μmであって、かつ第一金属柱の中心点から第二金属柱の中心点までの距離は10μmから250μmである。これにより、金属柱体間の距離を250μm以下に縮小することが可能であって、かつピンホール数を400個以下の目標に抑えることも達成できる。またICの性能を有効に改善し、かつ低電源ICエレメントのIC金属接続線路の抵抗及び負荷を大幅に下げることが可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】 MISFETを有する半導体装置の性能を向上させる。

【解決手段】 半導体基板1のp型ウエル7上にゲート絶縁膜8を介してゲート電極15が形成され、p型ウエル7にはソース・ドレインとしてのn+型半導体領域35が形成されている。ゲート電極15の両側壁上にはオフセットスペーサ23を介してサイドウォールスペーサ33が形成され、サイドウォールスペーサ33の側面34aには凹部34bが形成されている。ゲート電極15上およびn+型半導体領域35上に金属シリサイド膜43a,43bが形成され、金属シリサイド膜43aはゲート電極15の上面上だけでなく、サイドウォールスペーサ33の側面34aうちの凹部34bよりも上部の領域上にも延在している。金属シリサイド膜43bは、n+型半導体領域35の上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネル形成領域に異なる応力を発声させる膜を互いに積層形成した半導体装置において、当該膜のエッジ部形状に起因するボイドが形成された場合であっても、隣り合うコンタクトがショートすることがない半導体装置及びその製造方法を提供する。

【解決手段】 コンタクト開口部を形成した後に絶縁材料を堆積して、コンタクト開口部に表出したボイド開口部を塞ぐ。これにより、当該ボイドに導電性材料が侵入することを防止し、隣り合うコンタクトがショートすることを防止する。

(もっと読む)

半導体素子における銅の層剥離の回避

半導体素子は、半導体基板(110)の上に形成された障壁層を含む。開口(120)が、基板の上に配置された絶縁層(130)の中に形成されることによって、下にある銅の層(140)を暴露する。開口及び下にある銅の層は、熱アニールの存在下でのプラズマ・フリーの還元雰囲気(200)に暴露される。障壁層は、暴露された開口の中、及び、暴露された下にある銅の層の上に蒸着される。

図2  (もっと読む)

(もっと読む)

無電解銅めっき液及びそれを用いた配線基板の製造方法

硫酸銅又は塩化銅を主成分とし、ホルムアルデヒド、2価のコバルトイオン及びグリオキシル酸のうちから選ばれる1種以上の還元剤を含有するとともに、分子量60以上1000以下の例えば下記一般式(1)又は一般式(2)で表されるイオウ系有機化合物及び分子量200以上20000以下のオキシアルキレングリコールを含むことを特徴とする無電解銅めっき液である。アスペクト比の高い微細な溝及び孔の中に空隙を生じることなくめっき膜を堆積させることができる。X1−L1−(S)n−L2−X2 (1)X1−L1−(S)n−H (2)[式中、nは整数、X1及びX2はそれぞれ独立に水素原子、SO3M基またはPO3M基(Mは水素原子、アルカリ金属原子またはアミノ基を示す)、L1及びL2はそれぞれ独立に低級アルキル基又は低級アルコキシ基を示す。]  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】層間絶縁膜をドライエッチングして下層のCu配線の上部に配線溝を形成する際、配線溝の底部に露出した下層のCu配線の表面に絶縁性の反応物が付着したり、配線溝の側壁に露出した炭化シリコン膜や有機絶縁膜がサイドエッチングされるという不具合を抑制する。

【解決手段】炭化窒化シリコン膜を含む積層膜をドライエッチングしてCu配線21の上部に配線溝30を形成する際、CHF3とN2とからなる混合ガスを使用することにより、配線溝30の側壁を垂直に加工すると共に、配線溝30の底部に露出したCu配線21の表面に堆積物や反応物が付着する不具合を抑制する。

(もっと読む)

チップの架橋接続

システムは、第1半導体デバイスと第1電気接続とを有する第1チップ、第2半導体デバイスと第2電気接続とを有する第2チップ、および第3半導体デバイスと第3電気接続とを有する第3チップを有し、第3チップは、第1および第2チップの上面にスタックされ、第1および第2チップのそれぞれの少なくとも一部分を物理的に架橋し、前記第1および第2チップに接続される。  (もっと読む)

(もっと読む)

マイクロ反応チップおよびその製造方法

【課題】 CMOS回路のAl合金配線の有無による段差やAl合金残渣による突起の影響を受けることなく、平坦な表面の反応電極を形成して、均一かつ収率の高いDNAの合成や検出等を促すことができるマイクロ反応チップと、その確実な製造方法を提供する。

【解決手段】 CMOS回路の最終保護層6に形成されたコンタクトホール13に接続電極22が形成されてCMOS回路の配線12に接続されるとともに、最終保護層6上には、接続電極22に達する孔部23Bを備えた保護膜23が形成され、さらにこの保護膜23上には、孔部23Bを介して接続電極22に接続される反応電極24が形成される。保護膜23の表面23Aを研磨加工した後に反応電極24を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 本発明の目的は、導電性の密着性の向上及びマイグレーションの防止を図ることにある。

【解決手段】 半導体装置の製造方法は、(a)電極パッド16及びパッシベーション膜18を有する半導体基板10の上方に、複数回のパターニング工程を行うことにより、少なくとも電極パッド16側が階段状をなす樹脂層40を形成する工程と、(b)樹脂層40をキュアすることにより、樹脂突起41を形成する工程と、(c)電極パッド16と電気的に接続し、かつ樹脂突起41の上方を通る導電層50を形成する工程と、を含む。

(もっと読む)

チップ対チップ接点の絶縁

装置は、基板材料の、相互に接合される2つのスラブを有し、この2つのスラブは、第1領域を第2領域から分ける形状を有して、相互に接合された一対の接点を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 層間絶縁膜に与えるダメージが抑制された、半導体装置の製造方法を提供する。

【解決手段】 第1の絶縁層に埋設される、導電材料よりなる配線構造を形成する配線構造形成工程と、前記第1の絶縁層を除去して前記配線構造を露出させる絶縁層除去工程と、

前記配線構造を埋めるように第2の絶縁層を形成する絶縁層埋設工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

2,241 - 2,260 / 2,805

[ Back to top ]