Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,261 - 2,280 / 2,805

無電解銅めっき液及びそれを用いた配線基板の製造方法

硫酸銅又は塩化銅を主成分とし、ホルムアルデヒド、2価のコバルトイオン及びグリオキシル酸のうちから選ばれる1種以上の還元剤を含有するとともに、分子量60以上1000以下の例えば下記一般式(1)又は一般式(2)で表されるイオウ系有機化合物及び分子量200以上20000以下のオキシアルキレングリコールを含むことを特徴とする無電解銅めっき液である。アスペクト比の高い微細な溝及び孔の中に空隙を生じることなくめっき膜を堆積させることができる。X1−L1−(S)n−L2−X2 (1)X1−L1−(S)n−H (2)[式中、nは整数、X1及びX2はそれぞれ独立に水素原子、SO3M基またはPO3M基(Mは水素原子、アルカリ金属原子またはアミノ基を示す)、L1及びL2はそれぞれ独立に低級アルキル基又は低級アルコキシ基を示す。]  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】層間絶縁膜をドライエッチングして下層のCu配線の上部に配線溝を形成する際、配線溝の底部に露出した下層のCu配線の表面に絶縁性の反応物が付着したり、配線溝の側壁に露出した炭化シリコン膜や有機絶縁膜がサイドエッチングされるという不具合を抑制する。

【解決手段】炭化窒化シリコン膜を含む積層膜をドライエッチングしてCu配線21の上部に配線溝30を形成する際、CHF3とN2とからなる混合ガスを使用することにより、配線溝30の側壁を垂直に加工すると共に、配線溝30の底部に露出したCu配線21の表面に堆積物や反応物が付着する不具合を抑制する。

(もっと読む)

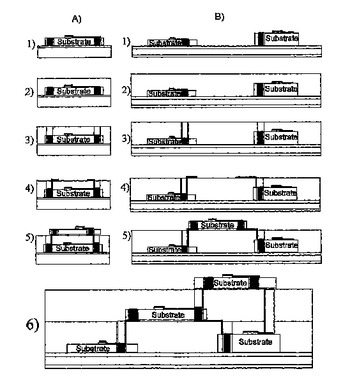

チップの架橋接続

システムは、第1半導体デバイスと第1電気接続とを有する第1チップ、第2半導体デバイスと第2電気接続とを有する第2チップ、および第3半導体デバイスと第3電気接続とを有する第3チップを有し、第3チップは、第1および第2チップの上面にスタックされ、第1および第2チップのそれぞれの少なくとも一部分を物理的に架橋し、前記第1および第2チップに接続される。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】 キャパシタの上部電極の表面形状を安定化させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】 シリコン基板20上に第1アルミナ膜(下地絶縁膜)37を形成する工程と、第1アルミナ膜37上に第1導電膜41、強誘電体膜42、第2導電膜43を順に形成する工程と、第2導電膜43上にマスク材料膜45を形成する工程と、マスク材料膜45を補助マスク45aにする工程と、補助マスク45aと第1レジストパターン46とをマスクにするエッチングで第2導電膜43を上部電極43aにする工程と、強誘電体膜42をパターニングしてキャパシタ誘電体膜42aにする工程と、第1導電膜41をパターニングして下部電極41aにし、下部電極41a、キャパシタ誘電体膜42a、上部電極43aをキャパシタQとする工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】 高融点金属シリサイド層への熱負荷を低減することが可能な半導体装置の製造方法を提供すること。

【解決手段】 シリコン基板10の一部領域に高融点金属シリサイド層13a〜13cを形成する工程と、高融点金属シリサイド層13a〜13cの上に層間絶縁膜21を形成する工程と、層間絶縁膜21の上に、第1導電膜31、強誘電体膜32、及び第2導電膜33を順に形成する工程と、第1導電膜33、強誘電体膜32、及び第2導電膜31をパターニングすることにより、下部電極31a、キャパシタ誘電体膜32a、及び上部電極33aで構成されるキャパシタQを形成する工程と、高融点金属シリサイド層13a〜13cの凝集面積が上限面積以下となるようなアニール時間でアニールを行う工程と、

を有する半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】 露出した上部電極の表面の清浄化を行う場合に、上部電極と、その上に形成する導電膜との接触抵抗の増大を防止することができる半導体装置を提供する。

【解決手段】 基板上に、下部電極、キャパシタ強誘電体膜、及び上部電極がこの順番に積層された強誘電体キャパシタが形成されている。上部電極は導電性酸化物で形成され、上部電極の下層部分における酸素濃度に比べて上層部分における酸素濃度の方が相対的に低くなるような酸素濃度分布を持つ。層間絶縁膜が強誘電体キャパシタを覆う。ビアホールが、層間絶縁膜を貫通し、上部電極の上面よりも深い位置まで達する。このビアホールは、上部電極の酸素濃度が最大になる位置よりも浅い位置で止まる。ビアホールの底面において、導電部材が上部電極に接する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】外部イオンや水分のゲート絶縁膜への浸透を防止する半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、半導体基板、半導体基板上に一方向に延びて形成されたゲート配線220とゲート配線に整列して半導体基板内に形成されたソース/ドレーン領域を含むトランジスタ、ゲート配線上にゲート配線と同一方向に延びて形成され、半導体基板に拡散されるイオンを遮断する拡散防止メタルパターン432aを含む。

(もっと読む)

多層構造の半導体装置及びその製造方法

【課題】多層構造の半導体装置及びこれを製造する方法を提供する。

【解決手段】多層半導体装置は、第1アクティブ半導体構造部、前記第1アクティブ半導体構造部上に形成された第1絶縁膜、前記第1絶縁膜上に形成され、前記第1アクティブ半導体構造部より高く位置する第2アクティブ半導体構造部、前記第2アクティブ構造部上に形成された第2絶縁膜、及び前記第1アクティブ半導体構造部の上部に垂直方向への厚さを有する第1オームコンタクトと、前記第2アクティブ半導体構造部の側壁に径方向へ厚さを有する第2オームコンタクトとを備える。第1オームコンタクトの垂直厚さは、第2オームコンタクトの径方向の厚さより厚く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 導電性プラグのコンタクト不良を防止することができる半導体装置の製造方法を提供すること。

【解決手段】 シリコン基板10上のコンタクトプラグ22aの上に酸化防止膜25を形成する工程と、酸化防止膜25上にキャパシタQを形成する工程と、キャパシタQを覆う第2層間絶縁膜44を形成する工程と、第1ホール44aを第2層間絶縁膜44に形成する工程と、第2層間絶縁膜44をブラシスクラバ処理する工程と、第2層間絶縁膜44をウエット処理する工程と、酸化防止膜25をストッパにして第2層間絶縁膜44に第2ホール44cを形成する工程と、第2ホール44c下の酸化防止膜25をエッチングして除去すると共に、第1ホール44a下の上部電極33aを清浄化する工程と、第1、第2ホール44a、44c内に第1、第2導電性プラグ50a、50cを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の銅配線間の容量低減を実現すると同時に絶縁破壊耐性を向上させ、さらにミスアライメント・ビアを対策する。

【解決手段】基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

配線構造の形成方法,配線構造およびデュアルダマシン構造

【課題】応力が調整された配線構造とその製造方法を提供する。

【解決手段】 配線構造は、導電材料102を有する基板100から構成される。少なくとも1つの応力調整層106が内部に介在された複合誘電体層110が、基板100の上部に存在する。複合誘電体層110における導電機構Sが、少なくとも1つの応力調整層106を貫通し、導電部材102を電気的に接続する。

(もっと読む)

半導体装置の製造方法およびデバイス形成基板および半導体装置

【課題】基板上に形成される多層配線構造の配線間を電気的に絶縁する第1絶縁膜と第2絶縁膜との積層構造において、第2絶縁膜上をCMPした際に発生する第2絶縁膜の膜剥がれを防止する。

【解決手段】基板11上に形成される多層配線構造の配線間を電気的に絶縁する絶縁膜を第1絶縁膜21と第2絶縁膜22との積層構造で形成する半導体装置の製造方法において、前記第1絶縁膜21を形成した後で前記第2絶縁膜22を形成する前に、前記基板11の製品となるチップが存在しない領域上における前記第1絶縁膜21表面に密着膜31を形成する工程を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置及びそれの製造方法

【課題】半導体集積回路装置及びそれの製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成された第1の導電膜パターンと、第1の導電膜パターン上に形成された絶縁膜と、絶縁膜上に形成された第2の導電膜パターンと、第2の導電膜パターン及び絶縁膜全面に形成され、半導体基板に輻射される紫外線を遮断する第1の紫外線遮断膜と、を含む。これにより、半導体基板に紫外線が輻射されることを遮断して外部イオン及び水分が半導体基板に浸透することを遮断でき、半導体集積回路装置の動作特性を向上させうる。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜の表面に埋込配線を形成する場合に、研磨面の平坦性を保つことができる半導体装置の製造方法を提供すること。

【解決手段】 基板200上に、層間絶縁膜203と、この層間絶縁膜を保護する絶縁性材料からなる第1のハードマスク204と、第2のハードマスク205とを成膜する。第2のハードマスク205を開口し、第2のハードマスク205をマスクとして、層間絶縁膜203に埋込配線が埋め込まれるべき凹溝207を形成する。埋込配線の材料209が層間絶縁膜203へ拡散するのを防止する拡散防止膜208Bを成膜する。第2のハードマスク205と拡散防止膜208Bとが同じ材料で、金属元素を組成に含む導電性材料からなる。埋込配線の材料となる導電性金属209を堆積する。導電性金属209の表面側から第1のハードマスク204が露出するレベルまで研磨を行う。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】 2.7より低い比誘電率を有する低誘電率絶縁膜及び4より低い比誘電率を有するバリア絶縁膜を化学気相成長法により成膜する方法を提供するものである。

【解決手段】 シリコン原子による5員環以上の環状構造を有し、かつ該シリコン原子によるシロキサン結合を有する第1のシリコン含有有機化合物と、シリコン原子による4員環以下の環状構造又は4以下のシリコン原子の鎖状構造を有し、かつ該シリコン原子によるシロキサン結合を有する第2のシリコン含有有機化合物とを含む成膜ガスのプラズマを生成し、反応させて基板31上に絶縁膜32を形成する。

(もっと読む)

半導体装置及びその製造方法

層間絶縁膜(1)及びCMPストッパ膜を形成した後、配線溝を形成する。次に、配線溝内にバリアメタル膜(4)及びCu膜(5)を埋め込んだ後、CMPストッパ膜が露出するまで、CMP等によってCu膜(5)及びバリアメタル膜(4)を平坦化することにより、下層配線(17)を形成する。次いで、ドライエッチングによってCMPストッパを除去することにより、相対的に下層配線(17)の表面を周囲から突出させる。続いて、全面にエッチングストッパ膜(6)を形成する。その後、ビアプラグ(18)を形成し、更に、下層配線(17)と同様にして、上層配線(19)を形成する。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】コンタクトホール形成の際に下部金属層のエッチングを防止し、上部金属層と下部金属層間の接触抵抗値の変化を最小化する事が可能な半導体素子の製造方法を提供する。

【解決手段】第1内部金属層36、前記第1金属層37、および前記第2内部金属層38を含む下部金属層を形成し、その上にコンタクトホール停止導電層40を形成する。下部金属層及びコンタクトホール停止導電層40をエッチングしてパターニングする。全体構造上にIMD酸化膜43を蒸着した後、第2コンタクトホールを形成する。前記第2コンタクトホール内にコンタクトプラグ46を形成する。前記コンタクトプラグの形成された前記IMD酸化膜の上部全体に、第3内部金属層47、第2金属層48、および第4内部金属層49を順次蒸着し、前記第3内部金属層、前記第2金属層、および前記第4内部金属層を含む上部金属層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 ポリサイド形成工程を経たパターン上に設けられる導電性プラグの接続部の高抵抗化を防止する半導体装置の製造方法を提供する。

【解決手段】 シリサイド層17を有するポリサイドパターン18を形成すると共に、ソース/ドレイン拡散層15の上部をシリサイド層17とする素子の接続領域(15)を形成する。層間の絶縁膜20を貫通しポリサイドパターン18及び接続領域に到達するホール21を形成する。ホール21内にバリア膜22を形成し、ホール21内を埋め込む金属部材23を形成する。金属部材23をホール21内に埋め込んだ状態にしてから、バリア膜22の関係するシリサイド化及び接続領域(ソース/ドレイン拡散層15)の活性化のための熱処理を加える。

(もっと読む)

半導体ウェハおよびそれにより形成した半導体装置

【課題】半導体ウェハの保護層に形成された溝のアスペクト比が0.5以上である場合においても、再配線を形成する際のレジスト膜に破壊が生じることを防止する手段を提供する。

【解決手段】半導体ウェハが、集積回路を形成した複数の能動領域と、隣合う能動領域間に設けられたダイシング領域と、能動領域の縁部に形成されたシールリングと、シールリングの内側に接近して形成された配線と、能動領域を覆う保護層と、能動領域の保護層上に形成された保護膜と、保護膜上に形成され、集積回路に電気的に接続する再配線とを備え、シールリングと配線との間の保護層に形成された溝のアスペクト比が0.5以上の場合に、この溝を保護膜で覆うようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】 コンタクトホールやビアホールのホール接続部に関し、パターンの疎密にかかわらず、抵抗の上昇を抑制し、抵抗ばらつきのないより安定した構成を有する半導体装置及びその製造方法を提供する。

【解決手段】 絶縁層11下の任意の接続領域10に到達するホール12が形成されている。配線部材13は、ホール12に埋め込まれると共に、絶縁層11上に延在する。ホール12上方を含んで配線部材13上に配線部材14が形成されている。配線部材14は配線部材13と共に絶縁層11上の配線パターン16を構成している。ホール12上部の配線部材13は、例えばWで、リセスができないよう絶縁層11上に所定厚さ保持されている。従って、ホールパターンの疎密に関係なく、ホール12上部はリセスが極めてでき難い構造になる。

(もっと読む)

2,261 - 2,280 / 2,805

[ Back to top ]