Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

241 - 260 / 2,805

配線パターン

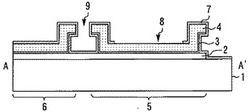

【課題】コンタクトホールを起点とした絶縁膜の剥がれの伸展を防ぐことができる配線パターンを得る。

【解決手段】半絶縁性GaAs基板1上に、配線メタル2が設けられている。配線メタル2上に金メッキ4が設けられている。金メッキ4は、ボンディングパッド部5と配線部6を有する。ボンディングパッド部5及び配線部6を覆うように金メッキ4上に連続してSiN膜7が設けられている。ボンディングパッド部5上においてSiN膜7にコンタクトホール8が設けられている。ボンディングパッド部5と配線部6の間において金メッキ4に段差が設けられている。

(もっと読む)

半導体構造およびその製造方法

【課題】カーボンナノチューブによりビアプラグを構成する半導体装置の製造方法において、製造効率を向上させる製造方法を提供する。

【解決手段】絶縁膜中にビアホールを形成し、ビアホールの底に触媒粒子3cを付着させる。ビアホール中において触媒粒子を起点に、カーボンナノチューブを絶縁膜の表面を超えて成長させ、複数のカーボンナノチューブよりなるカーボンナノチューブの束を形成する。絶縁膜上に前記カーボンナノチューブの束を覆って、誘電体膜の塗布液を塗布し、絶縁膜上における塗布液の厚さを、絶縁膜上における塗布膜の表面の高さが絶縁膜表面におけるカーボンナノチューブの高さ以下になるように減少させる。厚さが低減された塗布膜を硬化させて誘電体膜4Dを形成し、誘電体膜を除去して絶縁膜の表面を露出させ、絶縁膜の表面に、カーボンナノチューブによりビアプラグ4VA,4VBを形成する。

(もっと読む)

電子部品の製造方法

【課題】高温で成膜される低融点金属の凝集を防止し、十分なバリア性及びぬれ性を有するバリア層を形成して、凹部に低融点金属を付け回り良く充填する。

【解決手段】電子部品の製造方法が、4Pa以上20Pa以下の圧力下で、被処理体306と接する電極301に第1のバイアス電力を印加し、プラズマ処理により被処理体306の上にTiNxからなる第1のバリア層404を成膜する手順と、4Pa以上20Pa以下の圧力下で、電極301に第1のバイアス電力よりも小さいイオン入射エネルギーを与える第2のバイアス電力を印加し、またはバイアス電力を印加しないで、プラズマ処理により第1のバリア層の上にTiNxからなる第2のバリア層405を成膜する手順と、第2のバリア層405の上に、Tiからなる第3のバリア層409を成膜する手順と、第3のバリア層409の上に低融点金属406を充填する手順と、を有する。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】スルーホールの微細化による半導体装置の高集積化と、スルーホール内に埋め込まれる導体のカバレッジ性と、を両立させる。

【解決手段】半導体装置は、下層配線2と、下層配線2上に形成され、下層配線2の上面を露出させる開口31を有する第1絶縁膜(例えば、有機絶縁膜3)と、第1絶縁膜上に形成され、スルーホール5が形成された第2絶縁膜(例えば、無機絶縁膜4)とを有する。半導体装置は、更に、スルーホール5に埋め込まれ、下層配線2と電気的に接続された導体9を有する。開口31は、上側に向けて拡径するテーパー形状に形成されている。スルーホール5の側壁5aの少なくとも下端は、開口31の側壁31aを構成する傾斜面の上に位置している。

(もっと読む)

電気めっき方法

【課題】めっき時における平均電流値をより高くした効率的なめっきによるめっき膜の埋込みを行ってめっき時間を短縮し、しかも理想的なめっき膜の埋込みを行うことができるようにする。

【解決手段】内部にスルーホールを形成した基板をめっき液中に浸漬させてめっき槽内に配置し、めっき槽内に配置される基板の表面及び裏面にそれぞれ対向する位置にアノードをめっき槽内のめっき液中に浸漬させて配置し、基板の表面と該表面と対向する位置に配置されるアノードとの間、及び基板の裏面と該裏面と対向する位置に配置されるアノードとの間に、パルス電流を供給して基板の表裏両面に所定時間のめっきを行うめっき処理を複数回に亘って行い、基板の表面と該表面と対向する位置に配置されるアノードとの間、及び基板の裏面と該裏面と対向する位置に配置されるアノードとの間に、めっき時とは逆方向の電流をそれぞれ供給する逆電解処理をめっき処理の間に行う。

(もっと読む)

半導体装置及びその製造方法

【課題】同層配線間の容量及び、上下層配線間の容量を低減し、配線間領域の実効誘電率を低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に形成された第1の絶縁膜101と、第1の絶縁膜101の上部に埋め込まれた複数の第1の配線120と、第1の絶縁膜101上及び複数の第1の配線120上に形成され、開口部を有するライナー絶縁膜104と、ライナー絶縁膜104上に形成された第2の絶縁膜107と、第2の絶縁膜107の上部に埋め込まれた複数の第2の配線110とを備える。第1の絶縁膜101における、第1の配線120の間であって、ライナー絶縁膜104の開口部と重なる部分には、絶縁膜によって塞がれたエアギャップ108が形成されており、第2の絶縁膜107の比誘電率は2.5以下である。

(もっと読む)

拡散バリアー層及びその製造方法

【課題】表面を有する基材アセンブリを提供し、この表面の少なくとも一部の上にバリアー層を提供することを含む、集積回路の製造で使用する方法を提供する。

【解決手段】バリアー層14は、白金(x):ルテニウム(1−x)合金でできており、ここでxは約0.60〜約0.995、好ましくはxは約0.90〜0.98である。バリアー層14は、化学気相堆積によって作ることができ、バリアー層14を形成する表面の少なくとも一部は、ケイ素含有表面でよい。この方法は、キャパシター、蓄積セル、接触ライニング等の製造で使用する。

(もっと読む)

半導体装置

【課題】機械的強度が比較的弱い材料を層間絶縁膜の材料として用いる場合であっても、集積度が高く、信頼性の高い半導体装置を提供する。

【解決手段】支持基板10と、支持基板上に形成され、絶縁層26,28,38,44,50,56,62,68を介して複数の配線36,42,48,54,60,66を積層して成る多層配線構造と、多層配線構造上に形成された電極パッド78と、多層配線構造を貫いて支持基板に達し、電極パッドを支持する構造物76であって、断面が十字形又はY字形である構造物とを有している。この構造物により電極パッドが支持されているため、ボンディングを行った際に電極パッドの下方に存在する構成要素に大きなストレスが加わるのを防止することができ、多層配線構造の一部に、機械的強度が比較的弱い層間絶縁膜を用いた場合であっても、微細な配線パターンの変形や断線等、トランジスタの破壊等を防止することができる。

(もっと読む)

バリア層の形成方法

【課題】 本発明は、以上の点に鑑み、異種金属からなる導電層間に介在されるような場合でも十分なバリア性能を発揮し得るバリア層を生産性よく形成することができるバリア層の形成方法を提供する。

【解決手段】 バリア層BMは、処理対象物Wを一方の導電層CL1を有するものとし、この処理対象物と、例えばTi製のターゲット2とを真空処理室1a内に配置し、真空処理室内に希ガスを導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして一方の導電層表面に第1金属層を形成し、真空処理室内に酸素ガス及び窒素ガスを含むガスを導入してプラズマ雰囲気を形成し、第1金属層の表面を酸窒化処理すると共に、ターゲットをもプラズマ雰囲気に曝して当該ターゲット表面を酸窒化し、真空処理室内に希ガスを更に導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして酸窒化処理された表面に第2金属層を形成してなる。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を削減し、電気抵抗値のバラツキを低減して歩留まりを向上させる。

【解決手段】まず、半導体基板1の平面1aに、開口部を有するマスク層を形成し、次いで、半導体基板1に、マスク層の開口部から電極パッド層4に達するビアホール6を形成した後、マスク層を除去する。次に、金属層形成工程において、半導体基板1に形成したビアホール6の底部6aとなる電極パッド層4上に、電極パッド層4よりも絶縁材料の密着性が低い金属層8を形成する。次に、絶縁層形成工程において、化学気相成長法にて金属層8を除く部分、即ちビアホール6の側壁部6bに絶縁材料からなる絶縁層9を形成する。そして、導電膜形成工程において、半導体基板1の平面1a及びビアホール6の内部に導電層12を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、アルミ配線パターンに含まれるアルミニウムと銅配線に含まれる銅とが反応して高抵抗の合金が生成されることを防止した上で、導電膜である窒化チタン膜に起因する半導体基板の反りを低減することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】第2の層間絶縁膜18に形成されたコンタクト孔27により露出された銅配線16の上面16aを覆うように、窒化チタン膜を含む第1の導電膜21を設けると共に、アルミ配線パターン23と第1の導電膜21及び第2の層間絶縁膜18との間に、窒化チタン膜を含まない第2の導電膜22を設ける。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

金属含有犠牲材料及びダマシン配線形成の方法

【課題】ヴィアのダメージを抑制することが可能な構造及び方法を提供する。

【解決手段】実施形態に係る半導体装置を形成するための構造は、半導体基板と、ベースキャップ層210と、配線層の形成のための絶縁体層215と、絶縁体層上に形成されたハードマスク層220とを備え、ヴィアがハードマスク層及び絶縁体層の少なくとも一部を貫通して形成され、ヴィアが金属又は金属化合物を含有した犠牲材料で埋められている。

(もっと読む)

半導体装置の製造方法

【課題】低コストで、かつ簡便な方法で、コンタクトプラグ上に形成される銅配線の上面にヒロックが生じて短絡が発生することを抑制可能な半導体装置の製造方法を提供する。

【解決手段】配線13を覆う層間絶縁膜15の上面に、層間絶縁膜よりもエッチング速度の遅いエッチングストッパ膜16を形成する。エッチングストッパ膜のうち、配線と対向する部分を貫通する第1の開口部16Aを形成する。エッチングストッパ膜よりも層間絶縁膜がエッチングされやすい条件を用いて、配線の上面が露出するまで第1の開口部の下方に位置する層間絶縁膜をエッチングして、第1の開口部と共にコンタクトホールを構成する第2の開口部15Aを形成する。第1の開口部を埋め込むように、コンタクトホール内に導電膜を成膜することでコンタクトプラグ27を形成する。電解メッキ法により、コンタクトプラグの上面と接触する銅配線39を形成する。

(もっと読む)

241 - 260 / 2,805

[ Back to top ]