Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,581 - 2,600 / 2,805

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法に関する。

【解決手段】 本発明の表面疎水化用組成物は、(A)下記一般式(1)で表される化合物と、(B)沸点が50〜350℃である溶媒とを含む。

Si(R1)2(R2)2 ・・・・(1)

(式中、R1はアシルオキシ基、アルコキシ基またはヒドロキシ基を示し、R2はアルキル基を示す。)

(もっと読む)

半導体装置

【課題】素子全体の機械的な強度の低下を防ぎ、配線を伝播する信号の遅延を低減する。

【解決手段】各配線層100を構成する第1の絶縁層及び前記第3の絶縁層がシリコン炭化窒化膜、シリコン炭化物及び/又はシリコン酸化物を含み、下層配線層の第2の絶縁層はシリコン酸化物を含み、上層配線層の第2の絶縁層はフッ素添加シリコン酸化物及び/又は炭素添加シリコン酸化物を含む。下層配線層の第2の絶縁層の比誘電率を、上層配線層の第2の絶縁層の比誘電率よりも小さくする。

(もっと読む)

半導体装置

【課題】Cu配線および低誘電率絶縁膜を有する半導体装置において、低誘電率絶縁層中に拡散するCuのイオン化、並びにCu+イオンのドリフトを抑制する。

【解決手段】半導体装置10は、素子領域を有する半導体基板11上に形成された低誘電率絶縁層17と、低誘電率絶縁層17で絶縁されたCu配線18、20とを有する。低誘電率絶縁層17とCu配線18、20との間には、単体の仕事関数が3eV未満の元素を含み、Cu濃度が10原子%未満であるイオン化抑制層22が配置されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 リフレッシュ動作を必要とせず、かつ、高集積化・大容量化を実現する半導体記憶装置を提供する。

【解決手段】 半導体基板1上に形成されたメモリセルと、第1電荷保持部と、第2電荷保持部と、第1アクセストランジスタと、第1リークトランジスタ522Aと、第2アクセストランジスタと、第2リークトランジスタと、層間絶縁膜16と、層間絶縁膜16上に形成され、第1電荷保持部に接続されたメモリセル内の第1MISFET56A(Metal-Insulator-Semiconductor Field Effect Transistor)と、層間絶縁膜16上に形成され、第2電荷保持部と接続されたメモリセル内の第2MISFET(Metal-Insulator-Semiconductor Field Effect Transistor)とを備える。

(もっと読む)

成膜方法

【課題】 超臨界状態の媒体を用いた成膜方法において、被処理基板上に供給する被供給物を、安定に被処理基板上に供給する、安定した成膜方法を提供する。

【解決手段】 超臨界状態の媒体にプリカーサを添加した処理媒体によって、被処理基板上に成膜を行う成膜方法であって、前記プリカーサは有機溶媒に溶解された状態で前記超臨界状態の媒体に添加されることを特徴とする成膜方法。

(もっと読む)

めっき装置、半導体基板および金属膜の形成方法

【課題】 大口径の半導体基板に対して、シードCu膜が薄くても面内の膜厚均一性良く電解めっき成長を行うことができるめっき装置、めっき方法を提供する。

【解決手段】 めっき槽110内にはアノード電極104が、基板保持機構107には第1のカソード電極109と第2のカソード電極が設けられている。Cuシード層(図示せず)とアノード電極104間に電流を流してめっき成長を行う際に、半導体基板の中心付近に接する第2のカソード電極からも電流を流す。これによって、Cuシード層が60nm以下の非常に薄膜になった場合においても、半導体基板の中心付近で得られるめっきCu膜厚が薄くなることを防止できる。

(もっと読む)

基板にダマシン構造を製造する方法、集積回路の製造方法およびこれらの方法によって製造される半導体装置

ダマシン構造の製造は、ダマシン構造用の凹部(30)の周りの領域を保護するため、犠牲層(20)を基板(10)上に形成する工程と、前記凹部内に、前記犠牲層と電気接触状態でバリヤ層(40)を形成する工程と、前記凹部内にダマシン構造(50)を形成する工程と、平坦化する工程とを含む。平坦化の間、犠牲層は、バリヤ層またはダマシン構造と電気化学的に反応する。これは、ダマシン構造のくぼみまたは突起を減少させ、銅の残渣を減少させ、そして、バリヤ腐食を減少させるように、ダマシン構造および犠牲層の除去の相対速度を変えることができる。バリヤ層は、ALCVDによって形成することができる。バリヤ層の材料は、WCNおよびTaNの1以上である。犠牲層は、TaN、TiNまたはWとすることができる。  (もっと読む)

(もっと読む)

集積回路の領域に、特にトランジスタの電極にコンタクト・パッドを生成するための方法

【課題】コンパクト・パッドの生成について改善された方法を提供する。

【解決手段】領域(51)は、該領域の表面の少なくとも一部に伸長する区域(510)であって、該領域に対して選択的に除去することが可能な材料から形成される区域を作成するよう、局所的に変更される。該領域は、絶縁材料(7)で覆われており、該区域の表面に出現するオリフィス(90)が、該絶縁材料内に形成される。該選択的に除去が可能である材料は、該区域に代わってキャビティ(520)を形成するように、該区域から、オリフィスを介して除去される。キャビティおよびオリフィスは、少なくとも1つの導電性材料(91)で充填される。

(もっと読む)

半導体装置及びその製造方法

【課題】 フォトリソグラフィー工程を削減するとともに、活性領域の縮小により半導体装置の集積度を高める。

【解決手段】 フィールド形成用のシリコン窒化膜102を用いて素子分離領域105を形成した後、このシリコン窒化膜102をパターニングすることによりゲートトレンチ114bを形成する。次に、ゲートトレンチ114b内にゲート電極材料111〜113を埋め込み、これをエッチバックした後、シリコン窒化膜102を除去する。そして、これにより形成されたコンタクトホール内にコンタクトプラグを埋め込む。これにより、拡散層コンタクトパターンを用いることなく、コンタクトプラグを形成できるとともに、コンタクトプラグの周縁が素子分離領域と活性領域の境界と実質的に一致することから、活性領域を縮小することが可能となる。

(もっと読む)

配線基板の製造方法および半導体装置の製造方法

【課題】ビアホールを形成する際に用いたハードマスク層を除去する前にビアホールを埋め込む保護膜を形成することで、ビアホール内のサイドエッチングの防止を可能とする。

【解決手段】第1面側に実装基板を接続し、第1面とは反対側の第2面側に集積回路チップを実装し、配線基板を貫通する接続部を備えた配線基板の製造方法であって、接続部を形成する工程は、配線基板(SOI基板10のシリコン層13)上にハードマスク層14を形成した後に該ハードマスク層14にビアホールパターン32を形成する工程と、ハードマスク層14をエッチングマスクに用いて配線基板(SOI基板10のシリコン層13)にビアホール15を形成する工程と、ビアホール15内を埋める保護部16を形成する工程と、保護部16を残した状態でハードマスク層14を除去する工程と、保護部16を除去する工程とを備えた製造方法である。

(もっと読む)

成膜方法

【課題】 超臨界状態の媒体を用いた、微細パターンへの成膜方法において、従来に比べて微細パターンへのカバレッジと埋め込み特性を良好とし、さらに微細なパターンへの成膜を可能とする。

【解決手段】 被処理基板上に、超臨界状態の媒体にプリカーサを溶解した処理媒体を供給して成膜を行う成膜方法であって、前記被処理基板の温度を、成膜が生じる温度の下限である成膜下限温度未満である第1の温度とし、当該被処理基板上に前記処理媒体を供給する第1の工程と、前記被処理基板の温度を前記第1の温度から前記成膜下限温度以上である第2の温度に上昇させることで、当該被処理基板上に成膜を行う第2の工程と、を有することを特徴とする成膜方法。

(もっと読む)

自動設計装置、自動設計方法、及び半導体集積回路

【課題】 斜め配線と直交配線とを有する多層配線構造の半導体集積回路においてクロストークの発生を抑制でき、ビアホールの配置制約の少ない半導体集積回路が設計可能な自動設計装置、自動設計方法、及び半導体集積回路を提供する。

【解決手段】 第1線群及び第2線群により定義される第1格子領域401a及び第3線群及び第4線群により定義される第1斜め格子領域402aを第1配線層400a上に設定し、第1〜第4線群を基準として第1配線41a及び第1斜め配線42aを第1配線層400a上に配置する第1層配線部14と、第1格子領域401a及び第1斜め格子領域402a上に重なる位置に、第2格子領域501a及び第2斜め格子領域502aを第2配線層500a上に設定し、第1〜第4線群を基準として、第2配線51a及び第2斜め配線52aを第2配線層500a上に配置する第2層配線部15とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】基板表面側でトランジスタとストレージノード電極との接続を低抵抗で実現する。

【解決手段】トレンチ3を形成し、トレンチの内壁にカラー酸化膜4を形成し、不純物が導入されている半導体材料を、前記カラー酸化膜4が形成されているトレンチ内に埋め込んでストレージノード電極5を形成する。ストレージノード電極5に隣接した基板領域に、ソース・ドレイン領域11を有するトランジスタTRを形成する。ソース・ドレイン領域11とストレージノード電極5とがカラー酸化膜4を挟んで近接する箇所を、半導体材料のエッチングレートに比べ絶縁材料のエッチングレートが大きい条件でエッチングする。このエッチングによりカラー酸化膜4が基板深部側に後退した部分4Aが形成され、そこに非晶質シリコンなどの半導体材料を埋め込んで半導体接続層15Aを形成する。半導体接続層15Aおよび周囲の半導体部に半導体と金属の合金層19を形成し、当該合金層19によりソース・ドレイン領域11とストレージノード電極5とを電気的に接続する。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 (A)ケイ素原子と炭素原子とが交互に連続してなる主鎖を有するポリカルボシラン化合物と、(B)有機溶媒とを含む表面疎水化用組成物。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 環状シランモノマーと有機溶剤とからなる組成物。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜−絶縁膜間等の界面における膜剥がれやクラック等による不良が生じない低誘電率膜を用いた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板101上の第1の絶縁膜102に第1の配線106を形成し、第1の絶縁膜102上に第2の絶縁膜107、第3の絶縁膜108、第4の絶縁膜109及び第5の絶縁膜110を順次堆積する。その後、第1の配線106上の第5の絶縁膜110から第2の絶縁膜107までを突き抜ける第1のスルーホール112と第1のスルーホール112につながる第2の配線溝114に第2の配線117を形成し、第5の絶縁膜110から第1の絶縁膜102までを突き抜ける第2のスルーホール120に第1の支柱123を形成する。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 (A)ポリシランと、(B)有機溶媒を含む、表面疎水化用組成物。(A)下記一般式(1)で表わされる化合物の群から選ばれた少なくとも1種のポリシランと、(B)有機溶媒を含む、表面疎水化用組成物、および該組成物を用いた表面疎水化方法、半導体装置。

[式中、R1,R2は水素原子、アルキル基、ビニル基、アリル基またはフェニル基を示す(ただし、R1,R2のうち水素原子は1個または0個である)。]

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 マロン酸ビス(トリメチルシリル)、1,2−ビス(トリメチルシロキシ)エタン、テトラキス(トリメチルシロキシ)チタニウムなどのシラン化合物と有機溶媒とからなる組成物。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられる絶縁層の表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 1,1,3,3−テトラメトキシジシラシクロブタン、ビス(ジメチルメトキシシリル)メタン、1,3−ジメトキシ−1,1,3,3−テトラメチルジシロキサンなどのシラン化合物と有機溶媒とからなる組成物。

(もっと読む)

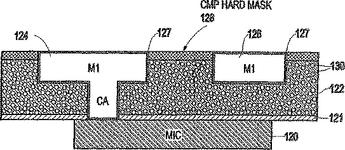

CMP後のポロゲン・バーンアウト・プロセス

【課題】 ライナによって確実に導体が低k誘電体内に拡散するのを防ぐ集積回路構造を提供する。

【解決手段】 論理および機能デバイスを含む少なくとも第1の層を形成し、第1の層の上に少なくとも1つの相互接続層を形成する集積回路構造を形成するための方法および構造を開示する。相互接続層は、論理および機能デバイス間に電気的接続を形成するように構成されている。相互接続層は、まず誘電体層を形成することによって作成される。誘電体層は、第1の材料および第2の材料を含み、第2の材料は、製造環境条件(例えば以下で論じる処理条件)における安定性が第1の材料よりも低い。「第2の材料」はポロゲンを含み、「第1の材料」はマトリックス・ポリマを含む。そして、本発明は、誘電体層における導電性フィーチャを形成し、誘電体層から第2の材料を(例えば加熱によって)除去して、相互接続層内で第2の材料が位置していた場所に空気ポケットを生成する。  (もっと読む)

(もっと読む)

2,581 - 2,600 / 2,805

[ Back to top ]