Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

2,561 - 2,580 / 2,805

多層配線構造を有する半導体装置およびその製造方法

多層配線構造は、第1の層間絶縁膜と、前記第1の層間絶縁上に形成された第2の層間絶縁膜と、前記第1の層間絶縁膜中に形成され第1のバリアメタル膜で側壁面および底面が覆われた配線溝と、前記第2の層間絶縁膜中に形成され第2のバリアメタル膜で側壁面と底面が覆われたビアホールと、前記配線溝を充填する配線パターンと、前記ビアホールを充填するビアプラグとよりなり、前記ビアプラグは前記配線パターンの表面にコンタクトし、前記配線パターンは前記表面に凹凸を有し、前記配線パターンは、前記配線パターン中において前記表面から前記配線パターン内部に向かって延在する結晶粒界に沿って、前記表面におけるよりも高い濃度で酸素原子を含むことを特徴とする。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体基板に形成された開口部の形成状態を、断面観察しないでも確認できるようにすることを目的とする。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成されたパッド電極3を露出するように基板裏面から開口部が形成され、この開口部を介して前記パッド電極3に配線層10が形成されて成るものにおいて、前記開口部の形成状態をモニターするためのモニター開口部6bをスクライブライン上に形成することを特徴とするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、貫通電極を有する半導体装置及びその製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10をエッチングして、半導体基板10の裏面からパッド電極12に到達するビアホール16を形成する。ここで、上記エッチングは、ビアホール16の底部の開口径Aが、パッド電極12の平面的な幅Cよりも大きくなるようなエッチング条件により行われる。次に、ビアホール16の底部でパッド電極12を露出する第2の絶縁膜17を、当該ビアホール16を含む半導体基板10の裏面上に形成する。次に、ビアホール16の底部で露出されたパッド電極12と電気的に接続された貫通電極20及び配線層21を形成する。さらに、保護層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

電子デバイスの製造方法

【課題】 ビアファースト方法を用いるデュアルダマシン配線の形成において、レジストポイズニングを抑制しトレンチ開口パターンを高精度に形成する。

【解決手段】 デュアルダマシン配線の形成工程において、層間絶縁膜に形成したビアホール21を充填しキャップ層16表面を被覆して、セルロースを構成材料とした捕獲兼用樹脂膜1を塗布形成する。好ましくは、不活性雰囲気において200℃程度の焼成温度でその一部を炭化させる。そして、水素プラズマあるいは水素ラジカルを含む水素活性種を照射し、キャップ層16表面の不要な捕獲兼用樹脂膜1aをエッチング除去してダミープラグ2を形成する。ここで、上記捕獲兼用樹脂膜1に予め酸性剤を添加しておくと好適である。このダミープラグ2は、アミン等の塩基性物質を捕獲あるいは中和させ上記課題を達成させる。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法に関する。

【解決手段】 本発明の表面疎水化用組成物は、(A)官能基を有するシラン化合物と、(B)ケトン系溶媒とを含む。

(もっと読む)

電子デバイスの製造方法

【課題】 ビアファースト方法を用いたデュアルダマシン配線の形成において、ビアホール内を充填するダミープラグを高精度に形成する。

【解決手段】 スピン塗布法によりキャップ層106上およびビアホール110を埋設する樹脂膜11を形成する。そして、200℃程度の温度でベーク処理を施した後に、水素ガス、あるいは水素ガスと不活性ガスとの混合ガスをプラズマ励起し、水素活性種である水素プラズマ13を樹脂膜11表面に照射して行う樹脂膜11のエッチバックによりキャップ層106表面の不要な樹脂膜11を除去し、ビアホール110を充填するダミープラグ12を形成する。ここで、不活性ガスとしてArガスあるいはHeガスが好適である。

(もっと読む)

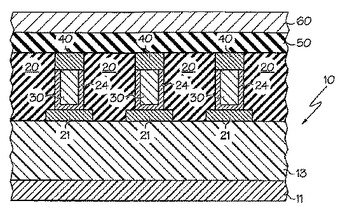

カルコゲニド型メモリ・デバイスのための金属キャップの無電解メッキ

カルコゲニド型メモリ・デバイスにおいて導電性相互接続部の上側に金属キャップを形成する方法が提供され、該方法は、基板10の上側に第1導電性材料の層21を形成する工程と、基板及び第1導電性材料の上側に絶縁層20を堆積させる工程と、絶縁層に開口22を形成して、第1導電性材料の少なくとも一部分を露出させる工程と、絶縁層の上側に且つ開口内に第2導電性材料30を堆積させる工程と、第2導電性材料を部分的に除去して開口内に導電性区域を形成する工程と、開口内の導電性区域を絶縁層の上面よりも低い高さまで凹ます工程と、開口内の凹まされた導電性区域の上側に第3導電性材料のキャップ40を形成する工程と、キャップの上側にカルコゲニド型メモリ・セル材料のスタックを堆積させる工程と、カルコゲニド型メモリ・セル材料のスタックの上側に導電性材料を堆積させる工程とを備え、第3導電性材料は、コバルト、銀、金、銅、ニッケル、パラジウム、白金、及びそれらの合金の群の中から選択される。  (もっと読む)

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法に関する。

【解決手段】 本発明の表面疎水化用組成物は、(A)下記一般式(1)で表される化合物と、(B)沸点が50〜350℃である溶媒とを含む。

HSi(R1)n(R2)3−n ・・・・(1)

(式中、R1はアシルオキシ基、アルコキシ基またはヒドロキシ基を示し、R2はアルキル基を示し、nは1〜3の数を示す。)

(もっと読む)

半導体装置

【課題】素子全体の機械的な強度の低下を防ぎ、配線を伝播する信号の遅延を低減する。

【解決手段】各配線層100を構成する第1の絶縁層及び前記第3の絶縁層がシリコン炭化窒化膜、シリコン炭化物及び/又はシリコン酸化物を含み、下層配線層の第2の絶縁層はシリコン酸化物を含み、上層配線層の第2の絶縁層はフッ素添加シリコン酸化物及び/又は炭素添加シリコン酸化物を含む。下層配線層の第2の絶縁層の比誘電率を、上層配線層の第2の絶縁層の比誘電率よりも小さくする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 接続線と配線との接続部において、接続線周囲の配線幅の拡大や接続線個数の増大に伴う配線ピッチの増大によるレイアウト面積の損失を抑えつつ、かつ、エレクトロマイグレーションの発生を抑える。

【解決手段】 上層配線と下層配線と、上層配線と下層配線とを接続する接続線とを備える半導体装置において、接続線に対して電子の流れの下流側の配線の、少なくとも接続線に接続する接続部の直下又は直上部分、及び接続部から下流側の部分の膜厚を厚くして、厚膜化領域を設ける。

(もっと読む)

半導体装置、DRAM集積回路装置およびその製造方法

多層配線構造を有する半導体装置は、第1の導電領域と、前記基板に対して前記第1の導電領域よりも高い位置に上面を有する第2の導電領域と、前記第1および第2の導電領域を覆う絶縁膜と、前記絶縁膜中に、前記第2の導電領域を露出するように形成された配線溝と、前記絶縁膜中に前記第1の導電領域を露出するように形成されたコンタクトホールと、前記配線溝および前記コンタクトホールを充填する配線パターンとよりなり、前記配線パターンの上面は、前記絶縁膜の上面に一致する。  (もっと読む)

(もっと読む)

集積回路内での金属層の選択的形成

【課題】集積回路(IC)メタライゼーションにおいて信頼性が高いインターフェースを形成するための、生産的かつ制御可能な方法を与える。

【解決手段】埋め込み銅配線の表面が露出したビア底またはCMP直後の銅配線の上面での銅相互接続及び/またはコンタクトの信頼性を強化するための方法が与えられる。当該方法は、露出した銅表面を貴金属から成る気相化合物と接触させる工程と、銅置換反応または貴金属の選択的蒸着(例えば、ALDまたはCVD)により、露出した銅表面上に貴金属の層を選択的に形成する工程から成る。

(もっと読む)

成膜方法、半導体装置の製造方法、半導体装置、プログラムおよび記録媒体

【課題】 半導体装置のCu拡散防止膜とCu配線との密着力を良好とし、半導体装置の信頼性を良好とする。

【解決手段】 被処理基板上にCu膜を成膜する成膜方法であって、前記被処理基板上に形成されたCu拡散防止膜上に密着膜を形成する第1の工程と、前記密着膜上にCu膜を成膜する第2の工程と、を有し、前記密着膜はPdを含むことを特徴とする成膜方法。

(もっと読む)

半導体装置の製造方法及び製造装置

表面に絶縁領域と金属領域とが露出した基板の該表面を、有機系洗浄液を用いて洗浄する。洗浄された基板の表面に紫外線を照射する。これにより、基板表面に残留物が残ることを抑制することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、低誘電率膜の疎水的性質を維持し、歩留まりを向上させることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 半導体基板の上方に、炭素を含む層間絶縁膜50を形成するステップと、表面付近における炭素濃度が低下した層間絶縁膜50上に保護膜60を形成するステップと、保護膜60の表面から層間絶縁膜50の底面まで貫通するように、層間絶縁膜50及び保護膜60のうち所望の領域を選択的に除去することにより、溝80、100を形成するステップと、層間絶縁膜50と保護膜60との界面に、炭素を供給するステップと、溝80、100に導電性材料を埋め込むことにより、導電層を形成するステップとを備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 貫通電極を有する半導体装置及びその製造方法において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10上に第1の絶縁膜11を介してパッド電極12を形成する。次に、パッド電極12上を含む第1の絶縁膜11上に、パッド電極12を露出する開口部14を有した第2の絶縁膜13を形成する。次に、開口部14を含む第2の絶縁膜13上に、当該開口部14を通してパッド電極12と電気的に接続された第1の配線層15を形成する。次に、半導体基板10の裏面からパッド電極12に到達するビアホール16を形成する。次に、ビアホール16の底部のパッド電極12と電気的に接続された貫通電極20及び第2の配線層21を形成する。さらに、保護層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

電子デバイスの製造方法

【課題】 ビアファースト方法を用いるデュアルダマシン配線の形成において、レジストポイズニング現象を抑制しトレンチ開口パターンを高精度に形成する。

【解決手段】 上記デュアルダマシン配線の形成工程において、水素活性種は水素ガスあるいは水素ガスと希ガスの混合ガスから、窒素活性種は窒素ガスあるいは窒素ガスと希ガスの混合ガスから、それぞれに生成し、且つ、上記水素活性種と窒素活性種とは混合して使用しない。例えば、下層配線11表面の防錆剤2は水素活性種3の照射のみにより除去する。また、下層配線11表面に形成する絶縁性バリア層12の成膜は、有機シラン4と窒素活性種を成膜の反応ガスとしてSiCN膜を形成する。このようにすることにより、NH、NH2、NH3あるいはアミンから成る塩基性物質の生成量が大幅に低減し上記課題が達成される。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法に関する。

【解決手段】 本発明の表面疎水化用組成物は、(A)官能基を有するシラン化合物と、(B)炭素数4〜8のアルコール系溶媒とを含む。

(もっと読む)

半導体装置とその製造方法

【課題】 周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

銅相互接続配線およびこれを形成する方法

集積回路のための相互接続構造体における使用のための銅相互接続配線層(602)の表面上のキャッピング層(614)およびガスクラスタイオンビーム処理の適用による集積回路のための改良された集積相互接続構造体を形成する方法。低減された銅拡散と改善されたエレクトロマイグレーション寿命が結果として得られ、また選択的金属キャッピング技法の使用とそれらに付随する歩留まり問題とが回避される。 (もっと読む)

2,561 - 2,580 / 2,805

[ Back to top ]