Fターム[5F033NN13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクト部の配線構造の特徴 (690) | 接触構造 (642) | 下層配線の凹部に接触 (185)

Fターム[5F033NN13]に分類される特許

1 - 20 / 185

半導体装置、半導体装置の製造方法、および電子機器

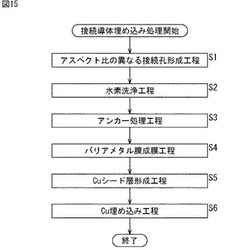

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

電子装置およびその製造方法

【課題】信頼性の高いコンタクト構造を提供する。

【解決手段】電子装置は第1の絶縁膜と、前記第1の絶縁膜の表面に形成された配線溝と、Cuよりなり前記配線溝を充填する配線パタ―ンと、前記配線パタ―ンの表面に形成され、Cuよりも大きな弾性率を有する金属膜と、前記第1の絶縁膜上に形成された第2の絶縁膜と、Cuよりなり、前記第2の絶縁膜中に形成され、前記金属膜とコンタクトするビアプラグと、を備える。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体装置の製造方法

【課題】スルーホールの底部における突起の形成を防止して、半導体装置の品質を安定させる手段を提供する。

【解決手段】配線層5と、該配線層上に形成された金属窒化膜8とを覆う層間絶縁膜9とを形成した半導体ウェハに、層間絶縁膜を貫通し金属窒化膜に達するスルーホール10を形成する工程を備えた半導体装置の製造方法において、スルーホールを形成する工程は、層間絶縁膜上に、レジストマスク18を形成する工程と、半導体ウェハを第1の温度とし、異方性エッチングにより層間絶縁膜をエッチングする第1のエッチング工程と、半導体ウェハを、第1の温度より高い第2の温度とし、レジストマスクをそのまま用いて、異方性エッチングにより金属窒化膜の上表面をエッチングする第2のエッチング工程と、レジストマスクを除去する工程と、を備え、第1のエッチング工程と、第2のエッチング工程で用いるエッチングガスとを同一とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極と配線との接続部位の抵抗のバラつきを低減させて、配線信頼性を向上させる。

【解決手段】貫通電極用の穴部を設け、配線層に対してオーバエッチングを施す。穴部に銅を埋め込むことにより、銅からなる貫通電極を形成させて、アルミニウムからなる配線と接続させた後、熱処理により貫通電極と配線とが接続される接触領域Gを合金化させることで、貫通電極と配線との抵抗バラつきを低減させて、配線信頼性を向上させる。本技術は、半導体装置と、その製造に適用することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

半導体装置、製造方法、および電子機器

【課題】製造コストの低減を図ることができる。

【解決手段】シリコンウェハ31の上面側の内部にメタルパッド32が形成され、シリコンウェハ31の上面にガラスシール材33が積層され、メタルパッド32がシリコンウェハ31の上面に露出するようにシリコンウェハ31およびガラスシール材33に加工された開口部にストッパ層34が形成される。そして、シリコンウェハ31の下面からストッパ層34まで開口するように縦孔35が形成され、縦孔35の先端部においてストッパ層34を介してメタルパッド32に電気的に接続され、シリコンウェハ31の下面まで延在するようにメタルシード層37が形成される。本発明は、例えば、固体撮像装置に適用できる。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び電子機器

【課題】センサ基板と回路基板とを電極間で張り合わせてなる構成において電極間の接合面積を確保することが可能な3次元構造の固体撮像素子を提供する。

【解決手段】光電変換部21が配列形成されたセンサ基板2と、光電変換部21を駆動する回路が形成されセンサ基板2に対して積層された回路基板7と、センサ基板2における回路基板7側の界面に引き出されたセンサ側電極45と、回路基板7におけるセンサ基板2側の界面に引き出された回路側電極65とを備え、センサ側電極45と回路側電極65とは、凹型電極に凸型電極を嵌め合わせた状態で接合されていることを特徴とする固体撮像素子1である。

(もっと読む)

1 - 20 / 185

[ Back to top ]