Fターム[5F033NN15]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクト部の配線構造の特徴 (690) | 接触構造 (642) | コンタクトプラグが絶縁膜より突出 (59)

Fターム[5F033NN15]に分類される特許

1 - 20 / 59

固定装置

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

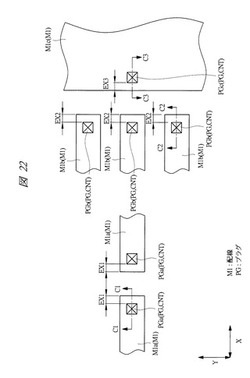

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを用いた実装における端子間のショートや実装精度の低下を防止する。

【解決手段】半導体チップ88の貫通ビア86の上に、他の半導体チップ101を実装する。半導体チップ101のバンプ103は、4つの貫通ビア86で囲まれた領域に導かれて接合される。各貫通ビア86は、バンプ103に面する側面及び上面の保護膜31がエッチングによって除去されており、バンプ103のハンダ材料への濡れ性が保護膜31で覆われた領域よりも良好になっている。このために、ハンダ材料のはみ出しによる他の電極との間のショートが防止される。さらに、1つのバンプ103に複数の貫通ビア86からなる接続端子を配置するので、バンプ103に確実に接合できる。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】基板を貫通する電極の形成に適用できる新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に半導体素子を形成する工程と、半導体基板に孔を形成する工程と、半導体素子の上方と孔の内壁および底を覆うように絶縁膜を形成する工程と、異方性エッチングにより、半導体素子の上方と孔の底の絶縁膜を除去する工程と、孔の底に金属拡散防止膜を形成する工程と、孔に導電膜を埋める工程とを有する。

(もっと読む)

半導体装置

【課題】アンダーバリアメタルに起因する応力集中を緩和し、トランジスタの特性の変動を抑制することができるパッド電極構造を備える半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成された電極パッド6と、電極パッド6の上に形成され、且つ、電極パッド6の一部が露出するような第1開口部を有する第1絶縁膜7と、第1絶縁膜の上に形成され、且つ、第1開口部における少なくとも一部が露出するような第2開口部を有する第2絶縁膜8と、第2絶縁膜8及び電極パッド6の上に形成されたアンダーバリアメタル10とを備えている。アンダーバリアメタル10は、第2絶縁膜8の表面における第2開口部の外側である第1領域と電極パッド6の表面における第2開口部の内側である第2領域とにより挟まれる第3領域により分離されている。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び電子機器

【課題】センサ基板と回路基板とを電極間で張り合わせてなる構成において電極間の接合面積を確保することが可能な3次元構造の固体撮像素子を提供する。

【解決手段】光電変換部21が配列形成されたセンサ基板2と、光電変換部21を駆動する回路が形成されセンサ基板2に対して積層された回路基板7と、センサ基板2における回路基板7側の界面に引き出されたセンサ側電極45と、回路基板7におけるセンサ基板2側の界面に引き出された回路側電極65とを備え、センサ側電極45と回路側電極65とは、凹型電極に凸型電極を嵌め合わせた状態で接合されていることを特徴とする固体撮像素子1である。

(もっと読む)

半導体構造およびその製造方法

【課題】カーボンナノチューブによりビアプラグを構成する半導体装置の製造方法において、製造効率を向上させる製造方法を提供する。

【解決手段】絶縁膜中にビアホールを形成し、ビアホールの底に触媒粒子3cを付着させる。ビアホール中において触媒粒子を起点に、カーボンナノチューブを絶縁膜の表面を超えて成長させ、複数のカーボンナノチューブよりなるカーボンナノチューブの束を形成する。絶縁膜上に前記カーボンナノチューブの束を覆って、誘電体膜の塗布液を塗布し、絶縁膜上における塗布液の厚さを、絶縁膜上における塗布膜の表面の高さが絶縁膜表面におけるカーボンナノチューブの高さ以下になるように減少させる。厚さが低減された塗布膜を硬化させて誘電体膜4Dを形成し、誘電体膜を除去して絶縁膜の表面を露出させ、絶縁膜の表面に、カーボンナノチューブによりビアプラグ4VA,4VBを形成する。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

熱の抽出及び遮蔽のための埋込み式熱伝導層

【課題】多ブロック半導体デバイスにおいて熱を抽出しかつ遮蔽するための方法及び装置。

【解決手段】一実施形態は、互いに上下して積み重ねられる複数のブロック205,305は、熱伝導材料で充填される垂直バイア240,350によって相互に接続され、かつ埋込み式の熱伝導層340によって分離される。熱伝導層は、複数のブロックのうちの一番上または下へ熱抽出層または接地平面として接着される。熱伝導層は、高い熱伝導率を有する。基板110上には、断熱層210,320が堆積される。断熱層は、基板の加熱を低減するための温度勾配をサポートすることができる。断熱層の内部には埋込み式の熱伝導層が形成され、これは、基板を介して外部の熱抽出層へ接続される垂直バイアを有する。半導体層はこの断熱層上へ堆積され、電気配線用にパターン化される。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

半導体装置及びその製造方法

【課題】TFT回路を備える半導体装置において、歩留まりの低下を抑制可能な半導体装置及び半導体装置の製造方法を提供することを目的とする。

【解決手段】ロジック回路10上に形成された層間絶縁膜22と、層間絶縁膜22上に形成され、上部から所定の高さまでシリサイド化されたシリサイド層30を含むアモルファスシリコン層23と、アモルファスシリコン層23上に形成されたTFTと、層間絶縁膜22を貫通する貫通孔24を埋め込むように形成され、ロジック回路10に電気的に接続すると共に、上部がシリサイド層30に接続するコンタクトプラグ25とを備える。

(もっと読む)

1 - 20 / 59

[ Back to top ]