Fターム[5F033NN30]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | 断面が長方形以外 (728)

Fターム[5F033NN30]の下位に属するFターム

上部を拡大、コンタクトパッド (511)

Fターム[5F033NN30]に分類される特許

141 - 160 / 217

被膜形成方法、絶縁膜を有する構造体及びその製造方法並びに電子部品

【課題】孔部の少なくとも内壁面に均一な被膜を形成する方法、この方法を利用した、絶縁膜を有する構造体及びその製造方法並びに電子部品を提供する。

【解決手段】本発明の被膜形成方法は、開口部の面積が25〜10,000μm2であり且つ深さが10〜200μmである孔部を有する基板に、溶剤を塗布する溶剤塗布工程と、樹脂成分及び溶剤を含有し、剪断速度6rpmにおける粘度V1(mPa・s)と、剪断速度60rpmにおける粘度V2(mPa・s)との比(V1/V2)が、1.1以上の樹脂組成物を、該樹脂組成物が上記孔部内の上記溶剤と接触するように、上記基板に塗布する樹脂組成物塗布工程と、塗膜を乾燥する乾燥工程と、を備え、該孔部の内壁面及び底面のうちの少なくとも該内壁面に上記樹脂成分を含む被膜を形成する。

(もっと読む)

半導体装置、電子機器、および半導体装置の製造方法

【課題】高い段差の上方から下方に掛けて段切れすることなく良好にパターン形成された導電性パターンを備えたことにより歩留まりの向上が図られた半導体装置および電子機器、さらには半導体装置の製造方法を提供する。

【解決手段】基板10に達する第1開口部11aを備えて基板10上に形成された第1絶縁膜11と、第1開口部11a内において基板10に達する第2開口部13aを備えて第1絶縁膜11上を覆う第2絶縁膜13と、第2開口部13aを介して基板10に接する状態で第2絶縁膜13上に設けられた導電性パターン15とを備えた。第2絶縁膜13は、第1開口部11aの上方肩部をラウンド形状に覆う。

(もっと読む)

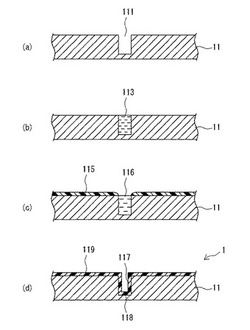

半導体装置およびその製造方法

【課題】接地インダクタンスを低減化した半導体装置およびその製造方法。

【解決手段】半絶縁性基板11の第1表面に配置され,複数のフィンガーを有するゲート電極、ソース電極およびドレイン電極と、第1表面と反対側の第2表面に配置された接地導体26と、ゲート電極、ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極14、ソース端子電極18およびドレイン端子電極12と、ゲート電極、ソース電極およびドレイン電極の下部の半絶縁性基板11上に形成された動作層と、動作層近傍の小口径VIAホール30と接地導体26近傍の大口径VIAホール20とからなる多段VIAホールと、多段VIAホールの内壁面および第2表面に形成され、ソース端子電極18に対して第2表面側から接続された接地電極23とを備える半導体装置およびその製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】セルコンタクトのアクティブ領域に対する位置合わせにずれが生じた場合でも、コンタクト抵抗を増大させない半導体装置及びその製造方法を提供する。

【解決手段】半導体基板20、半導体基板に設けられた素子分離膜21、層間絶縁膜60及び導電プラグ62を備えて構成される。半導体基板は、一方の主表面20a側に、第1の方向及び第2の方向に行列配列されたメモリセルを有している。導電プラグは、層間絶縁膜内に形成されていて、メモリセルと層間絶縁膜上に形成される配線74とを電気的に接続する。各メモリセルは、ゲート電極34と、一対の不純物拡散領域40を備えている。不純物拡散領域は、主表面側に金属シリサイド膜46を有している。導電プラグは、素子分離膜上と金属シリサイド膜上とに形成されている。金属シリサイド膜は、第1部分47と、第2部分48を備えていて、第1部分の厚みが第2部分の厚みよりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】外部からの応力による構成要素の破損を防止する。

【解決手段】半導体装置10は、基板20と、複数の電極パッド24と、複数の第1開口部26aを有する表面保護膜26と、第2開口部30bを有する絶縁膜30と、電極パッド24から絶縁膜上に導出されている、柱状電極接続領域44aを有する配線44であって、柱状電極接続領域が第1開口部の真上に位置しており、かつ配線の柱状電極接続領域側の端縁が第1開口部の輪郭内に位置している配線を含む再配線層40と、柱状電極接続領域に底面50bの一部分である第1部分領域50baが接続されていて、電極パッドの真上に少なくとも底面の第1部分領域を位置させており、かつ第2部分領域50bbを絶縁膜とは非接触として設けられている柱状電極50とを具えている。

(もっと読む)

半導体装置およびその製造方法

【課題】開口径の異なるコンタクトが混在することによる歩留りの低下を抑えることが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板11に形成された所定パターンの活性領域12と、半導体基板11上の所定位置に形成されたゲート電極14と、半導体基板11上に形成された層間膜16aと、中央部において幅が極小となる開口形状を有し、層間膜16aを貫通して活性領域12およびゲート電極14と接続されるシェアードコンタクト17を備える

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の大きさを大きくすることなく、踏外しマージンおよびショートマージンを十分に確保できる半導体装置を提供する。

【解決手段】第1層間絶縁膜13と、前記第1層間絶縁膜13上に形成された第2層間絶縁膜14と、前記第1層間絶縁膜13と前記第2層間絶縁膜14とを貫通して形成され、上面1bの外径d1が第1層間絶縁膜13と第2層間絶縁膜14との界面位置13aの外径d2よりも小さい下層コンタクトプラグ1と、前記第2層間絶縁膜14上に形成された第3層間絶縁膜22と、前記下層コンタクトプラグ1上で前記第3層間絶縁膜22を貫通して形成され、前記下層コンタクトプラグ1と電気的に接続された上層コンタクトプラグ2とを有する上下導通構造を備える半導体装置とする。

(もっと読む)

半導体装置とその製造方法および電子機器

【課題】生産効率を低下させることなく、接続信頼性の高い貫通電極を備えた半導体装置とその製造方法および電子機器を提供する。

【解決手段】基体2の能動面3上に形成された電極パッド5,6と、基体2の裏面7から電極パッド5,6に向けて形成された貫通電極8,9とが、電極パッド5,6から貫通電極8,9に向けて立設された平面視リング状のプラグ15,16を介して電気的に接続されており、貫通電極8,9の外周からプラグ15,16の表面にかけて、基体2との間に絶縁膜4a,14が連続形成されている。

(もっと読む)

回路装置、回路装置の製造方法および半導体モジュール

【課題】回路装置における配線の接続信頼性を向上する技術を提供する。

【解決手段】回路装置10は、回路素子が形成された半導体基板12と、半導体基板12の表面Sに形成された電極14と、電極14の上に設けられた絶縁層16と、絶縁層16の上に設けられた第2の配線層18と、絶縁層16を貫通して電極14および第2の配線層18を電気的に接続する導電性バンプ20と、を備える。導電性バンプ20は、電極14と第2の配線層18との導通方向の結晶粒のサイズより、半導体基板12の表面Sと平行な方向の結晶粒のサイズが大きい。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を有している。層間絶縁膜1内に下部配線5を備えた第一層を準備する。第一層上にライナー膜11を設ける。層間絶縁膜12をライナー膜11上に設ける。層間絶縁膜12およびライナー膜11を貫通して下部配線5に達するトレンチ14を形成する。トレンチ14の側壁に沿った層間絶縁膜12上及びライナー膜11上と、下部配線5上に位置するトレンチ14の底部とにバリアメタル13を形成する。トレンチ14底部を物理エッチングすることにより、トレンチ14底部のバリアメタル13と下部配線5とを削り、円錐形状又は半球形状の孔6をトレンチ14の下側に設ける。トレンチ14の側壁上のバリアメタル13上及び孔6内に導電膜15を形成する。トレンチ14及び孔6内にCu膜19を埋め込む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】DRAMなどの半導体記憶装置において、容量コンタクトの抵抗値を下げつつ、ショート不良の発生を防止する。

【解決手段】活性領域111に形成された拡散層領域121〜123と、これら拡散層領域にそれぞれ接続されたセルコンタクト131〜133と、これらセルコンタクトにそれぞれ接続された柱状体141〜143と、柱状体141に接続されたビット線150と、柱状体142,143にそれぞれ接続された容量コンタクト152,153と、容量コンタクトにそれぞれ接続されたストレージキャパシタ170とを備える。これにより、セルコンタクトと容量コンタクトとの間に柱状体が介在することから、その分、容量コンタクトの深さが浅くなる。したがって、容量コンタクトの抵抗値を下げつつ、ショート不良の発生を防止することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】選択ゲートトランジスタのゲート電極間のビット線コンタクトのコンタクトホール形成を確実にできるようにする。

【解決手段】シリコン基板1にメモリセルトランジスタおよび選択ゲートトランジスタのゲート電極MG、SGが形成されたもので、選択ゲートSG−SG間の構成として、ゲート電極SGの対向する側壁にシリコン窒化膜12の厚いスペーサを設ける。シリコン窒化膜12はシリコン基板1に対してシリコン酸化膜11を介した状態で形成される。ゲート電極MG、SGの上部にはコバルトシリサイドの金属シリサイド層8が形成される。ビット線コンタクトのコンタクトホール16は、シリコン窒化膜13、12の部分で自己整合的に制約を受けて狭くなり、確実にコンタクトプラグ17を形成できる。

(もっと読む)

半導体素子の製造方法

【課題】改良されたランディングプラグを備えた半導体素子に関する。

【解決手段】半導体素子の製造方法は、ランディングプラグコンタクト領域を画成する半導体基板にリセスゲートを形成し、リセスゲートの側壁にゲートスペーサを形成し、ランディングプラグコンタクト領域の半導体基板をソフト食刻して丸いプロファイルと側壁を備えたリセスを形成し、ゲートスペーサとリセスの側壁に側壁スペーサを形成し、リセスゲート、リセスゲートスペーサ及びリセスを含む半導体基板の上部に層間絶縁膜を形成し、層間絶縁膜を選択的に食刻してランディングプラグコンタクトホールを形成し、ランディングプラグコンタクトホールに導電層を埋め込んでランディングプラグを形成する。

(もっと読む)

配線基板、電子回路装置およびその製造方法

【課題】各貫通電極配線の信号遅延時間を同等にする。

【解決手段】半導体装置101は、複数の半導体チップ102a,102bからなる。半導体チップ102a,102bは、それぞれ複数の貫通電極106(106a又は106b)を備え、貫通電極106が積層方向に沿って連結された貫通電極配線110,111により入出力端子103と電気的に接続されている。複数の貫通電極106のうち少なくとも一部は、各貫通電極配線110,111の信号遅延時間が等しくなるように、当該貫通電極を含む貫通電極配線110,111の長さに応じて成形された形状の信号遅延調整用貫通電極である。

(もっと読む)

ウエハのバイア形成

全プロセス完了ウエハに導電性バイアを形成する方法は、全プロセス完了ウエハの背面に少なくとも一つの溝領域を画成するステップと、その溝領域内に少なくとも一つの溝を、その溝内に形成されるバイアに対して全長にわたってシード被覆を可能にする、全体的な深さまで形成するステップと、全プロセス完了ウエハの溝内に所定の深さまでバイアを形成するステップと、バイアの全長にわたってシード層を堆積するステップと、導電性メタルでバイアを充填するためにシード層をめっきするステップとを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 ポリメタルゲート構造を有し、コンタクトホール下面の半導体基板表面及びコンタクトホール下面のプラグ表面にシリサイド膜を有する半導体装置の製造方法におけるゲート構造への配線とコンタクトホール内シリサイド膜への配線の工程を簡略化すること。

【解決手段】 層間絶縁膜(37)の第1の開口部41に底部に形成されるコンタクト32と前記層間絶縁膜(35,37)に半導体基板(10)に達するように形成される第2の開口部43と前記層間絶縁膜にポリメタルのゲート電極に達するように形成される第3の開口部(42)とを有する第1の形状を形成し、その表面にコバルト層を堆積させ、熱処理し前記コンタクトの表面及び前記第2の開口部の底面にコバルトシリサイド層(52)を形成し、コバルトシリサイド層が形成された状態で前記ポリメタルを溶解せずコバルトを溶解する薬液で処理して未反応のコバルト(51)を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線構造を備えた半導体装置において、配線溝底面におけるバリアメタル膜の消失を回避しつつ、ビアプラグ下端において下層配線パターンと確実なコンタクトを実現する。

【解決手段】配線溝およびビアホールの側壁面および底面を覆うようにバリアメタル膜をスパッタ法により堆積する際に、前記バリアメタル膜の堆積を、層間絶縁膜主面上における堆積速度がスパッタエッチング速度よりも大きくなる第1の条件で前記バリアメタル膜の堆積を行う第1のスパッタ工程と、前記層間絶縁膜主面上における堆積速度とスパッタエッチング速度がほぼ等しくなる第2の条件で前記バリアメタル膜の堆積を行う第2のスパッタ工程により、実行する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】セル面積の縮小化とともに、シェアードコンタクト形成時のゲート電極側部に形成されたサイドウォールの膜減りによる半導体基板への突き抜けを防止する。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極13が形成され、その両側にサイドウォール15,16が形成され、ゲート電極13両側の半導体基板にソース・ドレイン17,18が形成されている半導体基板上に、ゲート電極13、ソース・ドレイン17,18等を被覆する犠牲膜23を形成する工程と、犠牲膜23にゲート電極13上から一方側のソース・ドレイン18上を開口するシェアードコンタクト24を形成する工程と、シェアードコンタクト24の内部にゲート電極13と一方側のソース・ドレイン18に接続する導電性プラグ26を形成する工程と、犠牲膜23を除去する工程とを備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタにチャージアップダメージを与えることなく、安定なコンタクト抵抗を有する上部電極用コンタクトプラグを実現する。

【解決手段】半導体基板100上に形成された第1の層間絶縁膜105中の第1のホールの底部及び側壁部に形成された下部電極108と、下部電極108を覆う容量絶縁膜109と、容量絶縁膜109を覆う上部電極110と、第1の層間絶縁膜105中の第2のホールの底部及び側壁部に形成され、上部電極110を構成する導電膜を延設させてなる上部電極用コンタクト部112と、第1の層間絶縁膜105、上部電極110及び上部電極用コンタクト部112上に形成された第2の層間絶縁膜114と、第2の層間絶縁膜114を貫通し上部電極用コンタクト部112に到達する第1のコンタクトホール内に埋め込まれた上部電極用コンタクトプラグ120とを備え、第2のホールは第1のホールの開口径よりも大きい開口径を有している。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上からフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有する。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透過層表面に撥液処理を行ってもよい。

(もっと読む)

141 - 160 / 217

[ Back to top ]