Fターム[5F033NN30]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | 断面が長方形以外 (728)

Fターム[5F033NN30]の下位に属するFターム

上部を拡大、コンタクトパッド (511)

Fターム[5F033NN30]に分類される特許

161 - 180 / 217

柔軟性機械的サポートを構成するワイヤ要素用ハウジングを形成する凹部を具備するベアマイクロエレクトロニクスチップ、製造プロセスおよび微細構造

マイクロエレクトロニクスチップ(1)は2つの平行主面(4、5)と側面(6、7)とを備える。該面(4、5、6、7)のうちの少なくとも1つが、少なくとも1つの電気接続要素を具備し、かつワイヤ要素(10、11)用のハウジングを形成する凹部を備える。該ワイヤ要素(10、11)は、該接続要素を介する該チップ(1)と外部との間の電気接続と、該チップ用柔軟性機械的サポートと、の両方を同時に構成する。  (もっと読む)

(もっと読む)

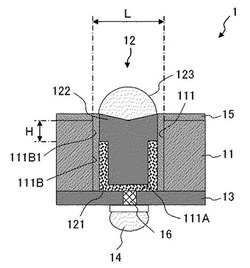

半導体装置および半導体装置の製造方法

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

高アスペクト比のフィーチャを形成するための選択的化学エッチングおよび関連構造

酸化ケイ素層などの層間誘電体層(130)は、ケイ素種とハロゲン種、また好ましくは炭素種と酸素種を含む、プラズマ化学エッチングを用いて選択的にエッチングされる。ケイ素種は、SixMyHzなどのケイ素化合物から生成することができ、“Si”はケイ素、“M”は一つ以上のハロゲン、“H”は水素であり、x≧1、y≧0、z≧0である。炭素種はCαMβHγなどの炭素化合物から生成することができ、“C”は炭素、“M”は一つ以上のハロゲン、“H”は水素であり、α≧1、β≧0、γ≧0である。酸素種はO2などの酸素化合物から生成することができ、これは炭素と反応して揮発性化合物を形成し得る。  (もっと読む)

(もっと読む)

半導体装置

【課題】導電部の破壊や電極部の断線等の損傷を防止して、導電部と電極部との電気的な接続信頼性を向上した半導体装置を提供すること。

【解決手段】本発明の半導体装置1は、基板2の一方の面2aに配された電極部3と、前記基板の他方の面2bから前記電極部の少なくとも一部が露呈するように、前記基板内に設けられた貫通孔4と、前記貫通孔内の側面および露呈された前記電極部を覆うように配され、前記電極部と電気的に接続される導電部7と、を備え、前記貫通孔の内側面と前記電極部とが交わる角部において、前記導電部の断面形状Rが、円弧状または多角状であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】酸化ハフニウム等の高誘電率絶縁膜を用いたMIMキャパシタにおいて、高容量密度と高容量精度を両立し、MIMキャパシタの耐圧低下を防止し、リーク電流増大を低減する技術を提供する。

【解決手段】第一の金属配線700、加工された容量膜405、加工された上部電極215、第三の金属配線702から構成されるMIMキャパシタにおいて、第一の金属配線を被覆するように酸化シリコンからなる層間絶縁膜を形成した後、この第一の金属配線直上の層間絶縁膜の接続孔層に相当する領域に対し、第一の金属配線の上面が露出しないようにこの層間絶縁膜に第一の開口部を形成し、次に、第一の金属配線表面が露出するように第一の開口部の内部に第二の開口部を形成した後、容量膜、第三の金属配線を形成されることにより達成される。

(もっと読む)

集積回路及びこれを備えるアセンブリ

高周波数で用いるのに適しており、且つ、入力と出力を有する第1のキャパシタ及びグランド接続を備える集積回路であって、キャパシタは、該キャパシタの出力とグランド接続との間の抵抗を介してESD保護され、抵抗は、グランド接続のRF性能への実質的な影響を阻止するように充分に高い抵抗値を有する、集積回路。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】厚い絶縁膜をドライエッチングしてスルーホールなどを形成する場合、開口径が小さくなるとエッチング停止が生じる問題や底部ほど先細りして接触面積が小さくなり接触抵抗が増大する問題を回避する半導体装置の製造方法を提供する。

【解決手段】ホールを形成する位置に、酸素や水素プラズマのみでエッチングが可能なペデスタル141を予め形成しておき、その上に層間絶縁膜142を形成する。ペデスタル上の層間絶縁膜をフッ素含有プラズマでエッチングしてホール147aを形成しペデスタルの表面を露出させる。その後、酸素プラズマを用いてペデスタルをエッチングする。ペデスタルには非晶質カーボン膜や有機塗布膜を用いることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板上にBCB等の低誘電率材料からなる絶縁膜と配線とが各々2層交互に積層されて設けられた半導体装置において、絶縁膜間で剥離が生じにくいようにする。

【解決手段】 シリコン基板1の上面に設けられた酸化シリコン等からなるパッシベーション膜3の上面の周辺部を除く領域にはBCB等の低誘電率材料からなる第1、第2の絶縁膜5、9と第1、第2の配線8、12とが交互に積層されて設けられている。第2の配線12を含む第2の絶縁膜9の上面および第1、第2の絶縁膜5、9の側面はエポキシ系樹脂等からなる封止膜14によって覆われている。これにより、第1、第2の絶縁膜5、9間で剥離が生じにくいようにすることができる。

(もっと読む)

ナノ構造体に基づく相互接続および熱の散逸体

本発明は、導電または絶縁基板上に成長されるナノ構造体およびそれを作る方法を提供する。請求項の方法によって成長されるナノ構造体は、電子装置における相互接続および/または熱の散逸体に適切である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド技術を用いなくても抵抗を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】トランジスタを覆うBPSG膜8を形成する。次に、BPSG膜8上にBPSG膜9を形成する。BPSG膜8中のB濃度は、BPSG膜9中のB濃度の5倍程度高いものとする。次いで、ゲート電極を境にしてBPSG8膜をソース拡散層41側の部分とドレイン拡散層42側の部分とに分離する。その後、BPSG膜8及び9にソース拡散層41まで到達するコンタクトホール21を形成する。続いて、コンタクトホール21に露出しているBPSG膜8を等方性エッチングにより除去することにより、ソース拡散層41とBPSG膜42との間に空洞部を形成する。そして、空洞部内にTiN等からなるバリアメタル膜12を形成する。

(もっと読む)

相互接続構造体、半導体構造体および相互接続構造体の形成方法(相互接続用途のための耐酸化性シード層の形成)

【課題】貴金属シード層上への導体めっきの表面酸化問題を実質的に低減する、シングルまたはデュアル・ダマシン型の相互接続構造体およびそれを形成する方法を提供する。

【解決手段】本発明によれば、貴金属シード層を処理するために水素プラズマ処理が用いられ、その結果、処理された貴金属シード層は表面酸化に対して非常に耐性がある。本発明の耐酸化性貴金属シード層は、低いC含有量または低い窒素含有量あるいはその両方を有する。

(もっと読む)

半導体装置の製造方法

【課題】従来の構成では、接続プラグ上の絶縁層に設けられた開口部内に導電膜を堆積させる際、接続プラグの表面と開口部の内表面とに導電膜が連続して形成されない可能性があり、接続プラグと導電膜との電気的接続信頼性が低減してしまう可能性があった。

【解決手段】本願発明では、接続プラグが配置される接続プラグ領域は第1の長さ方向と第1の幅方向とから成る長尺形状を備え、接続プラグ上の絶縁層に設けられた開口部により露出する開口領域は第2の長さ方向と第2の幅方向とから成る長尺形状を備え、開口部を設ける際のエッチング工程において、接続プラグ領域の第1の長さ方向と開口領域の第2の長さ方向とが所定の角度を成すように交差して配置される。これにより、接続プラグと開口部内に堆積される導電膜との電気的接続信頼性を向上させることが可能となる。

(もっと読む)

半導体集積回路

【課題】セルアレイの大容量化と信頼性向上に有効なレイアウトを提案する。

【解決手段】本発明の例に関わる半導体集積回路は、セルアレイ11と、セルアレイ11上に配置されるライン&スペースのパターンを有する導電線WL11,・・・WL1nと、導電線WL11,・・・WL1nよりも上に形成される引き出し線L11,・・・L1nと、導電線WL11,・・・WL1nと引き出し線L11,・・・L1nとを接続するコンタクトホールCS11,・・・CS1nとを備え、導電線WL11,・・・WL1nの一端は、導電線WL11,・・・WL1nのうちの一つから他の一つに向かうに従って、順次、セルアレイ11の端部から離れていく。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

半導体装置の製造方法

【課題】隣接開孔との短絡を防止する。また、開孔下部の開孔径を大きくすることにより、容量の低下を引き起こすことなく安定したストレージノードを形成する。

【解決手段】異方性エッチングを行うことにより第2の絶縁膜中にボーイング形状が発生しない深さまで第2の開孔を形成する工程と、第1及び第2の開孔の側面に第4の膜を形成する工程と、異方性エッチングを行うことにより、第1の絶縁膜が露出するまで第2の開孔を伸長させてアスペクト比が12を越える第2の開孔を形成する工程と、第2の開孔の第4の膜が形成されていない側面部分を等方性エッチングにより拡張する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置とその製造方法

【課題】MISトランジスタを有する半導体装置において、微細化及び製造歩留りの向上を実現する。

【解決手段】半導体装置は、基板101上にゲート絶縁膜103を介して形成されたゲート電極117と、基板101におけるゲート電極117の両側に形成されたソース領域及びドレイン領域107bとを有するMISトランジスタを備え、ゲート電極117は金属シリサイドからなり、ソース領域及びドレイン領域107bの少なくとも一方の上に、金属シリサイドからなる第1のコンタクト電極116を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間または配線とプラグとの間の抵抗を低減しつつストレスマイグレーション耐性、エレクトロマイグレーション耐性を確保できる配線構造を提供する。

【解決手段】層間絶縁膜101及びCu膜104を有する配線105上に層間絶縁膜107を形成し、層間絶縁膜107にビア109及びトレンチ108を形成し、Cu膜104を露出させる。次に、Cu膜104にビア109よりも内径の大きい凹部110を形成した後、バリア金属膜111を形成する。次いで、バリア金属膜111をリスパッタすることで凹部110にバリアメタル金属膜111を埋め込むとともに、角に丸みを帯びた下凸な形状を有するビア112を形成する。次に、ビア112及びトレンチ108にバリア金属膜113、Cu膜114を順次形成する。次いで、Cu膜114、バリア金属膜113及びバリア金属膜111を除去する。

(もっと読む)

逆ソース/ドレイン金属コンタクトを有する電界効果トランジスタ(FET)及びその製造方法

【課題】 コンタクト間隔及び寄生容量の問題に対する解決策を提供する、改善されたFET設計を構築する。

【解決手段】 本発明は、下方の第1の誘電体層内に配置された下部と上方の第2の誘電体層内に配置された上部とを有する逆ソース/ドレイン金属コンタクトを含む電界効果トランジスタ(FET)に関する。逆ソース/ドレイン金属コンタクトの下部は、上部より大きい断面積を有する。好ましくは、逆ソース/ドレイン金属コンタクトの下部は、約0.03μm2から約3.15μm2の範囲の断面積を有し、こうした逆ソース/ドレイン金属コンタクトは、約0.001μmから約5μmの範囲の距離だけ、FETのゲート電極から間隔を空けて配置される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】貫通孔の信頼性が低下することを抑制できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置100は、半導体チップ10と、スルーホール105,・・・とを備える。半導体チップ10は、表面10aと裏面10bとを有する。表面10aは、第1軸CAに略垂直に延びており素子が形成される。第1軸CAは、体積中心VCを通る。裏面10bは、第1軸CAに略垂直に延びており表面10aと反対側の面である。スルーホール105,・・・は、半導体チップ10の周辺部の付近において、表面10aから裏面10bへ向かうに従って第1軸CAに近づくように貫通して形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】裏面のグランド層を容易に形成するとともに、ビアホールを位置合わせが容易に形成する。

【解決手段】ウェハ1の半導体集積回路が形成されている側の表面11に形成された第1のホール2と、ウェハ1の裏面12に形成された第2のホール3とを有し、1個の第2のホール3と複数個の第1のホール2とがつながってウェハ1を貫通するビアホール4が構成され、ビアホール4には埋め込み金属層5が埋め込まれ、ウェハ1の裏面12の全体にはグランド層6が形成されている。

(もっと読む)

161 - 180 / 217

[ Back to top ]