Fターム[5F033NN30]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | 断面が長方形以外 (728)

Fターム[5F033NN30]の下位に属するFターム

上部を拡大、コンタクトパッド (511)

Fターム[5F033NN30]に分類される特許

101 - 120 / 217

半導体装置及びその製造方法

【課題】横型絶縁ゲートトランジスタ素子を備え、オン抵抗の増加を抑制しつつ体格を小型化することのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体層に構成されたLDMOS素子と、半導体層の主表面上に形成された絶縁膜を同一表面から貫通するコンタクプラグとしての、ソース領域とベースコンタクト領域とに接続された第1コンタクトプラグと、を備えた半導体装置であって、ベースコンタクト領域が、半導体層の主表面に略垂直な方向においてソース領域よりも主表面に対して下方で、半導体層の主表面に沿う方向においてソース領域と少なくとも一部が重なる位置に形成されている。そして、第1コンタクトプラグが、絶縁膜及びソース領域を貫通しつつベースコンタクト領域まで延設されている。

(もっと読む)

半導体装置及びその製造方法

【課題】導電パターンと貫通電極の間の抵抗を低くし、かつ貫通電極と裏面電極であるバンプを一体に形成することができる半導体装置を提供する。

【解決手段】この半導体装置において、貫通孔102は、基板100に形成され、導電パターン120の下に位置している。絶縁層110は、貫通孔102の底面に位置している。導電パターン120は、基板100の一面側に位置している。開口パターン112は、貫通孔102と導電パターン120の間に位置する絶縁層110に形成されており、周から貫通孔102の中心軸までの距離r3が貫通孔102における距離r1より小さい。開口パターン112が設けられることにより、貫通孔102の底面に導電パターン120が露出している。バンプ302は、基板100の裏面側に位置しており、貫通電極300と一体に形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、絶縁膜のホール内に形成される導電性プラグ等の導電性材料のコンタクト抵抗が基板面内でばらつくのを防止すること。

【解決手段】シリコン基板30の上方に第1の層間絶縁膜45を形成する工程と、第1の層間絶縁膜45の上方に強誘電体キャパシタQを形成する工程と、強誘電体キャパシタQの上方に、水素バリア絶縁膜55、57、62と第2の層間絶縁膜58とを有する積層膜を形成する工程と、エッチングにより積層膜にホール58b、58cを形成する工程と、ホール58b、58c内に金属配線(導電性材料)69を埋め込む工程とを有し、ホール58b、58cを形成する工程において、水素バリア絶縁膜55、57、62のエッチングを、第2の層間絶縁膜58のエッチングとは異なるエッチング手法で行う半導体装置の製造方法による。

(もっと読む)

半導体貫通電極形成方法

【課題】半導体ICの表面から裏面に電極経路を形成する貫通電極形成方法において、界面での導電性材料の剥がれ等の機械的不良や、絶縁不良,導通不良等の電気的不良を抑制することを目的とする。

【解決手段】貫通孔に樹脂材料を形成する際に、貫通孔底部に電極PAD102を形成し、インクジェット方法により貫通孔の周囲に絶縁材料104を中心部に導電性材料105を形成し、さらに、インクジェット吐出樹脂を表面に凹凸が形成されるように吐出することにより、絶縁材料104と導電性材料105との密着性、および絶縁性材料104と貫通孔内壁との密着性を向上することができるため、界面での導電性材料105の剥がれ等の機械的不良や、絶縁不良,導通不良等の電気的不良を抑制することができる。

(もっと読む)

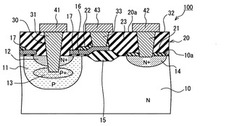

トランジスタ、半導体装置及びその製造方法

【課題】トレンチゲート型トランジスタのオン抵抗とプレーナ型トランジスタの耐圧とを同時に最適化する。

【解決手段】半導体基板10上に、半導体層16A、16Bがエピタキシャル成長により形成される。第1の領域において第1の埋め込み層12が形成され、第2の領域において第2の埋め込み層13が形成される。第1の埋め込み層12はN+型の第1の不純物層12Aと、それより広い範囲に拡散されたN型の第2の不純物層12Bとによって形成される。第2の埋め込み層13はN+型の不純物層のみで形成される。第1の領域において半導体層16Aの表面からN型の第3の不純物層18が深く拡散される。第1の領域にはトレンチゲート型トランジスタが形成され、第2の領域にはプレーナ型トランジスタが形成される。

(もっと読む)

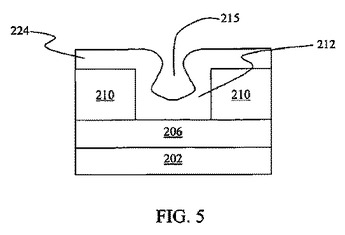

配線構造の製造方法、並びに表示装置及びその製造方法

【課題】CMP法を用いずに、配線部26とコンタクト部25とを同時に形成する。

【解決手段】コンタクトホール27及び配線溝28を形成した層間絶縁膜23の表面に第2膜24を上記各表面に沿って所定の厚みで形成することにより、コンタクトホール27内の第2膜24によって穴部31を形成すると共に、配線溝28内の第2膜24によって溝部32を形成する。次に、穴部31及び溝部32の開口端を塞ぐように、レジストを第2膜24上に形成した後に、エッチバックにより穴部31及び溝部32の周囲で露出した第2膜24をエッチングして除去し、コンタクトホール27にコンタクト部25を形成すると共に、配線溝28に配線部26を形成する。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 コンタクトプラグの凸形状部の電界集中による絶縁破壊を抑制したViaパターンを有する半導体装置を提供する。

【解決手段】 第一の配線層1及び第一の絶縁層2上に形成された層間絶縁膜3と、層間絶縁膜3内に第一の配線層1との接続部から上方にいくにつれて断面形状が大きくなるように形成された接続孔4と、接続孔4の側壁全面に所定の深さから上方にいくにつれて膜厚が大きくなるように連続的にスペーサ膜5と、スペーサ膜5の内側に第一の配線層1と電気的に接続されるコンタクトプラグ7と、コンタクトプラグ7上に形成され、コンタクトプラグと電気的に接続された第二の配線層8と、第二の絶縁層9とを有する半導体装置。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】シリコンエピタキシャル層と配線材料との間でショートが発生しない半導体装置の製造方法、コンタクトプラグの形成においてコンタクトホールの径の拡大を抑制する半導体装置の製造方法、これらの目的を効果的に達成できる半導体製造装置を提供する。

【解決手段】シリコン表面に形成された第1の酸化シリコン膜2と、第1の酸化シリコン膜2とは形成方法の異なる第2の酸化シリコン膜3とを有し、各々の酸化シリコン膜2,3の少なくとも一部が露出して共存するシリコン基板1を前処理する前処理工程を備えた半導体装置の製造方法であって、前記前処理工程は、第1の酸化シリコン膜2を除去して前記シリコン表面を露出させるエッチング工程を有し、前記エッチング工程は、第1の酸化シリコン膜2と第2の酸化シリコン膜3とを同じエッチングレートでエッチングすることを特徴とする。

(もっと読む)

半導体チップ及び半導体装置

【課題】小型化が可能な半導体チップ及び半導体装置を提供する。

【解決手段】上面、底面、及びこれらの面を接続する側面13を有する半導体基板11と、上面にあり、半導体基板11に形成された半導体素子と接続された上部配線15と、底面にあり、側面13で囲まれた内側に側面13から離間して配置された複数の接続端子26と、半導体基板11を貫通する貫通孔21を通り、上部配線15と接続端子26とを電気接続する貫通配線25と、接続端子26間の底面にあり、接続端子26とは凹部31を隔てて配置された絶縁性の分離膜27とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置70には、積層形成される配線膜6及び10から構成される配線層が設けられる。キャップ膜3上に形成される層間絶縁膜4の第1の開口部には、配線膜6が埋設される。配線膜6の底部及び側面部にはバリアメタル膜5が設けられる。層間絶縁膜4及び配線膜6上に形成されるキャップ膜7及び層間絶縁膜8の第2の開口部には、配線膜10が埋設される。配線膜10の底部及び側面部にはバリアメタル膜9が設けられる。層間絶縁膜8及び配線膜10上に形成される。配線膜10は配線膜6上に設けられ、配線膜10の端部は配線層6の端部よりも内側に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】バリア膜を薄くする場合であっても良好なバリア性を確保し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の導電体32と、半導体基板上及び第1の導電体上に形成され、第1の導電体に達するコンタクトホール52と、コンタクトホールの上部に接続された溝54とが形成された、酸素を含む絶縁膜48と、コンタクトホールの側面並びに溝の側面及び底面に形成された酸化ジルコニウム膜62と、コンタクトホール内及び溝内における酸化ジルコニウム膜上に形成されたジルコニウム膜64と、コンタクトホール内及び溝内に埋め込まれたCuより第2の導電体70とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留りが高く且つ配線間容量を十分に低減でき、且つ機械的強度を十分に得られるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の配線105と、第1の層間絶縁膜101に複数の配線105の少なくとも1つと接続するように形成されたビア113及びダミービア106とを有している。第1の層間絶縁膜101における互いに隣り合う配線105同士の間には空隙部109が選択的に形成されており、ダミービア106は、空隙部109と接する配線105Aの下側に該配線105Aと接続して形成され、ビア113及びダミービア106は、空隙部109を介することなく第1の層間絶縁膜101により周囲を覆われている。

(もっと読む)

半導体装置およびその製造方法

【課題】ビット線間の間隔が狭くなった場合の配線間ショートに対するマージンや耐圧を確保する。

【解決手段】隣接配置される選択ゲートトランジスタのコンタクトプラグを、第1および第2のコンタクトプラグ4、5として交互に配置した構成とし、配線層を2層にして下層側を第1の配線層6、上層を第2の配線層7として形成する。第1のコンタクトプラグ4を第1の配線層6にヴィアプラグ13を介して接続し、第2のコンタクトプラグ5をヴィアプラグ13、16を介して第2の配線層7に接続する構成とする。第1の配線層6、第2の配線層7が共にコンタクトプラグのピッチの倍のピッチで配置できる。ショート不良、耐圧不良、リーク不良、配線間容量の増大を防止できる。

(もっと読む)

半導体装置およびフォトマスク

【課題】シェアードコンタクトホールの開口不良を抑制できる半導体装置およびフォトマスクを提供する。

【解決手段】シェアードコンタクトホールSC1、SC2は、ゲート電極層GE1、GE2とドレイン領域PIRとの双方に達している。平面視において、ゲート電極層GE1、GE2の一方側壁E2が、一方側壁E1の仮想延長線E1aよりも他方側壁E4側にずれて位置している。平面視において、ゲート電極層GE1、GE2のシェアードコンタクトホールSC1、SC2が達する部分の線幅D1の中心線(C2−C2)が、ゲート電極層GE1、GE2のチャネル形成領域CHN1、CHN2上に位置する部分の線幅D2の中心線(C1−C1)に対してずれて位置している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、コンタクトプラグの高抵抗化を抑制することができ、また当該コンタクトプラグの構成材料のソース・ドレイン領域への拡散が起こらず、かつ簡略な製造プロセスにより作製可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ゲート電極4、第一の層間絶縁膜7、第一のコンタクトプラグ8、第二の層間絶縁膜9および第二のコンタクトプラグ10を有する。第一の層間絶縁膜7の上面は、ゲート電極4の上面と同じ高さ位置である。第一のコンタクトプラグ8は、第一の層間絶縁膜7の膜厚方向に貫通して形成され、下面においてソース・ドレイン領域5と電気的に接続され、第一の電気抵抗率を有する。第二のコンタクトプラグ10は、第二の層間絶縁膜9の膜厚方向に貫通して形成され、下面において第一のコンタクトプラグ8の上面と電気的に接続され、第一の電気抵抗率より低い第二の電気抵抗率を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトプラグの上部に形成するヴィアプラグを形成する場合に、ヴィアホールの上端開口をシュリンクさせるスペーサを設けるときの不具合を解消する。

【解決手段】NANDフラッシュメモリのメモリセル領域は、シリコン基板1がSTI2により活性領域3に分離形成されている。一対の選択ゲート線の間にシリコン酸化膜4に千鳥配置されたコンタクトプラグ6が形成されている。コンタクトプラグ4の上部にはボイドに起因した凹部6aが発生している。上部のシリコン酸化膜7にヴィアプラグ10が形成され、この凹部6aの形状に対応した凸部10aにより電気的に良好に接触した状態となっている。ヴィアホール8の上端開口部はスペーサ9により径がシュリンクされている。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の導電層を電気的に接続するコンタクト部の近傍におけるリーク電流を効果的に抑制可能な半導体装置を提供する。

【解決手段】半導体基板1の主表面に形成され、低濃度不純物領域5bと高濃度不純物領域5aとを有する不純物領域と、低濃度不純物領域5bと隣り合う位置の上記主表面上に形成されたゲート電極4と、ゲート電極4の一方の側壁上に形成されたサイドウォール絶縁膜12a,12bと、低濃度不純物領域5b上からゲート電極4の他方の側壁上に延在し高さの低いサイドウォール絶縁膜12a,12bと、この高さの低いサイドウォール絶縁膜12a,12bと低濃度不純物領域5bとを覆いゲート電極4の他方の側壁に達するシリコン窒化膜9aと、シリコン窒化膜9aを覆うように形成され上記不純物領域とゲート電極4との双方と電気的に接続されたプラグ11とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 第1の導電体と第2の導電体とのショートを防止することができる半導体装置を提供する。

【解決手段】 半導体装置は、半導体基板上における複数の第1の導電体上に形成された中間絶縁膜と、中間絶縁膜に形成されかつ複数の第1の導電体上に位置する複数のコンタクトホールと、複数のコンタクトホール内にそれぞれに埋め込まれた複数のコンタクトプラグと、中間絶縁膜上の複数のコンタクトプラグそれぞれの上に形成されかつコンタクトプラグを介して複数の第1の導電体に電気的に接続された複数の第2の導電体と、を有する半導体装置であって、半導体基板には、複数の第1の導電体およびコンタクトプラグを第1の密度で有する第1の素子領域と、第1の素子領域の周囲に近接され複数の第1の導電体およびコンタクトプラグを第1の素子領域より低い第2の密度で有する第2の素子領域と、が形成されていること、第1の素子領域は、コンタクトプラグが中間絶縁膜の途中で終端して埋設された第2の素子領域に近接する最外周領域を有する。

(もっと読む)

基板装置及びその製造方法並びに表示装置

【課題】単一層からなるパターン膜の側面部から不要な他の膜残渣を確実に除去する。

【解決手段】基板上に形成され、側面部を有すると共に単一層からなるパターン膜を備え、側面部は、基板の表面に対して複数の傾斜角度を有するように形成され、又は段差状に形成されている。

(もっと読む)

101 - 120 / 217

[ Back to top ]