Fターム[5F033QQ26]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287)

Fターム[5F033QQ26]の下位に属するFターム

導電膜 (467)

絶縁膜 (1,171)

多層レジスト (195)

エッチング後も残存させるもの (194)

Fターム[5F033QQ26]に分類される特許

201 - 220 / 260

半導体装置の製造方法。

【課題】半導体装置の生産性および製品の歩留まりが向上する半導体装置の製造方法を提供する。

【解決手段】本発明によれば、フォトマスクとして、マスクパターンを分割して得られる第1矩形パターン104aを有する第1フォトマスク106、および前記マスクパターンを分割して得られる第2矩形パターン104bを有する第2フォトマスク108を用いて半導体装置を製造する。半導体装置を製造する際には、第1フォトマスク106を用いて、半導体基板上の犠牲膜を第1矩形パターン104aに加工する第1の工程、第2フォトマスク108を用いて、前記犠牲膜を第2矩形パターン104bに加工する第2の工程、および第1の矩形パターン104aおよび第2の矩形パターン104bに加工された前記犠牲膜をマスクとして、半導体基板上に形成された膜をエッチングする第3の工程、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ニッケルシリサイドのパターニングを精度よく行なうことのできる半導体装置の製造方法と半導体装置を提供する。

【解決手段】半導体基板1の主表面に絶縁膜、ポリシリコン膜およびニッケル層が形成される。ランプアニール処理を施すことにより、ニッケルシリサイド層が形成され、未反応のニッケル層が除去されて、ニッケルシリサイド層上にハードマスク9が形成される。ハードマスク9をマスクとして、NH3とCOとを含むガスを用いた異方性のプラズマエッチングと、Cl2ガスを用いた異方性のプラズマエッチングとを交互に行なうことによって、ゲート電極となるニッケルシリサイド層8aおよびポリシリコン膜5aが形成される。その後、ソース・ドレイン領域が形成され、そのソース・ドレイン領域にニッケルシリサイド層がそれぞれ形成される。

(もっと読む)

構造の作製方法

金層(20)が金酸化物マスク(30)でパターニングされる。前記マスクは、酸によってパターニングされ、好適にはマイクロコンタクトプリントによってパターニングされる。金酸化物マスク(30)は、金層(20)用のアルカリエッチング溶液中で安定である。金酸化物マスク(30)は、再曝露可能な金パッド(20)を形成するように維持されて良い。  (もっと読む)

(もっと読む)

半導体ウエハ上に設けられた配線ラインに付随する電気的分離の形成方法

【課題】半導体基板上の配線ラインの形成及び配線ラインに付随する電気的分離の形成方法を提供する。

【解決手段】複数の配線ライン16を基板表面の上に形成すること、および前記配線ライン16の上に、第1層48の下であって隣りあう配線間には、空気が満たされ空隙を設けるように、非晶質炭素である第1層48をプラズマ助長化学気相(PECVD)により形成すること、を含む。また、空間内に空気で満たされた空隙23を生じさせるために、OSG(有機シリコンガラス)やFSG(フッ素ドープシリコンガラス)を形成することができる。炭素、OSG,FSG層は、IMD層(ライン間の分離)として使用される。ILD層(レベル間の分離)を形成するために、さらなる絶縁物質層を加えてもよい。

(もっと読む)

半導体装置およびその製造方法

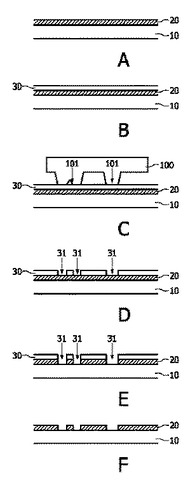

【課題】回路の集積化が容易な大型の半導体装置およびその製造方法を提供する。

【解決手段】基板100上に回路用パターンが形成されている半導体装置の製造方法であって、回路用パターンを形成する工程は、基板100上の第1の領域101に第1のマスク10を介した露光により第1のパターン11を形成する工程と、第1の領域に隣接する第2の領域102に第2のマスク20を介した露光により第2のパターン21を形成する工程と、第1の領域と第2の領域との境界領域112に第3のマスク30を介した露光により第3のパターン31を第1のパターン11と第2のパターン21とを繋ぎ合わせるように形成する工程を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法、パターン補正方法およびプログラム

【課題】 エッチング工程時で生じる加工変換差を小さくことができる半導体装置の製造方法を提供すること。

【解決手段】 半導体装置の製造方法は、被加工膜1上にパターンを含むレジストパターン2Pを形成する工程と、前記パターンのサイズを変更する工程と、前記パターンのサイズを変更した前記レジストパターン2Pをマスクにして前記被加工膜1をエッチングする工程とを含み、前記パターンのサイズを変更する工程は、前記被加工膜1をエッチングする工程により形成される、前記パターンに対応した前記被加工膜1からなるパターンが、所望の寸法を有するように、前記パターンのサイズの変更量を決める。

(もっと読む)

パターン形成方法及び薄膜トランジスタの製造方法

【課題】フォトリソ工程を簡便に削減できるパター形成方法を考案し、液晶表示装置の製造工程を大幅に削減できるTFTの新しい製造方法を提供する。

【解決手段】TFTを構成する材料膜を絶縁膜基板上に積層して成膜してから、膜厚が互いに異なる複数の領域を有するレジストマスクを上記材料膜の最上層にパターニングして形成する。そして、このレジストマスクを用いたリフトオフの方法で導電体膜のパターン形成を行う。あるいは、別に形成した膜厚が互いに異なる複数の領域を有するレジストマスクをエッチングマスクにして積層した材料膜のうち複数の材料膜を順次に加工する。このような新規なパターン形成方法および加工方法により、従来の技術で5回のフォトリソ工程で製造していた液晶表示装置を2回あるいは3回のフォトリソ工程で製造する。

(もっと読む)

半導体装置およびその作製方法

【課題】幅の異なるLDD領域を自己整合的に形成し、それらの幅を個々の回路に応じて精密に制御する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いることによって、ゲート電極の膜厚の薄い領域の幅を自由に設定でき、そのゲート電極をマスクとして自己整合的に形成できる2つのLDD領域の幅を個々の回路に応じて異ならせることができる。なお、一つのTFTにおいて、幅の異なる2つのLDD領域は、両方ともゲート電極と重なる構造である。

(もっと読む)

半導体装置およびその作製方法

【課題】液晶表示装置やEL発光装置などの半導体装置において、今後のさらなる高精細化(画素数の増大)、小型化に伴う各表示画素ピッチの微細化、及び画素部を駆動する駆動回路の集積化を進められるように、複数の素子を限られた面積に形成し、素子が占める面積を縮小して集積することを課題とする。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して複雑なゲート電極を形成する。また、マスクを変更するだけで、工程数を増やすことなく、同一基板上に上記マルチゲート構造であるトップゲート型TFTとシングルゲート構造であるトップゲート型TFTを形成することができる。

(もっと読む)

クリティカルディメンション低減およびピッチ低減のためのシステムおよび方法

【解決手段】形状を形成する方法は、下層の上に第1の材料のマスクを形成する工程を備え、マスクは、不適切なプロファイルを有する。マスクのプロファイルは補正され、形状が下層に形成される。形状を形成するためのシステムも開示されている。 (もっと読む)

半導体装置の製造方法

【課題】 層間絶縁膜に与えるダメージが抑制された、半導体装置の製造方法を提供する。

【解決手段】 第1の絶縁層に埋設される、導電材料よりなる配線構造を形成する配線構造形成工程と、前記第1の絶縁層を除去して前記配線構造を露出させる絶縁層除去工程と、

前記配線構造を埋めるように第2の絶縁層を形成する絶縁層埋設工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

小さく、スペースの狭い構成物の配列を形成する方法

集積回路に用いるための、小さく高密度に間隔をあけた孔もしくは支柱の配列を形成するための方法を開示する。高密度に充填された構成物を形成するために、様々なパターン転写ステップ、および、エッチングステップを、ピッチ減少化技術と組み合わせて用いることができる。一つの層に統合することができる、交差し引き伸ばされた構成物のピッチが減少しているパターンの重ね合わせたものを形成するために、従来のフォトリソグラフィーステップをピッチ減少化技術と組み合わせて用いることができる。 (もっと読む)

表示装置、及び表示装置の作製方法

【課題】信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】一導電型の不純物領域を含む半導体層と、半導体層上にゲート絶縁層と、ゲート電極層と、一導電型の不純物領域と接する配線層と、ゲート絶縁層上に設けられ、配線層と接する導電層と、導電層と接する第1の電極層と、第1の電極層上に電界発光層と、第2の電極層とを有し、配線層は導電層を介して第1の電極層と電気的に接続している。

(もっと読む)

半導体装置の製造方法

【課題】所望する微細な加工形状を得るための半導体装置の製造方法を提供する。

【解決手段】ナイトライド膜103及びレジストパターン104を覆うアモルファスカーボン膜にスパッタリングを行って、レジストパターン104の側壁上にアモルファスカーボン膜106を形成する。レジストパターン104とアモルファスカーボン膜106とをマスクにして、シリコン基板上101、酸化膜102及びナイトライド膜103をパターニングする。

(もっと読む)

半導体装置及びその作製方法

【課題】LDD領域を有する微細TFTを、工程数の少ないプロセスで作製し、各回路に応じた構造のTFTを作り分けることを課題とする。また、LDD領域を有する微細TFTであってもオン電流を確保することを課題とする。

【解決手段】ゲート電極を2層とし、下層のゲート電極のゲート長を上層のゲート電極のゲート長よりも長くし、ハットシェイプ型のゲート電極を形成する。この際に、レジストの後退幅を利用して上層のゲート電極のみをエッチングし、ハットシェイプ型のゲート電極を形成する。また、配線と半導体膜のコンタクト部をシリサイド化し、コンタクト抵抗を下げる。

(もっと読む)

レジストパターン厚肉化材料、レジストパターンの形成方法、及び半導体装置の製造方法

【課題】レジストパターンのパターニング時に既存の露光装置におけるArFエキシマレーザー光等の光源をそのまま使用可能であり量産性に優れ、レジスト抜けパターンを前記光源の露光限界を超えて微細に形成可能なレジストパターンの形成方法、半導体装置の製造方法等の提供。

【解決手段】本発明のレジストパターンの形成方法は、レジストパターンを形成後、該レジストパターンの表面を覆うように、樹脂と界面活性剤とを含有するレジストパターン厚肉化材料を塗布し、該レジストパターンを厚肉化した厚肉化レジストパターンを形成することを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 エアーギャップ構造を利用したデュアルダマシン構造を有する半導体装置の製造方法を提供する。

【解決手段】 基体上にSi犠牲膜420を堆積し、このSi犠牲膜に下層配線用の溝を形成した後、この配線溝に導電性材料を埋め込み下層配線260とする。この下層配線と前記Si犠牲膜上に多孔質low−k膜280とSi犠牲膜424を順次堆積した後、これらの膜を貫通する開口部と、Si犠牲膜424には上層配線用の溝とを形成し、前記開口部と配線溝に導電性材料を堆積させ上層配線262とする。この後Si犠牲膜420、424をエッチングで除去し、エアーギャップ311,313を形成する。

(もっと読む)

回路基板の製造方法、回路基板及び電子表示装置

【課題】 少ない枚数のフォトマスクで回路形成を行うことができ、生産性の向上を図ることが可能な回路基板の製造方法を提供する。

【解決手段】 下層導電部と上層導電部とが絶縁層を介して積層され、かつ絶縁層の貫通孔内及び上層導電部の開口部内に形成された配線を介して接続された構造を基板上に有する回路基板の製造方法であって、基板上に下層導電部、絶縁層及び上層導電膜を順次形成する工程と、上層導電膜上に、上層導電部間形成領域で上層導電部形成領域よりも膜厚が小さく、かつ上層導電部の開口部形成領域に開口部を有するフォトレジスト膜を形成する工程と、フォトレジスト膜の開口部領域内の上層導電膜及び絶縁層を除去して貫通孔を形成する工程と、貫通孔内に配線を形成する工程と、上層導電部間形成領域のフォトレジスト膜を除去する工程と、上層導電部間形成領域の上層導電膜を除去して上層導電部を形成する工程とを含む回路基板の製造方法。

(もっと読む)

プラズマ酸化および酸化材料の除去

【課題】プラズマ酸化および酸化材料の除去

【解決手段】導電層をエッチングする方法は、導電層の少なくとも一部を転換し、導電層の転換部分を実質的に除去し、残存表面を露出させるために、導電層をエッチングすることを含む。残存表面は、約10nm未満の平均表面粗さを有する。導電層をエッチングするための方法も開示される。

(もっと読む)

微細パターン形成方法

【課題】

微細加工が可能な微細パターン形成方法を提供する。

【解決手段】

パターニングされたマスク層76の側壁にプラズマ反応生成物を堆積させてマスク層76のパターン幅を広げる第1工程と,パターン幅が広げられたマスク層76をマスクとして,第1の被エッチング層74をエッチングする第2工程と,エッチングされた第1の被エッチング層74に生じたスペース80にマスク材81を埋め込む第3工程と,スペース80に埋め込まれたマスク材を残して,第1の被エッチング層74をエッチングする第4工程と,残されたマスク材81をマスクとして,第2の被エッチング層72をエッチングする第5工程とを有することを特徴とする,微細パターン形成方法である。

(もっと読む)

201 - 220 / 260

[ Back to top ]