Fターム[5F033QQ26]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287)

Fターム[5F033QQ26]の下位に属するFターム

導電膜 (467)

絶縁膜 (1,171)

多層レジスト (195)

エッチング後も残存させるもの (194)

Fターム[5F033QQ26]に分類される特許

241 - 260 / 260

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等を、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】導電層を有する基板に対して裏面からの光照射によって、選択的に基板表面を改質し、ぬれ性を制御する。改質された表面上に、導電性材料又は絶縁性材料を吐出(噴出なども含む)などによって、付着させ、導電層、絶縁層を形成する。また、光触媒物質の光吸収、エネルギー放射作用によって、光による処理効率を向上させることができる。また、導電層上にも選択的にマスク層を形成し、非照射領域である導電層上の領域のぬれ性も制御する。

(もっと読む)

プラズマエッチングのパフォーマンスを改善する方法

【課題】 エッチングマスクを通して層内にフィーチャをエッチングする方法を提供する。

【解決手段】 前記エッチングマスクの曝露された表面、および前記フィーチャの垂直側壁上に保護コーティングが保護膜形成ガス混合物で形成される。前記フィーチャは、前記エッチングマスクを通して、少なくとも1つのエッチング化学物質および少なくとも1つの保護膜形成化学物質を含む反応性エッチング混合物でエッチングされる。  (もっと読む)

(もっと読む)

マスク、マスクの製造方法及び半導体装置の製造方法

【目的】 CMP法を用いないで形成される上層配線の加工不良の発生率を低減し、上層配線の上にさらなる上層配線を形成した場合に、ビアプラグの形成不良を低減することができるマスクの製造方法、マスク及び半導体装置の製造方法を提供する。

【解決手段】 上層配線レイアウト変更工程で下層配線レイアウトデータ取得工程及び第1の上層配線レイアウトデータ取得工程により取得される下層配線のレイアウトデータと、第1の上層配線のレイアウトデータを基にして配線重複領域データ取得工程により取得される上層配線が下層配線と略平行に重複する配線重複領域データと、プロセス条件データ取得工程により取得される多層配線を形成するためのプロセス条件データに基づいて、配線重複領域内の上層配線のレイアウトデータを変更して第2の上層配線レイアウトを第1の上層配線よりも良好な第2の上層配線を形成する第2の上層配線レイアウトデータを取得する。

(もっと読む)

パターン形成構造、パターン形成方法、デバイス及び電気光学装置、電子機器

【課題】 パターン形成時に、微細パターンと他のパターンとの各々の高さを同じくすることにより、上記パターン上を含む領域を平坦にするバンク構造体、パターン形成方法、及び電気光学装置、電子機器を提供する。

【解決手段】 機能液により形成するパターンに対応した凹部が設けられた隔壁構造体であって、第1パターンに対応して隔壁34に設けられた第1凹部55と、第1パターンに接続され、かつ、第1パターンよりも幅が狭い第2パターンに対応して隔壁34に設けられた第2凹部56と、を含み、第2凹部56の底面の高さが、第1凹部55の底面の高さよりも高く設けられていることを特徴とする。

(もっと読む)

レジスト除去方法

【課題】 低誘電率絶縁膜の比誘電率の増加を防止すると共にレジスト残渣を生じさせないレジスト除去を可能にする。

【解決手段】 レジストマスクをエッチングマスクにして、被処理基板上の有機成分含有の層間絶縁膜をRIEで加工した後(S1、S2)、上記レジストマスクを除去するために、はじめに、第1の温度下において水素ラジカル照射をして(S3)、レジストマスク表面に形成されている変質層を水素化分解する改質層に変換する(S4)。その後、第1の温度より高い第2の温度下において水素ラジカル照射を行い(S5)、上記改質層およびレジストマスクをアッシング除去する(S6)。このようにして、上記層間絶縁膜の組成変化およびその比誘電率の増加がなく、しかもレジスト残渣の生じないレジスト除去が可能になる。

(もっと読む)

ピッチ増倍を使用する集積回路の製造方法

周辺回路100のアレイ102及び周辺104の異なるサイズのフィーチャーが1つのステップで基板110上にパターン化される。特に、独立に形成された2つのパターン177、230を組合せた混合パターンが、一つのマスク層160上に形成され、次に、下の基板(110)に転写される。独立に形成されたパターンのうち第1パターン177はピッチ増倍によって形成され、独立に形成されたパターンのうち第2パターン230は従来のフォトリソグラフィによって形成される。第1パターン177は、第2パターン230の形成に使用されたフォトリソグラフィ法の解像度以下のフィーチャー175を含む。これらのラインは、フォトレジスト上にパターンを形成し、そしてそのパターンを非晶質炭素層にエッチングすることによって製作される。非晶質炭素のエッチングされていない部分の幅より小さい幅を有する側壁スペーサー175は、前記非晶質炭素の側壁上に形成される。その後、非晶質炭素は除去されて、側壁スペーサー175を残してマスクパターン177を形成する。従って、スペーサー175は、フォトレジスト上にパターンを形成するために使用されたフォトリソグラフィ方法の解像度より小さいフィーチャーサイズを有するマスク177を形成する。保護物質200がスペーサー175のまわりに形成される。スペーサーは175さらに、ハードマスク210を用いることにより保護され、そして次にフォトレジスト220がハードマスク210上に形成されパターン化される。フォトレジストパターン230はハードマスク(210)を通じて保護物質200に転写される。その後、スペーサー175及び保護物質200によって作成されたパターン177、230の組合せは、下の非晶質炭素ハードマスク層160に転写される。その後、異なるサイズのフィーチャーを有する組合せパターンは下の基板110に転写される。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 薄膜トランジスタ表示板の製造工程を簡素化する。また、画素電極の断線を防止できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】 本発明の一実施形態による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成する段階と、前記ゲート線上にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上に半導体層を形成する段階と、前記半導体層上にオーミック接触部材を形成する段階と、前記オーミック接触部材上にデータ線及びドレイン電極を形成する段階と、前記データ線及び前記ドレイン電極上に保護膜を蒸着する段階と、前記保護膜上に第1感光膜を形成する段階と、前記第1感光膜をマスクとして前記ゲート絶縁膜及び前記保護膜をエッチングすることによって、前記ドレイン電極の少なくとも一部と前記基板の少なくとも一部を露出させる段階と、導電体膜を蒸着する段階と、並びに前記第1感光膜を除去し、前記ドレイン電極の露出した部分上に画素電極を形成する段階とを含む。

(もっと読む)

薄膜トランジスタアレイ基板及びその製造方法

【課題】 アルミを含んだ上層と下層金属層との積層から加工されるドレイン電極は反射電極を兼ねており、しかも、ドレイン電極と画素電極とのコンタクト抵抗が低い薄膜トランジスタを備えた薄膜トランジスタアレイ基板をマスク枚数を追加することなく提供する。

【解決手段】 下層の金属膜と上層のアルミ膜の積層構造をなすドレイン電極の露光時に一部領域のみ露光量を変えることによりレジスト厚が他よりも薄い領域を形成した後に、通常どおりのパターニングを行う。その後、該領域のレジストを完全に除去し、露出したアルミ膜のみ選択エッチング除去する。ドレイン電極上の層間絶縁膜に形成するコンタクトホールを該領域に設け、該コンタクトホールを介して画素電極と電気的に接続させる。

(もっと読む)

非結晶性炭素膜を犠牲ハードマスクとして用いる半導体素子の製造方法

【課題】 本発明は、犠牲ハードマスクのエッチング選択比を増加させ、パターン変形を最小化できる半導体素子の製造方法を提供すること。

【解決手段】 本発明は、被エッチング層上に犠牲ハードマスク用の非結晶性炭素膜を形成するステップと、該犠牲ハードマスク用の非結晶性炭素膜上にフォトレジストパターンを形成するステップと、該フォトレジストパターンをエッチングマスクとして前記犠牲ハードマスク用の非結晶性炭素膜をエッチングし、犠牲ハードマスクを形成するステップと、少なくとも前記犠牲ハードマスクをエッチングマスクとして前記被エッチング層をエッチングし、所定のパターンを形成するステップとを含む。

(もっと読む)

半導体装置の製造方法、半導体装置、及び電子機器

【課題】 積層された半導体チップの接合強度が高く、これにより高い信頼性を確保することができる半導体装置の製造方法及び半導体装置、並びに当該半導体装置を備える電子機器を提供する。

【解決手段】 半導体基板10の能動面10aから半導体基板10の内部にかけて第一孔部H3を形成する工程と、第一孔部H3の内側に導電材料を充填して第一接続端子20を形成する工程と、半導体基板10の能動面10aとは反対側の裏面10bから第一孔部H3の底面に到達する第二孔部H6を形成する工程と、第二孔部H6の内面に導電材料を充填して第二接続端子21を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 写真製版処理で解像可能な寸法より小さな寸法の積層物を半導体基板上に形成できる半導体装置の製造方法を提供する。

【解決手段】 この半導体装置の製造方法は、半導体基板3上に写真製版処理により所定の横幅W2の積層物11aを形成する工程と、積層物11a上に第1のマスク層13を形成し、この第1のマスク層13に、エッチングにより、積層物11aの前記横幅方向に直交する方向に渡って、前記積層物11aの前記横幅方向のその開口幅W4が第1のマスク層13の上面から下面に向かってテーパ状に狭まった開口部13dを形成する工程と、第1のマスク層13をマスクとして積層物11aを開口部13dの下面開口に沿って部分的にエッチング除去することにより、積層物11aを開口部13dの下面開口に沿って分割積層物11に分割する工程とを含む。

(もっと読む)

シリコンゲルマニウム犠牲層を用いた半導体素子の微細パターンの形成方法及びそのパターンの形成方法を用いた自己整列コンタクトの形成方法

【課題】 シリコンゲルマニウム犠牲層を使用して半導体素子の微細パターンを形成する方法、及びそれを用いた自己整列コンタクトを形成する方法を提供する。

【解決手段】 基板上に導電性物質膜、ハードマスク膜及び側壁スペーサを含む導電ライン構造物を形成し、基板の全面に少なくとも導電ライン構造物の高さと同じであるか、またはそれ以上の高さにシリコンゲルマニウム(Si1−XGeX)犠牲層を形成し、犠牲層上にコンタクトホールを限定するフォトレジストパターンを形成した後、犠牲層を乾式エッチングすることで基板を露出させるコンタクトホールを形成し、ポリシリコンを使用してコンタクトホールを埋め込む複数のコンタクトを形成した後に残留する犠牲層を湿式エッチングした後、その領域にシリコン酸化物を満たして第1層間絶縁層を形成する半導体素子の自己整列コンタクトの形成方法。

(もっと読む)

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

リバーストーン処理を利用したリセス構造の形成方法

本発明は基板上にリセス部を形成する方法を提供し、該方法は第1のフューチャを有するパターン形成層を基板上に形成する段階と、第1のフューチャをトリムエッチングしてある形状を有するトリムフューチャを形成する段階と、該形状の反転形状を基板に転写する段階とを含む。 (もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

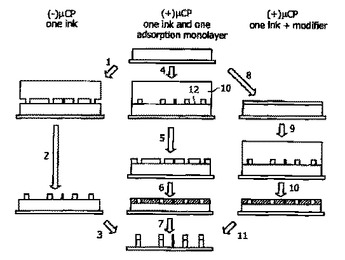

基板上にパターン化層を形成する方法

ソフト・リソグラフィのパターン化工程によって基板(24)上にパターン化された自己組織化単分子層(20)を形成する方法であって、その方法は、a)前記パターン化された自己組織化単分子層(20)の必要なパターンを画定するためのパターン化手段(10)を提供すること、b)前記基板(24)の表面(22)上に自己組織化単分子層(20)を形成すること、c)前記パターン化手段(10)を前記基板(24)の前記表面に適用することであって、前記パターン化手段(10)が前記基板表面の選択された領域に修飾剤を送達するように配置され、前記選択された領域が前記必要なパターン又はそのネガに対応し、前記修飾剤が化学物質を含み、且つ前記選択された領域で、前記自己組織化単分子層(10)の分子と前記基板(24)の前記表面との間の相互作用の強さを変えるように配置されること、並びにd)ステップc)の後、その分子と前記基板の前記表面との間でより低い相互作用の強さを示す前記自己組織化単分子層(20)の領域を選択的に除去又は置換し、それによって前記必要なパターンを有する自己組織化単分子層(20)を形成することを含む。修飾剤は、工程の要求に応じて、自己組織化単分子層の分子と基板の最上面との間の相互作用の強さを弱める又は高めるように選択されてもよい。  (もっと読む)

(もっと読む)

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

製造方法

【課題】 基板内に導電性構造体を形成する方法を提供すること。

【解決手段】 表面上に多段階層構造体を形成する方法が記載される。この方法は、表面上に硬化可能な液体層を堆積させるステップと、内部に多層パターンを有するスタンプを液体層に圧入し、該パターンによって定められる多段階層構造体を該液体層内に生成するステップと、液体層を硬化させ、内部に多段階層構造体を有する固体層を生成するステップとを含む。機械的位置合わせを用いて、構造体を形成することになる基板上に離間配置された複数の突出部及びスタンプのパターン内の相補的陥凹部を介して、基板に対するスタンプの光学的位置合わせを強化することができる。

(もっと読む)

マスキング方法

本発明はマスキング方法を包含する。1つの実施において、ホウ素ドープアモルファスカーボンを含むマスキング材料が、半導体基板上に形成されたフィーチャーを覆って形成される。マスキング材料は少なくとも約0.5原子パーセントのホウ素を含む。マスキング材料は実質的に異方的にエッチングされ、ここでそのエッチングはホウ素ドープアモルファスカーボンを含む異方的にエッチングされたサイドウォールスペーサをフィーチャーのサイドウォール上に形成するのに有効である。次に、スペーサに最も近い基板が、ホウ素ドープアモルファスカーボンを含むスペーサをマスクとして用いながら加工される。スペーサに最も近い基板を加工した後、ホウ素ドープアモルファスカーボンを含むスペーサが基板からエッチングされる。他の実施および面も考えられる。 (もっと読む)

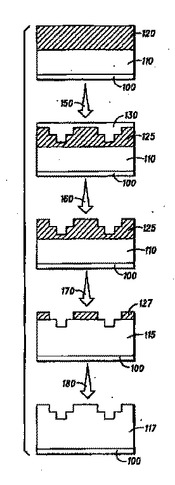

インプリント・リソグラフィによる単一デュアルダマシン製法

インプリント・リソグラフィと共に多段構造を有するテンプレートを用いるデュアルダマシン構造の製造方法の一例は、多段構造を有するリソグラフィ用テンプレート(130)をレジスト層(120)と接触するように配置するステップ(ステップ150)と、テンプレート(130)に圧力を加えることによりレジスト材料(120)がテンプレート(130)のレリーフパターン内に流れ込み、パターン化されたレジスト層(125)が形成されるステップと、そのパターン化されたレジスト層(125)を必要に応じて硬化するステップと、テンプレート(130)をパターン化されたレジスト層(125)から取り外すステップ(ステップ160)と、及びパターニング層(117)にビアやトレンチを作製するためパターン化されたレジスト層(125)をエッチングするステップ(ステップ170,180)とからなる。開示された特徴や仕様は、デュアルダマシン構造や他の多段構造の作製を改良したり、他の方法で最適化したりするため、様々に制御したり、設定したり、適合させたり、他の方法で部分的に変更したりしてもよい。  (もっと読む)

(もっと読む)

241 - 260 / 260

[ Back to top ]