Fターム[5F033QQ26]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287)

Fターム[5F033QQ26]の下位に属するFターム

導電膜 (467)

絶縁膜 (1,171)

多層レジスト (195)

エッチング後も残存させるもの (194)

Fターム[5F033QQ26]に分類される特許

141 - 160 / 260

接点抵抗が改善された半導体構造およびその製造方法(接点抵抗が改善された半導体構造)

【課題】 構造の接点抵抗を改善した、すなわち低下させた半導体構造を提供する。

【解決手段】 自己組織化・ポリマー技術を用いて、半導体構造の導電性コンタクト領域に存在する材料内に少なくとも1つの配列されたナノサイズ・パターンを形成する。配列されたナノサイズ・パターンを有する材料は、相互接続構造または電界効果トランジスタの半導体ソースおよびドレイン領域の導電材料である。接点領域内に整列ナノサイズ・パターニング材料が存在することによって、以降の接点形成のための全領域(すなわち界面領域)が拡大し、これによって構造の接点抵抗が低下する。接点抵抗の低下により、構造を通る電流が改善する。上述のことに加えて、本発明の方法および構造では、接合領域が不変のままであるので、構造の接合容量は影響を受けない。

(もっと読む)

液晶表示装置

【課題】

下地との優れた密着性を有し、銅やシリコンの拡散を防止し低抵抗銅配線を備えた液晶画像表示装置を提供する。

【解決手段】

アモルファスシリコン等を形成した基板上に、窒化物の生成自由エネルギが負の金属を添加した銅−金属合金ターゲットを用いて窒素+アルゴン雰囲気で金属元素と窒素とを含有する銅を主成分とする合金層を形成する。次にアルゴンのみで銅と金属の合金膜を成膜することで拡散バリアを有する金属元素を含有する銅を主成分とする合金膜と、金属元素と窒素とを含有する銅を主成分とする合金膜との積層配線を形成する。

(もっと読む)

半導体装置の製造方法

【目的】レベンソン型マスクを用いた場合でもくびれ部分を形成せずにコンパクトな膜パターンを形成する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に被加工膜を形成する工程(S104)と、前記被加工膜上に非最細膜パターンを形成する工程(S114)と、前記非最細膜パターンが形成された後、レベンソン型マスクを用いて端部の位置が前記非最細膜パターンと重なるように最細パターンを露光する工程(S116)と、前記最細パターンが露光された後、前記最細パターン幅の最細膜パターンを形成する工程(S118−S122)と、前記非最細膜パターンと前記最細膜パターンとが転写されるように前記被加工膜をエッチングする工程(S126)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】CMP法による研磨を行った際に、ウェーハ周辺部における配線材料の崩れに起因する異物の発生が生じず、ウェーハ表面に傷をつけることがないようにする。

【解決手段】シリコン基板上に多孔質絶縁膜及び絶縁膜を形成し、シリコン基板の周辺部をカバーするためのハードマスクカバー膜を介して配線形成用のレジストパターンを形成する。シリコン基板周辺部に配線パターンが形成されることを防止する。

(もっと読む)

半導体素子のコンタクトプラグ製造方法

【課題】ナンドフラッシュメモリ等のソース/ドレインコンタクトプラグを形成する半導体素子のコンタクトプラグ製造方法を提供する。

【解決手段】選択ラインSSLとワードラインWL0,WL1間の露出された半導体基板102に接合領域114a、114bを形成する段階と、選択ラインSSLとワードラインWL0,WL1上に第1の保護膜120を形成する段階と、第1の保護膜120上に絶縁層122を形成する段階と、選択ラインSSL間の第1の保護膜120が露出されるように選択ラインSSL間の絶縁層122にコンタクトホールAを形成する段階と、コンタクトホール側壁に露出された第1の保護膜上に第2の保護膜124を形成する段階と、コンタクトホールA底面の第1の保護膜120を除去する段階、及びコンタクトホールAに導電物質を形成して接合領域114a、114bと連結されるコンタクトプラグを形成する段階とを含む。

(もっと読む)

基板の処理方法、プログラム、コンピュータ記憶媒体及び基板処理システム

【課題】基板上の被処理膜に所定の微細なパターンを効率よく形成する。

【解決手段】ウェハW上に被処理膜F、反射防止膜B、レジスト膜Rを下から順に形成する(図5(a))。レジスト膜Rと反射防止膜BにパターンR1、B1をそれぞれ形成する(図5(b))。パターンR1をマスクとして被処理膜Fをエッチングし、被処理膜FにパターンF1を形成する(図5(c))。パターンB1の側壁部を溶解して、反射防止膜BにパターンB2を形成する(図5(d))。パターンB2を覆うように犠牲膜Gを形成する(図5(e))。パターンR1、B2をそれぞれ除去する(図5(f))。犠牲膜GをマスクとしてパターンF1をエッチングし、被処理膜FにパターンF2を形成する(図5(g))。犠牲膜Gを除去する(図5(h))。

(もっと読む)

半導体装置の製造方法

【課題】製造コストの増大を抑えながら、コンタクト抵抗のばらつきを低減できる半導体装置の製造方法を提供する。

【解決手段】第1の絶縁膜上に第1の導電層を形成する工程と、第1の導電層を覆うように第2の絶縁膜を形成する工程と、第2の絶縁膜上にレジストマスクを形成する工程と、前記レジストマスクを用いた第1のドライエッチングにより、第2の絶縁膜に、第1の導電層に達するホールを形成する工程と、前記レジストマスクを除去する工程と、前記ホールの底に露出した第1の導電層を第2のドライエッチングにより除去して、このホールが第1の絶縁膜に達し且つこのホール内の側面に第1の導電層を露出させる工程と、前記ホール内に導電材を埋め込んで、このホール内の側面に露出した第1の導電層と接触する導電プラグを形成する工程と、第2の絶縁膜上に、前記導電プラグに接続する第2の導電層を形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のゲート加工用のマスク層に関する新たな提案を行う。

【解決手段】基板上方に第1乃至第3のマスク層を堆積し、第3のマスク層を加工し、第2のマスク層を加工し、L/S部内及びL/S部外の第2のマスク層をスリミングし、L/S部内及びL/S部外の第3のマスク層を剥離し、L/S部内及びL/S部外の第2のマスク層の側壁にスペーサを形成し、L/S部外の第2のマスク層がレジストで覆われた状態でL/S部内の第2のマスク層をエッチングすることで、L/S部外の第2のマスク層を残存させつつL/S部内の第2のマスク層を除去し、L/S部内及びL/S部外のスペーサとL/S部外の第2のマスク層とをマスクとして、第1のマスク層をエッチングにより加工し、当該エッチングにより、L/S部内及びL/S部外のスペーサとL/S部外の第2のマスク層とが薄膜化されることを特徴とする半導体装置の製造方法。

(もっと読む)

金属塩を含有する剥離液を用いる金属エッチレートの低減

半導体集積回路用の半導体デバイス上に回路を製作及び/又は電極を形成するのに有用な、低減された金属エッチレート、特に低減された銅エッチレートを有するレジスト剥離剤を、それらの使用法とともに提供する。好適な剥離剤は、低濃度の銅塩又はコバルト塩を、銅塩又はコバルト塩の溶解度を改良するためのアミンと共に又はアミンなしで含有する。さらに、これらの方法に従って製造された集積回路デバイス及び電子相互接続構造も提供する。 (もっと読む)

半導体装置の製造方法

【課題】穴径の小さいホールを容易かつ確実に形成することを可能ならしめる半導体装置の製造方法を提供する。

【解決手段】炭素と水素を主元素とし所定の開口径を有する穴部14を備えたレジスト膜12を絶縁膜10上に形成し(ST1)、このレジスト膜12をマスク材として絶縁膜10の途中深さまでエッチング加工し(ST2)、レジスト膜12をXeF2ガス雰囲気に暴露することにより、レジスト膜12の表面を膨張させて穴部14の開口径を縮小させ(ST3)、こうして生成したレジスト膨張部12aと元のレジスト膜12をマスク材として絶縁膜10の下端面までエッチング加工し(ST4)、ホール16を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】例えば、液晶装置等の半導体装置について、製造プロセスを煩雑化させることなく、且つコンタクト抵抗の上昇を低減する。

【解決手段】凹部221a及び221bは、絶縁膜213上にレジスト膜222を形成した後、半導体製造プロセスで汎用される回折法或いはハーフトーン法を用いてレジスト膜222を部分的に除去することによって形成されている。したがって、レジスト膜221は、レジスト膜222を部分的に除去することによって形成された凹部221a及び221bの底部を構成するレジスト膜222の一部を含んで構成されている。凹部221bの深さd2は、凹部221aの深さd1より浅い。言い換えれば、凹部221bの底部の厚みは、凹部221aの底部の厚みより厚くなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

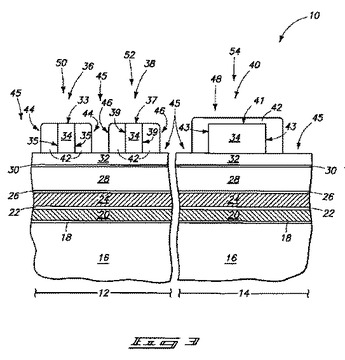

自己集合ナノ構造をパターン化する方法及び多孔性誘電体層を形成する方法(自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法)

【課題】 自己集合ナノ構造をパターン化しそして多孔性誘電体層を形成する方法を提供する。

【解決手段】 自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法は、1つの態様において、下側層を覆ってハードマスク層を設けるステップと、パターン化の間に保護されるべきハードマスク層の領域をフォトレジスト層により予め画定するステップと、ハードマスク層及びフォトレジスト層を覆って共重合体層を形成するステップと、共重合体層から自己集合ナノ構造を形成するステップと、自己集合ナノ構造をパターン化するためにエッチングするステップとを含む。

(もっと読む)

配線構造及び半導体装置、並びにそれらの製造方法

【課題】配線間隔の狭い回路において配線容量を低減させた配線構造及び半導体装置、並びにそれらの製造方法を提供することを目的とする。

【解決手段】導電性の配線層8を形成する工程と、配線層8に配線パターンを形成する工程と、前記配線パターンの配線10A,10B,10C,10D間に絶縁性の配線層間膜11を形成する工程と、配線層間膜11の厚さ方向に、縦穴状の微細孔14を複数形成する工程を有することを特徴とする。また、微細孔14は、ナノ粒子12またはナノ粒子12を含有する材料からなるマスクを用いて、エッチングすることにより形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】 微小なコンタクトホールを狭いピッチで形成することができ、且つ露光装置に対する要求(高NA)の緩和及びチップ面積の縮小をはかる。

【解決手段】 半導体装置の製造方法であって、被処理膜11上に、複数のコンタクトパターンのパターン開口を有し、且つ隣接するパターン開口を括れた状態で接続する接続開口を有するマスク材料膜22を形成した後、マスク材料膜22の各開口の側壁に側壁膜25を形成することにより、パターン開口の径を小さくすると共に隣接するパターン開口を分離し、次いでマスク材料膜22及び側壁膜25をマスクとして被処理膜21を選択的にエッチングしてコンタクトホールを形成する。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】目標臨界寸法を有する微細パターンを形成方法を提供する。

【解決手段】微細パターンを形成方法は、半導体基板100の上部にエッチング対象膜、第1のハードマスク膜及び菱状の絶縁パターンを形成する段階、絶縁パターンを含む前記第1のハードマスク膜上に第1の補助パターンを形成するが、四角形で隣接した4個の前記絶縁パターンの間の中央には絶縁パターンと同一の形態のコンタクトホールを有するように形成する段階、前記絶縁パターンの上部が露出されるように前記第1の補助パターンをエッチングして第2の補助パターンを形成する段階、前記露出された絶縁パターンを除去する段階、前記第2の補助パターンをエッチングマスクとして用いるエッチング工程で前記第1のハードマスク膜をエッチングして第1のハードマスクパターン102aを形成する段階、及び第1のハードマスクパターンを用いて前記エッチング対象膜をエッチングする段階を含む。

(もっと読む)

半導体装置の製造方法

【課題】タングステン配線の断面形状を良好にすることにより、配線抵抗の増大及び配線信頼性の低下を防ぐ。

【解決手段】先ず、下地100を用意して、下地上に、バリア膜120、配線膜130及びマスク膜140を順次に積層する。バリア膜及びマスク膜が窒化チタンであり、配線膜がタングステンである。次に、マスク膜上に、反射防止膜150を塗布する。次に、反射防止膜上に、レジスト膜を形成した後、フォトリソグラフィによりパターニングして、レジストマスク160を形成する。レジストマスクは、配線形成領域105を覆い、かつ配線非形成領域107を露出する。次に、フッ素系ガスを用いたエッチングにより反射防止膜のパターニングを行う。次に、塩素系ガスを用いたエッチングによりマスク膜のパターニングを行う。次に、フッ素系ガスを用いたエッチングにより配線膜のパターニングを行う。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】工程数を増やすことなく、安価に微細パターンを形成する方法を提供する。

【解決手段】半導体基板上にエッチング対象膜102、ハードマスク膜104及び第1の補助パターンを形成し、第1の補助パターンにシリレーション工程を行う。シリレーションされた第1の補助パターン106aを含む上記ハードマスク膜上に絶縁膜108を形成し、上記シリレーションされた第1の補助パターンの間の絶縁膜108上に第2の補助パターンを形成する。上記絶縁膜が上記第2の補助パターンの下部にのみ残留するようにエッチング工程を行い、上記シリレーションされた第1の補助パターン及び第2の補助パターンをエッチングマスクとして用いるエッチング工程で上記ハードマスク膜をエッチングしてハードマスクパターンを形成する。ハードマスクパターンを用いて上記エッチング対象膜をエッチングする。

(もっと読む)

半導体構造、複数のラインを形成する方法、および高密度構造と低密度構造を単一フォトマスクで形成する方法

いくつかの実施形態は、犠牲材料に沿ったポリマースペーサーの形成、犠牲材料の除去、および集積回路の製造中におけるマスクとしてのポリマースペーサーの利用、を含む。ポリマースペーサーマスクは、例えばフラッシュメモリアレイのフラッシュゲートをパターン化するために利用されてもよい。いくつかの実施形態では、ポリマーは大きな犠牲構造と小さな犠牲構造にわたって同時に形成される。ポリマーは、小さな犠牲構造にわたってよりも、大きな犠牲構造にわたっての方が厚く、こうした厚さの差を利用して、高密度構造と低密度構造を単一フォトマスクで製造する。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】研磨工程などを削減するとともに素子分離領域の上に微細なゲートスペースパターンを有する。

【解決手段】半導体装置は、半導体基板100と、素子分離絶縁膜101と、第1および第2電極107a,107bと、ゲート絶縁膜パターン104と、側壁絶縁膜108とを備えている。素子分離絶縁膜101は半導体基板100の上に設けられており、第1および第2電極107a,107bはゲート絶縁膜パターン104を挟むようにして素子分離絶縁膜101の上に設けられている。側壁絶縁膜108は、第1および第2電極107a,107bの側面のうちゲート絶縁膜パターン104に接している部分以外の部分に設けられている。

(もっと読む)

141 - 160 / 260

[ Back to top ]