Fターム[5F033QQ26]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287)

Fターム[5F033QQ26]の下位に属するFターム

導電膜 (467)

絶縁膜 (1,171)

多層レジスト (195)

エッチング後も残存させるもの (194)

Fターム[5F033QQ26]に分類される特許

61 - 80 / 260

周期的な酸化およびエッチングのための装置と方法

半導体装置及びその製造方法

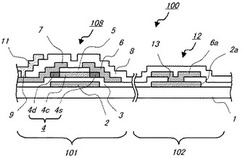

【課題】リーク電流が低く、電界効果移動度が高いなどの優れた特性を有するTFTを備え、駆動回路を内蔵して部材点数を減らすことが可能な半導体装置において、駆動回路内部における腐食などの発生を防止する。

【解決手段】本発明の半導体装置においては、駆動回路を内蔵したTFTアレイ基板100に、ゲート電極2と、ゲート絶縁膜3と、結晶性半導体部分を含んでチャネル領域4cが形成される半導体層4と、チャネル領域4cを保護するチャネル保護膜5と、半導体層4に接続されたソース電極6及びドレイン電極7を備えたTFT、並びに、ゲート電極2と同層に形成された配線層2aとソース電極6と同層に形成された配線層6aを駆動回路内部においてコンタクトホール13を介し直接接触させて接続させる配線変換部12を備えるものである。

(もっと読む)

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】窒化シリコン層3上に形成されたポリシリコン層をパターニングすることによってメモリセルアレイ領域1aにスリミングされたサイドウォールコア4を形成する。次に、サイドウォールコア4の少なくとも側面を覆う酸化シリコン層6、ポリシリコン層を順に成膜し、ポリシリコン層をエッチバックすることによって埋込ハードマスク7を形成する。その後、酸化シリコン層6をエッチングすることにより、サイドウォールコア4又は埋込ハードマスク7と重ならないメモリセルアレイ領域1a内の窒化シリコン層3と、目合わせモニタマーク8bと重なる周辺回路領域1b内の窒化シリコン層3を露出させ、被エッチング部材としての窒化シリコン層3をパターニングする。

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜のスリミング時にその膜厚の消費を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上に複数の絶縁層25と複数の導電層WLとを交互に積層して積層体を形成する工程と、積層体上にレジスト膜50を形成する工程と、レジスト膜50をマスクにして絶縁層25及び導電層WLをプラズマエッチングする工程と、ホウ素、リン及びヒ素の少なくとも1つを含むガスを用いたプラズマ処理により、レジスト膜50の上面に、ホウ素、リン及びヒ素の少なくとも1つを含む硬化層51を形成する工程と、レジスト膜50の上面に硬化層51が形成された状態で、酸素を含むガスを用いたプラズマ処理によりレジスト膜50の平面サイズをスリミングする工程と、を備えた。

(もっと読む)

パターン形成方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等のパターンを作製する方法、さらには、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜、良好なマスクパターン、及びコンタクトホールを形成する方法を提案し、更には低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】本発明の一は、膜上にぬれ性の低い1のマスクパターンを形成した後、第1のマスクパターンを介して、膜上にぬれ性の高い材料を塗布又は吐出して第2のマスクパターンを形成し、第1のマスクパターンを除去して、第2のマスクパターンをマスクとして第1の膜の一部を除去する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】銅を含む層とチタニウムを含む層とをエッチングする時に、非過水系のエッチング液を使用して工程の安定性を向上させる。

【解決手段】本発明は、薄膜トランジスタ表示板に対する発明であって、より詳細には、銅(Cu)とチタニウム(Ti)とをそれぞれ含む二重層配線に形成される薄膜トランジスタ表示板に関し、構造的にはチタニウムを含む層が銅を含む層より幅が広くて、チタニウムと銅とを共にエッチングする段階と、別にエッチングする段階とを含めて製造することを特徴とする。また、ゲート絶縁膜に段差が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】マイクロローディング効果を抑えつつ開口幅の異なる溝を同時に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工部材1上の第1のマスク膜2上に、第1のアスペクト比を有する溝4aを含む小開口パターン領域5aと第1のアスペクト比よりも小さい第2のアスペクト比を有する溝4bを含む大開口パターン領域5bを含むパターンを有する第2のマスク膜3を積層する工程と、第2のマスク膜3のパターンを第1のマスク膜2に転写する工程と、小開口パターン領域5aの第2のマスク膜3を選択的に除去する工程と、小開口パターン領域5aの第2のマスク膜3を選択的に除去した後、第1のマスク膜2および第2のマスク膜3をマスクとして用いて被加工部材1にエッチングを施し、溝を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ法の露光解像限界未満のラインアンドスペースパターンとなる被加工膜のパターンの上層に、その被加工膜のパターンと接続するコンタクトを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に形成された第2の膜14を、複数の線状部とそれぞれの線状部の一端に形成された線状部よりも幅の広い端部を有するパターンへと加工し、このパターンをスリミングして第1のパターン16を形成し、第1のパターン16の端部141a上を横断する第1の開口180を有する第2のパターンを形成し、第1の開口180内に露出する第2の膜14をエッチングし、端部141aを線状部140aに近い第1の端部142aと、線状部140aと遠い第2の端部143aとに分割することを含む。

(もっと読む)

歪み材料を有する半導体デバイス

歪み材料を有する半導体デバイスが開示される。特定の実施形態では、半導体デバイスは、第1ドレインと第1ソースとの間に第1ゲートを含む第1セルを含む。半導体デバイスはまた、第1セルに隣接する第2セルを含む。第2セルは、第2ドレインと第2ソースとの間に第2ゲートを含む。半導体デバイスはさらに、第1ソースと第2ソースとの間にシャロートレンチ分離領域を含む。第1ソースおよび第2ソース上の第1量の歪み材料は、第1ドレインおよび第2ドレイン上の第2量の歪み材料より多い。  (もっと読む)

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPにおいて、側壁部の形状の対称性を高め、被エッチング膜をエッチングするときの加工精度を向上させることができるマスクパターンの形成方法を提供する。

【解決手段】基板上の被エッチング膜の上に形成されたシリコン膜よりなる第1のライン部が配列したシリコン膜パターンの表面を等方的に被覆するように、カーボン膜を成膜する成膜工程S18と、カーボン膜を第1のライン部の上部から除去すると共に、第1のライン部の側壁部として残存するように、カーボン膜をエッチバックするエッチバック工程S19と、第1のライン部を除去し、側壁部が配列したマスクパターンを形成するシリコン膜除去工程S20とを有する。

(もっと読む)

半導体装置の製造方法及びマスク

【課題】樹脂製のバンプコアの上に導電膜を形成したバンプを有する半導体装置の歩留まりを高くしつつ、バンプピッチを狭くする。

【解決手段】保護絶縁膜120上に感光性樹脂膜210を形成する。次いで、感光性樹脂膜210を露光及び現像することにより、保護絶縁膜120上に、第1の直線に沿って複数のバンプコアを形成する。次いで、複数のバンプコア上、複数の電極パッド130上、及び保護絶縁膜120上に導電膜を選択的に形成することにより、複数のバンプ、及び複数のバンプそれぞれをいずれかの電極パッド130に接続する複数の配線を形成する。そして複数のバンプコアを形成する工程において、多階調マスク50を使用して感光性樹脂膜210を1回のみ露光することにより、バンプコアの側面のうち配線に面する領域を、第1の直線と交わる領域より傾斜を緩やかにする。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPによりマスクパターンを形成する場合に、反射防止膜のエッチング工程を省略し、マスクパターンのパターン倒れを防止することができるマスクパターンの形成方法を提供する。

【解決手段】レジストパターン列の表面を等方的に酸化シリコン膜で被覆するステップS14と、レジストパターン列の間をカーボン膜で埋め込むと共に、上部をカーボン膜で被覆するステップS15と、カーボン膜を、レジストパターン列の上部から除去すると共に、レジストパターン列の間に残存するようにエッチバック処理するステップS16と、残存するカーボン膜を除去すると共に、レジストパターン列の上部を被覆する酸化シリコン膜をエッチバック処理するステップS17と、レジストパターン列をアッシング処理し、中央部と、中央部を両側から挟む膜側壁部とを有する、酸化シリコン膜よりなる第1のマスクパターン列を形成するステップS18とを有する。

(もっと読む)

構造体および構造体を形成する方法

【課題】 サブリソグラフィ・ピッチの構造体とリソグラフィ・ピッチの構造体との相互接続を形成する。

【解決手段】 サブリソグラフィ・ピッチを有する複数の導電線をリソグラフィでパターン形成し、複数の導電線の縦方向から45度より小さい角度の線に沿って切断することができる。代わって、ホモポリマーと混合した共重合体を陥凹エリア内に入れて自己整合し、一定幅領域内にサブリソグラフィ・ピッチを有し、台形領域で隣接線間にリソグラフィ寸法を有する複数の導電線を形成することができる。さらに代わって、サブリソグラフィ・ピッチを有する第1の複数の導電線と、リソグラフィ・ピッチを有する第2の複数の導電線は、同じレベルでまたは異なるレベルで形成することができる。

(もっと読む)

基板処理方法

【課題】半導体デバイスの小型化要求を満たす寸法の開口部をマスク層又は中間層に形成することができる制御性に優れた基板処理方法を提供する。

【解決手段】アモルファスカーボン膜51、SiON膜52,BARC膜53及びフォトレジスト膜54が順に積層されたウエハWを処理する基板処理方法であって、CHF3ガスと、CF3Iガスと、H2ガス及びN2ガスの混合ガスから生成されたプラズマによって、フォトレジスト膜54の開口部55のCD値を縮小しつつ開口部底部のSiON膜をエッチングするシュリンクエッチングステップと、開口部55の側壁面へのデポの堆積を促進させて各CD値のばらつきを吸収するばらつき吸収ステップと、開口部の内面に薄膜を形成して各開口部の開口幅を縮小させる開口幅縮小ステップとを1ステップで行う。

(もっと読む)

ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法

【課題】 ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法を提供する。

【解決手段】 ブロック・コポリマの自己組織化を含む方法であって、目標とするCD(限界寸法)を有する開口部(1つ又は複数の基板内の)から開始して、ホールを規則的な配列又は任意の配列に形成する方法を説明する。重要なことに、形成されたホールの平均直径の百分率ばらつきは、最初の開口部の平均直径の百分率ばらつきより小さくなる。形成されたホール(又はビア)を下層の基板に転写することができ、次にこれらのホールを金属導体のような材料で埋め戻すことができる。本発明の好ましい態様は、22nm以下の技術ノードにおいても、より狭いピッチ及びより優れたCDの均一性を有するビアの作成を可能にする。

(もっと読む)

ブロック共重合体を用いてホール又はビアを有するデバイスを形成する方法

【課題】 ブロック共重合体を用いて所定の位置にホール又はビアを有するデバイスを形成する方法を提供する。

【解決手段】 例えば、光リソグラフィを用いて、輪郭を付けられた凸状のセグメントによって与えられる断面を有する開口部を基板内に形成する。開口部の断面は、例えば、重なった円形領域によって与えることができる。側壁は、種々の点で隣接し、そこで突起を画定する。ブロック共重合体を含むポリマーの層を開口部及び基板の上に塗布し、自己集合させる。開口部内に個別分離ドメインが形成され、これらを除去してホールを形成し、これを下層の基板に転写することができる。これらのドメイン及びこれらの対応するホールの位置は、側壁及びそれらに付随する突起によって所定の位置に誘導される。これらのホールを隔てる距離は、何も側壁がない場合にブロック共重合体(及び何れかの添加剤)が自己集合したとする場合よりも大きく又は小さくすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通配線が断線しにくい信頼性の高い半導体装置1および半導体装置1の製造方法を提供する。

【解決手段】第1の主面10Aと第2の主面10Bとを貫通する基板貫通孔10Hが形成された半導体基板と、第1の主面10Aから離れるにしたがい開口が段階的に小さくなる層間膜貫通孔13Hが形成された層間絶縁膜13とデバイス11と接続された再配線層14とを有する多層配線層15と、再配線層14と接続され層間膜貫通孔13Hの開口部を覆う電極パッド16と、電極パッド16から層間膜貫通孔13Hの側壁および基板貫通孔10Hの側壁を介して第2の主面10B側まで配設された貫通配線19と、第2の主面10B側の貫通配線19上に配設されたバンプ21と、を具備する。

(もっと読む)

61 - 80 / 260

[ Back to top ]