Fターム[5F033QQ26]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287)

Fターム[5F033QQ26]の下位に属するFターム

導電膜 (467)

絶縁膜 (1,171)

多層レジスト (195)

エッチング後も残存させるもの (194)

Fターム[5F033QQ26]に分類される特許

21 - 40 / 260

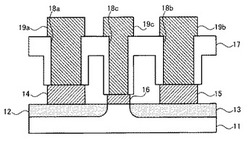

半導体装置及びその製造方法

【課題】精密なエッチング制御を必要とすることなく、ビアホール構造を形成することを可能とするとともに、エッチング後の洗浄を容易にする。

【解決手段】半導体装置において、第1の基板11と、第1の基板表面に形成された素子領域12,13と、素子領域と接続され、第1の基板11上に形成された電極14,15,16と、第1の基板11と積層される第2の基板17と、第2の基板17を貫通し、電極上に配置されるビアホール18a,18b,18cと、ビアホール内に形成される金属層19a,19b,19cと、を備える。

(もっと読む)

薄膜トランジスタ基板およびその製造方法

【課題】高い表示品位を有する表示装置用の薄膜トランジスタ基板およびこれらを生産効率よく実現することができる製造方法を提供する。

【解決手段】基板1上の複数の部分に配設された半導体膜2と、半導体膜2上に、該半導体膜2と接し互いに離間して配設されたソース電極およびドレイン電極4と、半導体膜2、ソース電極3およびドレイン電極4を覆うゲート絶縁膜6と、ゲート絶縁膜6を介して、ソース電極3およびドレイン電極4の間に跨るように配設された、ゲート電極7とを有した薄膜トランジスタ201と、半導体膜2上に、該半導体膜と接して配設された補助容量電極10と、下層に半導体膜2を有してソース電極から延在するソース配線31と、ゲート電極7から延在するゲート配線71と、ドレイン電極4に電気的に接続された画素電極9と、隣り合う画素の補助容量電極10どうしを電気的に接続する、補助容量電極接続配線12とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

パターン状金属膜の製造方法

【課題】レジスト膜の厚みを比較的小さくしてかつオーバーエッチングするパターン状金属膜の製造方法において、所望パターンの金属膜を安定的に製造することができる製造方法を提供する。

【解決手段】金属膜上にパターン状のレジスト膜を形成する工程(A)、前記金属膜をエッチングする工程(B)を順次有するパターン状金属膜の製造方法であって、前記レジスト膜は厚みが5μm以下でかつ鉛筆硬度がB以下であり、前記工程(B)において前記レジスト膜の線幅100%に対してパターン状金属膜の線幅が80%以下となるようにオーバーエッチングする、パターン状金属膜の製造方法。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

コンピュータ読み取り可能なマスクシュリンク制御プロセッサ

【課題】CD(限界寸法)誤差を低減し、シュリンク処理の形状依存を補正できるパターン化フォトレジスト層を実現するコンピュータ読み取り可能な媒体を備えた装置を提供する。

【解決手段】媒体614は形状レイアウトを受信するためのコンピュータ読み取り可能なコードと、形状レイアウトに対してシュリンク補正を適用するためのコンピュータ読み取り可能なコードとを備える。シュリンク補正を適用するためのコンピュータ読み取り可能なコードは、パターン化層に形状を形成するための角切り欠き部を提供して、線の幅および長さ、形の修正などを調整する。

(もっと読む)

半導体素子の形成方法

【課題】相互接続領域の具現が困難なパッドレイアウトを具現化し、オーバレイマージンを増大できる半導体素子の形成方法を提供する。

【解決手段】半導体基板に被食刻層、第1のハードマスク物質層、第1の分割パターン物質層及び第2のハードマスク物質層を形成して選択食刻し第2のハードマスクパターンを形成し、これをマスクとし第1の分割パターン物質層を食刻し第1の分割パターンを形成する。第1のハードマスク物質層の上部にスペーサ物質層及び第2の分割パターン物質層を形成し、第1の分割パターンが現われるまでスペーサ物質層及び第2の分割パターン物質層を部分食刻しスペーサ物質層を露出させ、複数の第1の分割パターン間に第2の分割パターンを形成し、第1、第2の分割パターンをマスクとしスペーサ物質層及び第1のハードマスク物質層を食刻し第1のハードマスクパターンを形成し、これをマスクとし被食刻層を食刻し微細パターンを形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】貫通孔の側面のスキャロップ形状及びアンダーカットを修復する。

【解決手段】半導体装置は、第1の基板と、第2の基板と、前記第1の基板と前記第2の基板との間に配置され、前記第1の基板と前記第2の基板とを接着する接着層と、を備え、前記第2の基板及び前記接着層には、前記第2の基板及び前記接着層を貫通する貫通孔が形成されており、前記貫通孔の側面には、凹部が形成されており、前記凹部には、少なくとも有機骨格を有する樹脂が埋め込まれており、前記貫通孔の中には、導電体が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 はんだからなるバンプの形成工程中やフリップチップ実装時に、スズのようなはんだ成分がバンプ電極のアンダーバリアメタルを透過してその下のパッド電極と反応し、バンプとパッド電極間の接合信頼性が低下することを防止する。

【解決手段】 半導体基板1上に形成されたパッド電極3とはんだからなるバンプ8間にアンダーバリアメタル6が形成される。アンダーバリアメタル6は保護絶縁膜4に形成された開口5に露出するパッド電極3上から開口5周囲の保護絶縁膜4上までを被覆する。しかしバンプ8の底面はアンダーバリアメタル6より小さく、望ましくは開口5より小さく、且つ開口5内部領域の垂直上方に形成される。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、芯材除去後の側壁材の倒れを防ぐ半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、上端と下端との間にくびれた部分を有する芯材20を、下地層上に形成する工程を備えている。また、半導体装置の製造方法は、芯材20の側壁に、芯材20とは異なる材料の側壁材16を形成する工程を備えている。また、半導体装置の製造方法は、芯材20を除去して、側壁材16を下地層上に残す工程を備えている。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】レジストの膜減りによって残すべき配線がエッチングされることを防止すると共に、露光機による配線パターニング時のフォーカスずれを抑制し、配線の線幅にバラツキが生じることを防止する。

【解決手段】スクライブライン内において、スクライブラインの両側では層間絶縁膜2、4、6が存在せず半導体基板1の表面が露出する領域を設け、スクライブラインの中央位置、つまり溝Tの間に挟まれた領域には層間絶縁膜2、4、6を残す。これにより、スクライブラインとチップとの境界位置近傍において、第3配線層7を形成する際のマスクとして用いるレジスト21が膜減りすることを抑制できる。したがって、レジスト21の膜減りによって残すべき配線がエッチングされることを防止できると共に、露光機による第3配線層7のパターニング時のフォーカスずれを抑制でき、第3配線層7の線幅にバラツキが生じることを防止することが可能となる。

(もっと読む)

多層薄膜パターン及び表示装置の製造方法

【課題】間便に所望の形状のパターンを得ることのできる多層薄膜パターン及び表示装置の製造方法を提供すること。

【解決手段】基板上に層間絶縁膜1を形成する工程と、層間絶縁膜1上に導電性を有する第1の薄膜2を形成する工程と、第1の薄膜2上に第2の薄膜3を形成する工程と、第2の薄膜3上に、複数階調露光によって膜厚差を有するレジストパターン5を形成する工程と、膜厚差を有するレジストパターン5を介して、第2の薄膜3及び第1の薄膜2をエッチングして、レジストパターンの存在しない領域の層間絶縁膜1を露出させる工程と、膜厚差を有するレジストパターン5をアッシングして、レジストパターンの薄膜部5bを除去する工程と、薄膜部5bが除去されたレジストパターン5cを介して、第2の薄膜3をエッチングする工程と、を順次実施する。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

半導体装置

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

21 - 40 / 260

[ Back to top ]