Fターム[5F033QQ60]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 絶縁膜 (83)

Fターム[5F033QQ60]に分類される特許

41 - 60 / 83

半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法

本明細書には概して半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法が記載されている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の層間絶縁膜として用いられる有機SOG膜にコンタクトを形成する際のポイズンドビアの発生を抑制する。

【解決手段】半導体基板42上に配置した複数の下層配線46とその間隙47とを覆って、有機SOG膜を塗布し平坦化する。有機SOG膜をイオン注入により改質し、コンタクトホール56より深い位置まで改質SOG膜52に変える。特に、下層配線46の上からずれて形成されるコンタクトホール56bは、下層配線46の上面より低い位置まで到達する。改質SOG膜52は、このコンタクトホール56bが到達する深さより深い位置まで形成される。この改質SOG膜52の形成後、コンタクトホール56が形成される。コンタクトホール56の内部には、未改質の有機SOG膜50が現れず、プラグ60を埋め込む際にポイズンドビアとなることが防止される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の層間絶縁膜として用いられる有機SOG膜を、イオン注入により改質する際、クラックが発生する。

【解決手段】半導体基板42上に配置した複数の下層配線46とその間隙47とを覆って、有機SOG膜を塗布し平坦化する。有機SOG膜を目的深さまで改質する工程は、予備改質工程と本改質工程との2段階で行う。まず、予備改質工程が行われ、目的深さより浅い中間深さまで有機SOG膜を第1のイオン注入により改質し、上部改質SOG膜52uを形成する。予備改質工程に続いて本改質工程が行われ、第1のイオン注入より高いエネルギーで第2のイオン注入を行い、目的深さまでの有機SOG膜を改質して、上部改質SOG膜52uの下に下部改質SOG膜52dを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 n型FET及びp型FETのドレイン電流の増加(電流駆動能力の向上)を図る。

【解決手段】 半導体基板に形成されたn型及びp型FETを有する半導体装置の製造であって、前記p型FETのゲート電極と前記半導体基板の素子分離領域との間の半導体領域を絶縁膜で覆った状態で、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記n型FETのチャネル形成領域に引っ張り応力を発生させる第1の絶縁膜を形成する(a)工程と、エッチング処理を施して、前記p型FET上の前記第1の絶縁膜を選択的に除去する(b)工程と、前記n型及びp型FET上にこれらのゲート電極を覆うようにして、前記p型FETのチャネル形成領域に圧縮応力を発生させる第2の絶縁膜を形成する(c)工程と、前記n型FET上の前記第2の絶縁膜を選択的に除去する(d)工程とを有する。

(もっと読む)

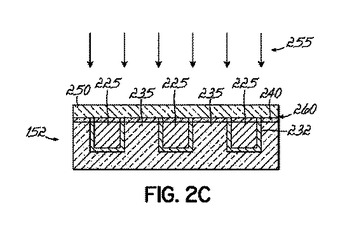

半導体デバイスのデュアルストレスライナ上方の付加層を使用することによって向上するNチャネルトランジスタのトランジスタパフォーマンス

それぞれ固有応力が異なる誘電ライナ(230、240)をパターニングした後に、窒化シリコンなどの付加的誘電材料(260)を形成することによって、Pチャネルトランジスタ(220B)のパフォーマンスを実質的に低下させずにNチャネルトランジスタ(220A)のパフォーマンスを著しく向上させることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 nチャネル導電型電界効果トランジスタ及びpチャネル導電型電界効果トランジスタの電流駆動能力の向上を図る。

【解決手段】 半導体基板の一主面の第1の領域にチャネル形成領域が構成されたnチャネル導電型電界効果トランジスタと、前記半導体基板の一主面の第1の領域と異なる第2の領域にチャネル形成領域が構成されたpチャネル導電型電界効果トランジスタとを有する半導体装置であって、前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力と、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力とが、各々で異なっている。前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は引っ張り応力であり、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は圧縮応力である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】合わせずれにより下層配線層の絶縁膜が大きくエッチングされてしまうことを抑制する半導体装置の製造方法及びその方法で製造された半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、下層配線となるCu膜260と、Cu膜260の側面側に配置された有機絶縁膜220と、Cu膜260の側面側であって有機絶縁膜220上に配置された有機絶縁膜220よりも比誘電率が高いSiOC膜222と、SiOC膜222側に一部がはみ出して配置された、Cu膜260を上層配線265側へと接続するプラグ263と、Cu膜262のSiOC膜222側にはみ出した部分の下部に配置された、SiOC膜222よりもエッチングレートが低い膜質の改質膜280と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルアレイ領域となるリソグラフィの解像限界以下の直線部と、その直線部を接続する接続部とを有するソース・ドレイン拡散層を簡易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】シリコン窒化膜50上に第1ハードマスク60、X軸方向に直線状に延びる第2ハードマスク70を複数並列して形成する。次に、第2ハードマスク70のヒンジ領域Hにイオン注入しエッチングレートを変化させる。次に、第2ハードマスク70をマスクとして第1ハードマスク60をエッチングし、イオン注入されていない第2ハードマスク70のみエッチング除去する。次に、第1ハードマスク60に側壁膜80を形成し、第2ハードマスク70に覆われていない第1ハードマスク60をエッチング除去する。そして、側壁膜80及び第1ハードマスク60をマスクとしてシリコン窒化膜50をエッチング除去する。

(もっと読む)

半導体装置の製造方法

【課題】膜中の空孔の孔径及び空孔率を正確に制御することができ、かつ良好なスループットで多孔質膜を形成する.

【解決手段】第1工程において、下地11の上側表面11aに、SiO2GeO2膜15を形成する。次いで、第2工程において、SiO2GeO2膜15を水洗することによって、SiO2GeO2膜に含まれるGeO2を溶解する。この溶解によって、SiO2GeO2膜からGeO2が除去されるため、SiO2GeO2膜においてGeO2に相当する部分が、空孔19となる。そして、GeO2が除去されることによって残存したSiO2は、膜中に空孔を有する多孔質SiO2膜17となる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、ビアホールに於ける肩落ちを低減させる為、トレンチのエッチング加工途中でビアホールの側壁に保護膜を形成するのであるが、その形成工程段階を適切に選定することで、保護対象を有効に保護できるようにする。

【解決手段】低誘電率材料であるポーラスシリカからなる絶縁膜14(無機膜)を用いてデュアルダマシン加工方法を実施する場合に於いて、トレンチ24形成のエッチングを行なう際に発生するビアホール23開口エッジの肩落ちを低減させる目的で成膜される側壁保護膜31の被覆性を向上させる為、その成膜を前記エッチングの途中段階で実施する工程が含まれる。

(もっと読む)

半導体装置およびその製造方法

【課題】電界効果トランジスタに応力を作用させて高性能化する半導体装置において、信頼性を向上させる。

【解決手段】半導体基板1に形成されたnチャネル型電界効果トランジスタQnおよびpチャネル型電界効果トランジスタQpを有する半導体装置であり、両トランジスタQn,Qpを覆うようにして形成された、半導体基板1に対して応力をもたらす第1絶縁膜Z1と、第1絶縁膜Z1に接し、かつ、第1絶縁膜Z1の上からnチャネル型電界効果トランジスタQnを覆うようにして形成された、半導体基板1に対して引張応力をもたらす第2絶縁膜Z2とを有し、第1絶縁膜Z1の厚さよりも第2絶縁膜Z2の厚さの方が薄く、第1絶縁膜Z1、第2絶縁膜Z2またはその両方は、窒化シリコン膜である。

(もっと読む)

半導体装置とその製造方法

【課題】新規な特徴を有する半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板10の上方に第1絶縁膜25を形成する工程と、第1絶縁膜25の所定の深さに不純物をイオン注入することにより、第1絶縁膜25に不純物層22を形成する工程と、不純物層22を形成した後、第1絶縁膜をアニールすることにより、不純物層22をバリア絶縁膜23に改質する工程とを有する半導体装置の製造方法による。

(もっと読む)

酸化膜パターンの形成方法及びこれを用いた半導体素子のパターニング方法

【課題】酸化膜パターンの形成方法及びこれを用いた半導体素子のパターニング方法を提供する。

【解決手段】半導体基板上に酸化膜を形成する工程と、所定領域の酸化膜上に1.0×1016個/cm2以上のボロンイオンを注入する工程と、前記酸化膜における前記ボロンイオンの注入されなかった領域を湿式エッチングする工程と、を含む酸化膜パターンの形成方法とした。

(もっと読む)

半導体装置の製造方法

【課題】ディッシングの発生を防止しながら簡単な工程で平坦化を行う。

【解決手段】 上面にストッパ膜12を形成した絶縁層11を覆うようにポリシリコン層13が形成され、ポリシリコン層13の表面にポリシリコン層13よりも硬度の高い保護膜14を形成する。凸部15の保護膜14の部分に対してイオン注入が行われ、その部分の硬度が低くされる。ストッパ膜12が露呈されるまでシリコン研磨用スラリーだけを用いて化学的機械研磨し、ポリシリコン層13の表面を平坦化する。凸部15の研磨速度を速くしつつ、凹部16のポリシリコン層13を保護膜14で保護してディッシングの発生を防止する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、被加工膜の加工形状の悪化やパターンの荒れを低減し、設計デザインに対し忠実で、且つデュアルダマシン工程等にも適用可能な半導体装置の製造方法を提供することを目的とする。

【解決手段】被加工膜2上に、膜の塗布、加熱硬化を行うことで、少なくとも1以上の膜よりなる加工用マスク層(下層有機膜3及び中間層5)を形成し、加工用マスク層のうち少なくとも1つの膜に対しハードニング処理を行う加工用マスク層形成工程と、加工用マスク層上に露光用レジスト膜を塗布し、露光現像することでレジストパターン6を形成し、当該レジストパターン6をマスクに加工用マスク層をエッチングする加工用マスク層エッチング工程と、加工用マスク層エッチング工程で形成された、加工用マスク層のパターンをマスクに被加工膜2をエッチングする被加工膜エッチング工程とを備える。

(もっと読む)

100%又はそれより大きい段差被覆性を有する相互接続部金属化プロセス

【課題】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法を提供すること。

【解決手段】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法が提供される。本発明の相互接続構造体は、従来のPVDプロセス、従来のイオン化プラズマ堆積、CVD、又はALDによってバリア材料が形成される従来技術の相互接続構造体と比べると、半導体業界のための改善された技術拡張性を有する。本発明によると、構造底部のバリア材料厚(ht)より厚い、構造側壁のバリア材料厚(wt)を有する相互接続構造体が提供される。すなわち、本発明の相互接続構造体において、wt/ht比は、100%に等しいか又はそれより大きい。

(もっと読む)

機械的特性が改善された多孔性低k層を有するダマシン相互接続

【課題】集積回路に向けたシングル及びデュアルダマシン相互接続に関する技術を提供する。

【解決手段】ダマシン相互接続を製作する方法。本方法は、基板上に多孔性誘電体層を形成する段階、及び誘電体層内に少孔性誘電体副層を定めるために多孔性誘電体層の上部部分の中にポロゲン材料を与える段階によって開始される。キャップ層が少孔性誘電体副層上に形成され、第1の相互接続開口部を定めるためにキャップ層の上にレジストパターンが形成される。キャップ層及び誘電体層は、レジストパターンを通じてエッチングされ、第1の相互接続開口部を形成する。レジストパターンが除去され、第1の相互接続開口部を導電材料で充填することによって相互接続が形成される。余分な導電材料を除去するために、相互接続が平坦化される。

(もっと読む)

半導体装置の製造方法

【課題】 制御電極と電荷蓄積層との間に優れた絶縁膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11上に形成された第1の絶縁膜12と、第1の絶縁膜上に形成された電荷蓄積層13と、電荷蓄積層上に形成された第2の絶縁膜20と、第2の絶縁膜上に形成された制御電極とを備えた半導体装置の製造方法であって、第2の絶縁膜を形成する工程は、酸素及び金属元素を含有した下層絶縁膜201を形成する工程と、下層絶縁膜に対して酸化性ガスを含む雰囲気下で熱処理を施す工程と、熱処理が施された下層絶縁膜上に水素及び塩素の少なくとも一方を含んだ成膜ガスを用いて上層絶縁膜202を形成する工程とを備える。

(もっと読む)

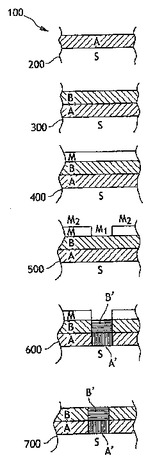

特性が制御された多層構造物の製造方法

本発明はn層の所定材料の元素状活性層(nは2以上の整数)を含む多層構造物を支持体上に製造する方法(100)に関する。この方法は、第1の元素状材料活性層の成膜工程(200)と、n番目の元素状材料活性層の成膜工程(300)とを含む方法であって、特性が制御された多層構造物を得るために、成膜されたn層の材料元素状活性層上に、n層の元素状活性層のそれぞれの個々の特性を変性させるのに適したイオン種をレジストを介して注入する単一の工程(600)を含むことを特徴とする。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】配線形成時において、エッチングストッパー膜にピンホールが発生することを防止して下層配線層Cuの溶解を抑制できる多層配線形成技術を提供する。

【解決手段】基板上に第1絶縁膜2を形成する工程と、第1絶縁膜中に表面が露出するように下層配線層1を形成する工程と、下層配線層上を含む第1絶縁膜上に、少なくとも後の工程によりコンタクトホールが形成される領域に当該領域の周辺部に比べて膜厚が大きい厚膜部10aを有する第2絶縁膜10を形成する工程と、第2絶縁膜上に少なくとも1層からなる第3絶縁膜4を形成する工程と、第3絶縁膜中および第2絶縁膜中に底面が下層配線層に達するようにコンタクトホール8を形成する工程とを備える。

(もっと読む)

41 - 60 / 83

[ Back to top ]