Fターム[5F033QQ60]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 絶縁膜 (83)

Fターム[5F033QQ60]に分類される特許

21 - 40 / 83

ビアホールの形成方法

【課題】異なる種類の絶縁体が積層された構造を有する絶縁膜に、高精度の加工形状を有するビアホールを形成することができるビアホールの形成方法を提供する。

【解決手段】

ドライエッチングによって第2の絶縁層に第1の貫通孔を形成する工程と、第1の絶縁層及び第2の絶縁層の第1の貫通孔からの露出部分を同一組成からなる絶縁体にする同一化工程と、第1の貫通孔から露出する第1の絶縁層をドライエッチングにより除去して下層配線に達するビアホールを形成する工程と、を有すること。

(もっと読む)

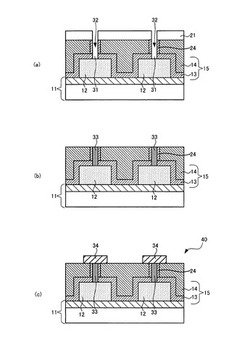

半導体装置の製造方法

【課題】信頼性の高いドレインコンタクトを有する半導体装置の製造方法を提供する。

【解決手段】第1ドレインコンタクト14を形成する工程と、第1ドレインコンタクト14に接続された第2ドレインコンタクト15を形成する工程と、第2ドレインコンタクト15に接続された配線16を形成する工程と、配線16をマスクとして自己整合的に、少なくとも第2ドレインコンタクト15の近傍の第2層間絶縁膜33に、第1層間絶縁膜13と第2層間絶縁膜33との界面34より深い位置まで不純物イオンを注入し、界面34に残置されている異物32をアモルファス化する工程と、不純物イオンが注入された第1および第2層間絶縁膜13、33をエッチングして異物32を露出させ、異物32を除去する工程と、第1絶縁膜13上に配線16を覆うように第3層間絶縁膜36を形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】SiN層にPおよびOを注入する工程と、前記SiN層に注入されたPおよびOをH2Oと反応させ、前記SiN層をエッチングする工程とを有する方法により、半導体装置を製造する。特に、半導体装置を形成するにあたり、狭スペースで高アスペクト比の溝サイドウォールを形成する工程や、埋め込み型ビット線を形成する工程に、上記のようにSiN層をエッチングすることができる。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の表面に対するダメージを防ぎ、配線膜厚を均一に制御することにより、配線間ショート及び信頼性劣化を防止できるようにする。

【解決手段】半導体基板101の上に絶縁膜102を形成し、絶縁膜102の内部にイオン注入法によりイオン注入層103を形成し、絶縁膜102に少なくともイオン注入層103に達する深さの配線溝104を形成し、配線溝104に導電膜107Aを形成し、絶縁膜102及び導電膜107Aにおけるイオン注入層103よりも上に形成されている領域を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】平坦な表面を有する層間絶縁膜を短時間で形成することができ、また、層間絶縁膜の厚さの増大を招くことなく、金属イオンによる半導体基板の汚染に対する長期信頼性を保証することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板2と、半導体基板2上に形成された層間絶縁膜8とを備えている。そして、層間絶縁膜8は、半導体基板2側から順に、HDP膜10、ゲッタリング層12およびNSG膜11が積層された構造を有している。ゲッタリング層12は、金属イオン、とくに可動イオンを捕獲する性質を有している。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上にチャネル長方向が<−110>方向に沿って配置される第1絶縁ゲート型電界効果トランジスタpMOS1と、前記半導体基板上にチャネル長方向が<−110>方向に沿って配置され、前記第1絶縁ゲート型電界効果トランジスタと前記チャネル長方向に隣接する第2絶縁ゲート型電界効果トランジスタnMOS1と、前記第1,第2絶縁ゲート型電界効果トランジスタ上を覆うように設けられ、正の膨張係数を有し、前記第1,第2絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加えピエゾ材料を含む第1ライナー絶縁膜11−1とを具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ソフトエラーを低減することが可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 電極パッドを有する半導体チップが形成される半導体基板と、前記電極パッドに設けられる内部接続端子と、前記複数の半導体チップと前記内部接続端子とを覆うように設けられる絶縁層と、前記絶縁層を挟んで前記内部接続端子と接続される配線パターンと、を有する半導体装置であって、前記絶縁層は、ポリイミド及び/又はポリイミド系化合物等のα線を遮蔽する材料を含んで構成されることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】接合リーク電流の低減が図られる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に所定の深さのトレンチが形成され、そのトレンチ5内に分離酸化膜6が形成される。不純物イオンを注入することにより、分離酸化膜6の表面に、分離酸化膜6のエッチング特性とは異なるエッチング特性を有する改質層7が形成される。半導体基板の領域に、トランジスタ等の所定の半導体素子が形成される。半導体基板1上に、エッチングストッパ膜10および層間絶縁膜16が形成される。その層間絶縁膜16およびエッチングストッパ膜に、金属シリサイド9の表面を露出するコンタクトホール16a,16bが形成される。コンタクトホール16a,16b内にプラグ18a,18bが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁耐性を向上することが可能な半導体装置の製造装置を提供する。

【解決手段】半導体基板上に形成され、トレンチが形成された層間絶縁膜と、前記トレンチの内面に成膜された第1の拡散防止膜と、前記トレンチ内に前記第1の拡散防止膜を介して埋め込まれたCu配線層と、前記層間絶縁膜上および前記Cu配線層上に形成された第2の拡散防止膜と、前記Cu配線層と前記第2の拡散防止膜との間の第1の界面に形成され、Cuを主成分とする合金層と、Cu以外の前記合金層を構成する元素と同じ種類の元素が前記層間絶縁膜の上層部と反応して前記層間絶縁膜と前記第2の拡散防止膜との間の第2の界面に形成された前記第1の反応層と、Cu以外の前記合金層を構成する元素と同じ種類の元素が前記第2の拡散防止膜の下層部と反応して前記第1の界面および前記第2の界面に形成された第2の反応層と、を備える。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

半導体装置及びその作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子と、半導体素子上の絶縁膜と、絶縁膜中に、欠陥の多い領域と欠陥の少ない領域とを有し、欠陥の多い領域は、金属元素が拡散され、絶縁膜の表面の一部と裏面の一部をつなぐ導電領域である半導体装置、及び、基板上に半導体素子を形成し、半導体素子上に絶縁膜を形成し、絶縁膜上に、半導体素子と電気的に接続された第1の導電膜を形成し、絶縁膜中にイオンを添加して、あるいはレーザビームを照射して、欠陥の多い領域を形成し、欠陥の多い領域上に、金属元素を含む導電材料を形成し、欠陥の多い領域に、金属元素を拡散させ、絶縁膜中に、第1の導電膜と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】Nチャネル領域内、およびPチャネル領域内のチャネルに印加するストレスを制御でき、面積の増加抑制および歩留まりの低下を実現できる半導体装置およびその製造方法を提供する。

【解決手段】Nチャネル領域201内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断する。Pチャネル領域202内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断後、酸素などをイオン注入する。その後、熱処理を加えてNチャネル領域201内のコンタクトライナー513を収縮させてnチャネルコンタクトライナー518を形成し、Pチャネル領域202内のコンタクトライナー513を膨張させてpチャネルコンタクトライナー519を形成する。

(もっと読む)

半導体装置の製造方法

【課題】歪み技術を利用した性能のよい半導体装置を低コストで製造する。

【解決手段】シリコン基板10上のnMOS形成領域12a及びpMOS形成領域12bにそれぞれゲート電極15a,15bを形成し、pMOS形成領域12bを覆い、フォトレジストマスク18を形成して、イオン注入によりnMOSのソース/ドレイン領域17aを形成するとともに、ゲート電極15aをアモルファス化し、フォトレジストマスク18を除去した後に、シリコン基板10上に、ゲート電極15a,15bを覆うように、引っ張り歪みを有するキャップ膜19を形成し、nMOS形成領域12aを覆うようにフォトレジストマスク20を形成し、pMOS形成領域12bのキャップ膜19に不純物をイオン注入し、フォトレジストマスク20を除去した後に、アニール処理を行い、nMOSのゲート電極15a下のチャネルに対し、チャネル深さ方向の圧縮歪みを加える。

(もっと読む)

半導体素子の製造方法

【課題】 本発明は、トンネル酸化膜の形成時に酸化膜に窒素を蓄積させた後、後続で酸素を注入するための工程を行ってSi−N結合をSi−O−N結合に変更することにより、窒素プロファイル(N profile)の変化による特性劣化の防止、電気的ストレスの緩和及び酸素密度の増加などを通じてサイクリング(cycling)及び電荷保存(retention)特性などの素子特性を向上させることができる半導体素子の製造方法を提供するものである。

【解決手段】 半導体基板上に第1の絶縁膜を形成する段階と、前記半導体基板と前記第1の絶縁膜の界面に窒素を蓄積させて第2の絶縁膜を形成する段階と、前記第2の絶縁膜に酸素を注入して第3の絶縁膜に変更させる段階とを含む構成としたことを特徴とする。

(もっと読む)

絶縁膜形成用組成物および電子デバイス

【課題】 低誘電性であり、かつ塗膜形成後の経時によって一旦上昇した誘電率を加熱処理によって回復させる能力(k値回復性)を良化させた絶縁膜形成用組成物を提供する。

【解決手段】 (A)少なくとも一種の有機ポリマーまたは2つ以上の不飽和基を置換基として有するカゴ型シルセスキオキサン化合物を重合させた高分子化合物、(B)溶剤、(C)下記一般式(C-1)〜(C-3)の何れかで表される少なくとも一種の有機シリコーン化合物を含有することを特徴とする。

【化1】

(R1はメチル基等を表し、x1は0〜95mol%, x2は5〜100mol%、x1+ x2 = 100mol%であり、R2, R3はアルキル基等を、R4はメチル基等を表し、X3は5〜100mol%, x4は0〜95mol%、x3 +

x4 = 100mol%であり、Rfはフルオロアルキル基を表し、x5は0〜95mol%, yは5〜100mol%、x5 + x6 = 100mol%である。)

(もっと読む)

21 - 40 / 83

[ Back to top ]