Fターム[5F033QQ89]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 酸化処理 (296)

Fターム[5F033QQ89]に分類される特許

281 - 296 / 296

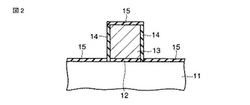

半導体装置の製造方法

【課題】 所望の適正な加工状態を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11の主面上にゲート絶縁膜12を介してゲート構造13を形成する工程と、ゲート構造の上面、ゲート構造の側面及び半導体基板の主面を覆う第1の絶縁膜14を形成する工程と、フッ素を含まないガスを用いた異方性のプラズマ処理によりゲート構造の上面及び半導体基板の主面を覆う第1の絶縁膜を改質する工程と、改質された第1の絶縁膜15を除去する工程とを備える。

(もっと読む)

アクティブマトリクス型表示装置およびその製造方法

【課題】 電極の段切れを防止して表示品位の優れたアクティブマトリクス型表示装置およびその製造方法を提供する。

【解決手段】 アクティブマトリクス型表示装置は、接続配線4と、貫通孔33を含む無機絶縁膜21と、コンタクトホール32を含む有機絶縁膜22と、画素メタル電極6とを備える。貫通孔33は、接続配線4の表面においてコンタクトホール32よりも大きくなるように形成され、有機絶縁膜22は、貫通孔33とコンタクトホール32とに挟まれるように形成された介在部31を含む。接続配線4は、表面のうち少なくとも介在部31が接する領域に形成された酸化膜を含む。

(もっと読む)

半導体装置の製造方法、半導体製造装置及び半導体装置

【課題】 銅膜を酸化させその酸化物を酸もしくはアルカリなどで除去することにより銅膜の表面をエッチングする方法において、エッチング処理を行った後の銅膜表面が荒れてしまうことが少なく、少ない工程で短時間に精度良く行うことができる半導体装置の製造方法、半導体製造装置及び半導体装置を提供する。

【解決手段】 半導体基板上の絶縁膜に形成された配線溝又はコンタクト孔に配線金属を堆積して前記配線溝又はコンタクト孔に充填する工程と、前記配線金属を研磨して前記絶縁膜を露出する工程と、前記半導体基板を洗浄する工程と、前記配線溝又はコンタクト孔に埋め込まれた前記配線金属表面をリセスエッチングする工程を有している。前記研磨工程、前記洗浄工程及び前記リセスエッチング工程の少なくとも2工程で用いる薬液の主たる成分が同一である。

(もっと読む)

マスク材料の変換

ピッチが増倍されたスペーサ等のマスクパターンの寸法が、パターン内のフィーチャが形成された後で、フィーチャの制御された成長によって制御される。ピッチが増倍されたスペーサ175aのパターンを形成するために、まず、半導体基板110の上にマンドレルのパターンを形成する。次に、マンドレルの上に材料のブランケット層を堆積させ、スペーサ材料を水平面から選択的に除去することにより、マンドレルの側壁にスペーサを形成する。その後、マンドレルを選択的に除去し、自立スペーサのパターンを後に残す。スペーサは、酸化するとサイズが大きくなることで知られているポリシリコンやアモルファスシリコン等の材料を含む。スペーサを酸化して所望の幅95に成長させる。所望の幅に達した後、スペーサ175aは、下にある層150及び基板110をパターニングするためのマスクとして用いられ得る。有利なことに、酸化によってスペーサ175aを成長させるため、マンドレルの上に薄いブランケット層を堆積することができ、それにより、よりコンフォーマルなブランケット層を堆積させ、スペーサ形成用の処理窓を拡張することが可能となる。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】 プラズマ処理によりシリコン表面に形成される、SiCを含む変質層を、シリコン表面の侵食を最小限に抑止しながら除去する。

【解決手段】 前記変質層を、酸素ラジカルに、前記半導体表面のSi原子に結合してSi原子と酸素原子との間の二重結合の形成を阻害するような元素の活性種を添加して改質し、形成された改質層をウェットエッチングにより除去する。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】 信頼性の向上を図ることにある。

【解決手段】 強誘電体メモリの製造方法は、(a)基体10の上方に形成された絶縁層20に、第1及び第2のコンタクトホール22,24を形成すること、(b)第1及び第2のコンタクトホール22,24のそれぞれの内部に、絶縁層20の上面よりも低い上面を有するプラグ42,44を形成すること、(c)第1及び第2のコンタクトホール22,24のそれぞれのプラグ42,44の上方を含む領域に、バリア層51を形成すること、(d)下部電極82、強誘電体層84及び上部電極86を順に積層して積層体81を形成すること、(e)積層体81をエッチングすることによって、第1のコンタクトホール22のプラグ42の上方を含む領域に、強誘電体キャパシタ80を形成すること、(f)第2のコンタクトホール24のプラグ44の上方を含む領域に、被覆層90を形成すること、(g)酸素雰囲気下においてアニール処理を行うこと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンプラグ上のプラグコンタクトの抵抗ばらつきを低減する。

【解決手段】半導体基板上の第1の絶縁膜12中にポリシリコンよりなるプラグ13を形成する工程と、ポリシリコンよりなるプラグの上に、酸化物層14を形成する工程と、ポリシリコンよりなるプラグと第1の絶縁膜の上に、第2の絶縁膜16を形成する工程と、第2の絶縁膜の上に、所定の形状にパターニングされたレジストを形成する工程と、パターニングされたレジストをマスクとして第2の絶縁膜の中に、コンタクト孔17bを設ける工程と、酸化物層を、ポリシリコンよりなるプラグの上に残した状態で、コンタクト孔の内部を洗浄する工程と、酸化物層を除去した後に、コンタクト孔の内部を導電性金属19で埋め込むことにより導電性金属よりなるプラグを形成する工程とを有する。

(もっと読む)

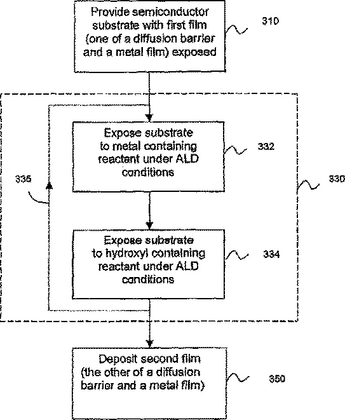

酸素架橋構造及び方法

拡散バリア膜と金属膜との間の接着性を改善するための方法が提唱される。拡散バリア膜及び金属膜の両方は、いずれかのシークエンスで、半導体基板上へ堆積される。拡散バリア膜又は金属膜のいずれか一方である第一膜(第一膜は、基板の表面領域の少なくとも一部で暴露される)を有する基板は、酸素含有リアクタントに暴露され、第一膜の露出部分に酸素含有基又は酸素原子の約1の単層の表面終端を生成する。次いで、第二膜(これは、拡散バリア膜及び金属膜のうち他方である)が基板上に堆積される。さらに、酸素架橋構造が提唱され、該構造は、拡散バリア膜及び該拡散バリア膜との界面を有する金属膜を含む(ここで、界面は、酸素原子の単層を含有する)。

【課題】

【解決手段】  (もっと読む)

(もっと読む)

基板の無電解めっき方法および基板上の金属パターン形成方法

【課題】 レジストを用い、無電解めっきによって基板の表面に金属パターンを形成する方法であって、基板表面への密着性に優れた精細な金属パターンを得ることができるとともに、レジストパターンおよびその上の無電解めっき被膜を同時に除去すること、およびレジストパターン上の無電解めっき被膜のみを除去することのいずれもが容易になる方法を提供する。

【解決手段】 レジストパターンが形成された基板の表面全面を酸化処理(例えば紫外線照射)し、次いでレジストパターンの最上層を除去した後、基板の表面全面に無電解めっきを行う。

(もっと読む)

半導体素子のストレージノードコンタクトの形成方法

【課題】ランディングプラグコンタクトとストレージノードコンタクトとの間の不整合を防止し、接触抵抗を改善することができる半導体素子のストレージノードコンタクトの形成方法を提供すること。

【解決手段】複数のゲート23とソース/ドレーン領域25が形成された半導体基板21のゲート間に酸化膜26とランディングプラグコンタクトを形成するステップと、ランディングプラグコンタクト及びゲートを含んだ半導体基板の全面上に層間絶縁膜29を形成するステップと、層間絶縁膜をエッチングしてランディングプラグコンタクトを露出させる第1ストレージノードコンタクトホールを形成するステップと、露出されたランディングプラグコンタクトと酸化膜を除去し、第2ストレージノードコンタクトホールを形成するステップと、第2ストレージノードコンタクトホール内にポリシリコンを埋め込んでストレージノードコンタクト30を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】加工パターンの疎密に依存することなく面内均一に精度良好なパターン加工行うことが可能なエッチング工程を備えた半導体装置の製造方法を提供する。

【解決手段】基板11上にSiOCH系絶縁膜からなる被エッチング膜13を形成し、マスクパターン15上からのプラズマ処理を行う。これにより、マスクパターン15から露出している被エッチング膜13部分をSiO2化して改質部13bを形成する前処理を行う。次に、マスクパターン15およびSiOCH系材料からなる未改質部13aに対して選択的に改質部13bをエッチング除去する。

(もっと読む)

成膜方法、SiO2膜、電子部品および電子機器

【課題】所定パターンのSiO2膜を容易かつ安価に形成し得る成膜方法、かかる成膜方法により形成されたSiO2膜、このSiO2膜を備える電子部品および電子機器を提供すること。

【解決手段】本発明の成膜方法は、所定パターンの第2の層間絶縁層(SiO2膜)5を形成する方法であり、主としてポリオルガノシロキサンで構成されるポリオルガノシロキサン膜を形成する第1の工程と、ポリオルガノシロキサン膜の前記所定パターンに対応する領域に、第1のSiO2化処理を施して、前記領域に存在するポリオルガノシロキサンをSiO2に変化させる第2の工程と、SiO2に変化した前記領域をアルカリ溶液により除去する第3の工程と、第3の工程において残存するポリオルガノシロキサン膜に、第2のSiO2化処理を施して、ポリオルガノシロキサンをSiO2に変化させることにより、第2の層間絶縁層5を得る第4の工程とを有する。

(もっと読む)

基板上に多機能誘電体層を形成する方法

本発明は、多機能誘電体層を基板上、特に基板上に露出している金属配線系上に形成する方法に関する。本発明の目的は、銅による配線を形成するための多機能パッシベーション層を容易に形成する方法を提供するとともに、エレクトロマイグレーション、ストレスマイグレーション、および接着性を向上させる方法を提供することにある。本発明によれば、更なる金属層(5)を、露出した金属配線(3)の表面上に堆積することによって、本発明の目的は達せられる。この金属層は少なくともその一部が非導電性の金属酸化物に変換され、誘電体層となっている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

配線構造

【課題】 高い周波数が印加され、数cm〜数10cmの長さを有する配線の抵抗を低減し、伝送される信号波形のなまりを低減する。

【解決手段】 高周波が印加される配線111は、層間絶縁膜107を介して、配線111の線方向にそって複数設けられたコンタクトホールにより配線106と電気的に並列接続している配線構造を採用する。その配線構造を周辺回路一体型アクティブマトリクス型液晶表示装置の周辺回路に用いることで、高周波信号が印加される配線において信号波形のなまりを低減できる。

(もっと読む)

配線構造および基板の製造方法ならびに液晶表示装置およびその製造方法

【課題】 短絡や断線を回避しながら、基板の接続配線の抵抗の均一化を図る。

【解決手段】 基板の各信号配線3と素子側端子8とを接続する接続配線7を、それぞれ所定の線幅を有する複数の接続部である第1の区間7a、第2の区間7bから構成し、該複数の接続部の膜厚を調整したり、第1の区間7aに積層配線19を設けて多層構造とすることにより、各接続配線7で全抵抗が略同じになるように構成する。これにより、接続配線7の最大線幅と最小線幅の差を約2倍程度に抑えることができるため、太い接続配線7における短絡や、細い接続配線7における断線を回避しながら、各接続配線7の抵抗の均一化を図ることができる。

(もっと読む)

281 - 296 / 296

[ Back to top ]