Fターム[5F033QQ89]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 酸化処理 (296)

Fターム[5F033QQ89]に分類される特許

81 - 100 / 296

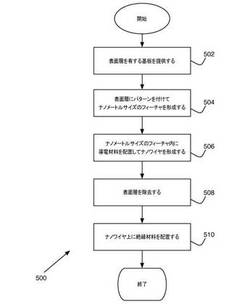

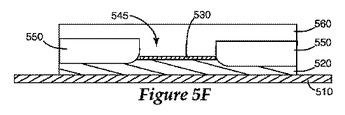

ナノワイヤの製造方法及び集積回路

【課題】低温プロセスのナノワイヤの製造を実現する。

【解決手段】封入されたナノワイヤを製造する方法であって、表面層を有する基板を提供することと、前記表面層にパターンを付け、ナノメートルサイズのフィーチャを形成することと、前記ナノメートルサイズのフィーチャ内に導電材料を配置し、前記基板上にナノワイヤを形成することと、前記表面層を除去することと、前記ナノワイヤ上に絶縁材料を配置することと、を含み、前記ナノワイヤ上に前記絶縁材料を配置することは、約350℃未満の温度で前記ナノワイヤ上に絶縁材料を配置することを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】印加電界の履歴によって抵抗値が変化する抵抗変化層を有するスイッチ素子を多層配線中に形成し、かつ配線又は抵抗変化層の表面がダメージを受けることを抑制できるようにする。

【解決手段】この半導体装置は、第1配線層12、第2配線層16、及びスイッチビア35を備える。第1配線層12は第1配線32を有しており、第2配線層16は第2配線39を有している。スイッチビア35は、第1配線32と第2配線39を接続する。またスイッチビア35は、少なくとも底部に、抵抗変化層33を有しているスイッチ素子を有している。抵抗変化層33は、電界印加履歴に応じて抵抗値が変化する。

(もっと読む)

表示デバイスの製造方法

【課題】Al合金膜の腐食を抑制でき、透明導電膜との接触電気抵抗も低減された表示デバイスを製造する。

【解決手段】下記(1)〜(4)の工程によってAl合金膜を透明導電膜と直接接触させる。(1)Alよりも貴な金属元素を含むAl合金膜を形成する第1の工程、(2)フォトリソグラフィおよびドライエッチングによってコンタクトホールを形成する第2の工程、(3)フォトリソグラフィで生成したフォトレジストの剥離を行なう第3の工程、(4)透明導電膜を形成する第4の工程と、をこの順序で包含し、第2の工程は、オーバーエッチングにおけるガスの流量比を、SF6/(SF6+O2)の比率で30%以下に制御して前記Al合金膜の表面をAlの酸化物で覆う工程を含み、第3の工程は、pH10.5以上のアルカリ溶液に接触させて前記Alの酸化物を除去する工程を含む。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 反射防止膜を使用しなくてもアルミニウム配線パターンを高精度に形成できる半導体装置の製造方法を提供する。

【解決手段】 半導体基板10上にアルミニウム層もしくはアルミニウム合金層3をバリアメタル層2を介して形成し、アルミニウム合金層3の表面にドライエッチングガスを用いて均一な微細凹凸を有する表面層3aを形成する。そして、アルミニウム合金層上にフォトレジストを塗布し、フォトレジストを配線パターンを有するフォトマスクを用いて露光し、現像して配線パターンを形成し、フォトレジストをマスクにして、アルミニウム合金層をエッチングしアルミニウム配線5を形成する。表面層3aを窒素および酸素条件下でアッシング処理して表面層3aの凹凸より細かい凹凸を有する酸化膜を形成することによって反射率を大きく低下させることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の結晶欠陥発生を抑制することができる半導体装置の製造方法を提供する。

【解決手段】ウエハ上にSTI用のトレンチを形成し、そのトレンチに絶縁膜を埋め込む。次に、ウエハ表面に酸素を導入する。酸素導入は、酸素100%雰囲気下で、1100℃、60秒間、ウエハ表面にRTO(Rapid Thermal Oxidation)を行う。その後、高温アニールを行う。SRAM製造プロセスにおいて、転位が発生するおそれのある高温アニール工程とソース/ドレイン部のイオン注入工程の前に酸素導入を行うため、ウエハの結晶強度を高めることができ、アニール工程やイオン注入工程によって発生する転位を抑えることができる。

(もっと読む)

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

電気的固体装置、電気光学装置、および電気的固体装置の製造方法

【課題】アルミニウム系の配線材料として用いた場合でも、十分な耐ヒロック性に備えるとともに、ドライエッチングを適用でき、さらに、レジストマスクを剥離する際に用いる剥離液によって、配線がエッチングされることのない電気的固体装置、電気光学装置、および電気的固体装置の製造方法を提供すること。

【解決手段】電気光学装置100において、素子基板10上に走査線3aなどの配線を形成するにあたって、ネオジウムを2atm%未満含有するアルミニウム合金膜を用いるとともに、走査線3aの上面および側面を酸化して表面保護膜31aを形成する。このため、走査線3aは、耐ヒロック性が高いとともに、表面保護膜31a、31eによってアルカリ性の剥離液から保護される。

(もっと読む)

シリコン酸化膜の形成方法および不揮発性半導体記憶装置の製造方法

【課題】低温で良好な絶縁膜であるシリコン酸化膜を形成する。

【解決手段】シリコン基板1上にトレンチ1a、1bを形成し、シラザン結合を有するポリマーを有機溶媒に溶かした塗布剤を塗布して塗布膜を形成する。塗布膜に含まれる有機溶媒を気化させてポリマー膜を形成する。ポリマー膜に90℃以下の温度で紫外線を照射し、そのポリマー膜を50℃以上80℃未満の温度の純水または水溶液中に浸漬することによってシリコン酸化膜3に転換する。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】第2バリア膜13の形成後に、SiH4を含むガスを用いたPECVD法により、Cu層20上にSiおよびOを含む絶縁材料からなる犠牲層21が積層される。犠牲層21にSiおよびOが含まれるので、犠牲層21の積層過程で、Cu層20と犠牲層21との界面にMnSiOからなる反応生成膜22が生じる。この反応生成膜22の生成にMnが使用されることにより、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体装置の製造方法

【課題】 CSPと呼ばれる半導体装置において、封止膜が配線の表面および柱状電極の外周面から剥離しにくいようにし、且つ、配線間でショートが発生しにくいようにする。

【解決手段】 銅からなる配線7の表面および銅からなる柱状電極10の外周面には針状構造の酸化銅膜11が設けられている。これにより、酸化銅膜11が無い場合と比較して、エポキシ系樹脂等からなる封止膜12が配線7の表面および柱状電極10の外周面から剥離しにくいようにすることができる。また、酸化銅膜11を形成する前に、配線7下以外の領域における導電性を有する変質層Cを完全に除去することにより、変質層Cに起因する配線7間でのショートの発生を確実に防止することができる。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

固体撮像装置、その製造方法および撮像装置

【課題】本発明は、画素部のMOSトランジスタ上で異なる2層のシリサイドブロック膜の一部が重なるように形成して、白傷、暗電流を低減することを可能にする。

【解決手段】半導体基板11に、光電変換部21を備えた画素部12とその周辺に形成された周辺回路部13を有し、画素部12のゲート電極32の側壁にサイドウォール形成膜で形成された第1サイドウォール33と、周辺回路部13のゲート電極52の側壁にサイドウォール形成膜で形成された第2サイドウォール53と、光電変換部21上および画素部12のMOSトランジスタ30の一部上にサイドウォール形成膜で形成された第1シリサイドブロック膜71と、画素部12のMOSトランジスタ30上に、第1シリサイドブロック膜71の一部上に重なる第2シリサイドブロック膜72を有し、第1、第2シリサイドブロック膜71、72で画素部12のMOSトランジスタ30上が被覆されている。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の配線同士間の容量を低くしたままで、機械強度の低下を防ぐことが可能な半導体装置およびその製造方法を提供すること目的とする。

【解決手段】本発明に係る半導体装置およびその製造方法によれば、下地層1,2,3上に形成された第1の配線層6と、第1の配線層6と同一面内に形成され、所定の温度で気化する配線層間膜4とを備える。そして、第1の配線層6上、および、配線層間膜4上に形成された拡散防止膜7を備え、第1の配線層6に沿って第1の配線層6と同一面内にエアギャップ8が設けられている。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】性能劣化を招く金属元素の半導体基板への侵入及び拡散を防ぐことのできる半導体基板の製造方法および半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体基板の製造方法は、半導体基板1の両面および側面に窒化膜2を形成する工程と、前記窒化膜2上の全面に、シリコンを含む酸化膜3および所定の金属を含む前駆体膜4Aを積層する工程と、前記酸化膜3と前記前駆体膜4Aとを反応させることにより、前記シリコンおよび前記所定の金属を含む自己形成バリア膜4を自己整合的に形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、絶縁膜の誘電率を低く維持すると共に、半導体装置の信頼性を高めること。

【解決手段】シリコン基板1の上方に層間絶縁膜29を形成する工程と、層間絶縁膜29に配線溝29aを形成する工程と、層間絶縁膜29の上面と配線溝29aの中とに導電膜27を形成する工程と、導電膜27を研磨することにより、層間絶縁膜29の上面から導電膜27を除去すると共に、配線溝29aの中に導電膜27を残す工程と、導電膜27の表面を還元性プラズマに曝す工程と、導電膜27の表面にシリサイド層34を形成する工程と、シリサイド層34の表面に窒化層36を形成する工程と、炭素を含むガス又は液に層間絶縁膜29の上面を曝す工程と、層間絶縁膜29の上面に紫外線を照射する工程と、導電膜27の上にバリア絶縁膜40を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

銅の異方性ドライエッチング方法および装置

【課題】ハロゲンによる銅の腐食を生じさせずに銅を異方性エッチングすることができる銅の異方性ドライエッチング方法を提供すること。

【解決手段】基板に形成された銅膜を異方的にドライエッチングする銅の異方性ドライエッチング方法は、銅膜に対して異方性酸化処理を施す工程と、酸化処理によって形成された酸化銅をハロゲンを含有しない有機酸によりドライエッチングする工程とを含む。

(もっと読む)

半導体装置、及びその製造方法

【課題】トランジスタ特性を劣化させずに形成される小型の半導体装置、及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成されるゲート絶縁膜と、前記半導体基板上に前記ゲート絶縁膜を介して形成されるゲート電極と、前記ゲート電極の上面に形成される第1窒化シリコン膜と、前記ゲート電極の側面に形成される保護絶縁膜と、前記保護絶縁膜の側面に形成される第2窒化シリコン膜と、前記保護絶縁膜の上面に形成され、その底面が前記第1窒化シリコン膜の底面よりも上部に形成される第3窒化シリコン膜とを備える。

(もっと読む)

半導体装置の製造方法

【課題】Low−K膜へのダメージを抑制するとともに、フローが冗長化せずかつ微細化にも対応可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】少なくとも1層以上の層間膜を備える半導体装置の製造方法であって、(a)層間膜であるLow−K膜102上に形成されたマスクを用いて層間膜にトレンチ開口部110を形成する工程と、(b)アッシングプロセスによりマスクを除去すると同時にビア開口部106およびトレンチ開口部110に側壁保護膜111を生成する工程を備える。さらに、(c)ビア開口部106およびトレンチ開口部110にCuを埋め込む工程を備えて構成される。

(もっと読む)

半導体装置の製造方法

【課題】pMOSトランジスタ領域の窒化膜除去とnMOS側への後退抑制を両立する半導体装置の製造方法を得る事を目的とする。

【解決手段】本発明の一実施形態に係る半導体装置の製造方法は、(a)窒化膜16の表面に選択的にレジスト膜17を成膜する工程、(b)レジスト膜17をマスクとして窒化膜16をエッチングすると同時にレジスト膜17をもエッチングし、薄膜化され端面が退避されたレジスト膜17に覆われた窒化膜16を残す工程を備えて構成される。残される窒化膜16に対する工程(a)におけるレジスト膜17のオーバー露光量は50nm以上であり、工程(b)における窒化膜16のレジスト膜17に対する選択比は0.8〜1.2である。

(もっと読む)

81 - 100 / 296

[ Back to top ]