Fターム[5F033VV04]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 電源線 (325)

Fターム[5F033VV04]に分類される特許

121 - 140 / 325

半導体装置

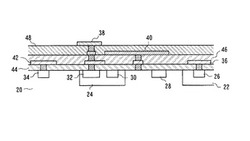

【課題】別々の配線から電源電力が供給される半導体素子が形成された互いに独立した複数のウェルを配線の延設方向に沿って隣り合わせて配置することを可能とする。

【解決手段】半導体基板20の第1ウェル領域22に形成された複数の半導体素子の少なくとも一部に電源電力を供給する第1配線36と、第1配線36上に形成された第1絶縁層46と、半導体基板20の第1ウェル領域22とは独立している第2ウェル領域24に形成された複数の半導体素子の少なくとも一部に電源電力を供給する第2配線38と、を設け、第1配線36と第2配線38とを第1絶縁層46によって電気的に絶縁する。

(もっと読む)

半導体装置

【課題】電源供給能力が高い半導体装置を提供する。

【解決手段】本発明の半導体装置1(100)は、機能回路21が形成された半導体基板2と、機能回路21の中央部Oの直上位置近傍を通る基幹配線33と、基幹配線33の端部に接続された電源パッド4と、機能回路21の略中央部と基幹配線33とを接続する接続配線34、5、6と、を備え、基幹配線33と電源パッド4とは同一層に形成される。このような構成により、半導体基板の機能回路の中央部近傍に効率良く電源供給を行うことができ、電源供給能力が高い。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】小型化の進んだ回路セルでも回路信頼性の低下を防止できる回路レイアウトの設計方法を提供する。

【解決手段】ゲート電極1に電位差の大きい電源電位あるいは基準電位からのノイズの影響が及んで誤動作を起こしてしまうことを防ぐために、ゲート電極1に接続するプラグ5と電源電位あるいは基準電位が供給されるプラグ6との間は、プラグ5に電源電位あるいは基準電位からのノイズの影響が及ばない十分な距離だけ離間させるために、配線4下にて等間隔で配置されているプラグ6のうち、プラグ5(5A)と十分離間していない配置位置6Aに配置されるプラグ6のみを平面レイアウトの設計時に消去する。

(もっと読む)

3−D積層型デバイスのESD保護を可能にするシステム及び方法

【解決手段】静電気放電(ESD)保護デバイスが、積層型半導体ダイのアクティブレイヤ間の縦型の空間に形成され、これにより、そうでなければ通信目的のためにしか使用されないであろう空間を利用する。シリコン貫通ビア(TSV:through silicon via)の縦型の表面領域は、ESDイベントに起因する大電圧を緩和するために使用される。一実施形態では、ESDダイオードは、積層型デバイスの半導体ダイのアクティブレイヤ間の縦型TSV内に形成される。このESDダイオードは、積層の半導体ダイの両方の上の回路によって共有され、これによって空間を節約し、そしてESD保護回路によって必要とされるダイ面積を低減し得る。 (もっと読む)

半導体集積回路及びその設計方法

【課題】デカップリングセルの配置場所を膨大な処理時間をかけて算出する必要が無く、電圧降下やノイズを効果的に防止できる位置にデカップリングセルを配置できる。

【解決手段】半導体集積回路100は、第1電位及び第2電位のセル用の電源配線101,102と、第1電位及び第2電位のセル用電源配線に垂直な方向に配置された第1電源配線103及び第2電源配線104と、スタンダードセル105と、デカップリングセル106とから構成される。第1電源配線103には第1電位、すなわち電源電位が供給され、第2電源配線104には第2電位、すなわちグランド電位が供給される。デカップリングセル106は、第2電源配線104の下に配置され、第1電位と第2電位が供給されている。スタンダードセル105の配置領域は、デカップリングセル106の配置部分以外の領域である。

(もっと読む)

半導体集積回路

【課題】配線の混雑を減少し、配線効率を向上させることができる電源配線構造を有する半導体集積回路を提供する。

【解決手段】主電源配線層と中間電源配線層との間には、第1の主電源配線と重なる位置に、第1の主電源配線と第1の中間電源配線とを接続する第1の中間接続ビアが設けられ、第2の主電源配線と重なる位置に、第2の主電源配線と第2の中間電源配線とを接続する第2の中間接続ビアが設けられる。中間電源配線層と副電源配線層との間には、第1の中間電源配線と第1の副電源配線とを接続する第1の副接続ビアと、第2の中間電源配線と第2の副電源配線とを接続する第2の副接続ビアとが、それぞれ複数、第1の方向に並ぶ副接続ビア列が、第2の方向に複数配置される。中間電源配線層の第2の中間電源配線には、第2の中間接続ビアと第2の副接続ビアとを接続する接続配線が含まれる。

(もっと読む)

半導体記憶装置

【課題】不良解析の際に、メモリセルのレイアウトを制限したり、工程数を増加することなく、メモリセル数を数えやすくすること。

【解決手段】半導体基板2上にメモリセル3aの繰り返しパターンが形成されたメモリセルアレイ領域3を有し、メモリセルアレイ領域3上に形成された所定層の電源配線4a、接地配線4bを、少なくともメモリセルアレイ領域3において、メモリセル3aの配置と対応させて縦方向及び横方向に格子状にレイアウトしている。

(もっと読む)

多層配線装置

【課題】本発明は、微細ピッチ多層配線構造を用いた並走配線間容量によるデカップリング容量において、高周波,高速特性に優れた大きなデカップリング容量を形成できるようにすることを最も主要な特徴とする。

【解決手段】たとえば、同一方向にピッチ配列された複数の配線M1a〜M1h,M2a〜M2f,M3a〜M3hの、そのピッチ配列の方向が互いに交差するように配線層M1,M2,M3を積層させる。そして、各配線層M1,M2,M3の、隣り合う配線におのおの異なる電位VDD,VSSが供給されるように、配線層M1,M2,M3の相互を接続してなる構成となっている。

(もっと読む)

半導体素子の製造方法および半導体素子

【解決手段】半導体素子の製造方法および半導体素子。接続パッド(7)がSOI基板(1)の絶縁層(2)に配置される。接続パッドの上部に形成されるコンタクトホール開口部(9)は、その側壁及び接続パッド上に、上縁が頂部金属(12)に接触する金属膜(11)を備える。 (もっと読む)

マルチダイ集積回路デバイスおよび方法

【課題】複数のダイを3次元集積回路パッケージとして積層する際に、貫通シリコンビアのコンタクトパッドの効率的な配置が可能なデバイスを提供する。

【解決手段】メモリダイなどの第2ダイに連結された第1ダイを含む集積回路において、複数の貫通シリコンビアTSVが第2ダイを貫通するよう設けられ、第1ダイに電力リファレンスを供給する。複数の貫通シリコンビアは、第2ダイの複数の回路セクションMSを妨害することなく横方向に再配置可能である。

(もっと読む)

半導体集積回路

【課題】チップ面積を有効に使用することができる半導体集積回路を構成する。

【解決手段】半導体基板(2)の縁に沿って構成される複数のボンディングパッド(5)(6)(7)と、複数のボンディングパッド(5)(6)(7)の下に、縁に沿って配置される複数のI/Oセル(3)と、複数の上層配線(13)を有する上層配線メッシュ(24)と、半導体基板(2)に構成されるコア領域(4)とを具備する半導体集積回路(1)を構成する。ここにおいて、コア領域(4)の面積は、半導体基板の表面に平行な面において、上層配線メッシュ(24)が占める面積よりも広い。

(もっと読む)

半導体チップ、半導体チップ群および半導体装置

【課題】 集積回路の周囲の回路及び配線の構造を簡素化可能で、チップ本体の小型化が可能なチップを提供する。

【解決手段】 半導体チップ1は平面形状が略四角形の板状のチップ本体3と、チップ本体3の表面に設けられた複数の集積回路5a、5bと、チップ本体3の裏面に設けられた他の回路としての配線13a〜13fと、集積回路5a、5bと配線13a〜13fを接続する接続手段としてのコンタクト11a、11bを有している。

コンタクト11a、11bはチップ本体3を貫通して設けられた導電性物質である。

このように、集積回路5a、5bを互いに接続するための配線を、チップ本体3の裏面2bに設けることにより、配線を表面2aに設けた場合と比べて、集積回路の周囲の他の回路(配線)の構造を簡素化することができる。

即ち、半導体チップ1を従来よりも小型化することができる。

(もっと読む)

半導体装置

【課題】細幅配線間のTDDB寿命の低下、および細幅配線間のショートによる歩留まり低下を抑制する半導体装置を提供する。

【解決手段】半導体装置10は、ダマシン配線からなる配線層を有し、0.5μm以上の幅を有する第1の配線12と、前記第1の配線12に隣接し前記第1の配線12から0.5μm未満の間隔で配置された第2の配線14と、前記第2の配線14に隣接し前記第1の配線12から0.5μm以下の間隔で配置された第3の配線16と、を備え、前記第2および第3の配線は同電位を有するよう構成されている。

(もっと読む)

半導体装置の製造方法

【課題】従来の半導体装置の製造方法には、さらなる効率化が困難であるという課題がある。

【解決手段】第1基板41に設けられた第1半導体層51の表示面側に、平面視で第1半導体層51の一部に重なる第1導電パターン107を形成する工程と、第1導電パターンをマスクとして第1半導体層51に不純物を注入する第1注入工程と、前記第1注入工程の後に、第1導電パターン107の一部を除去して、第1導電パターン107と第1半導体層51とが平面視で重なる領域である第1重畳領域113aを縮小する縮小工程と、前記縮小工程の後に、ゲート電極部57をマスクとして第1半導体層51に前記不純物を注入する第2注入工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

集積回路のシールリング構造

【課題】

デジタル回路によるデジタル雑音結合を低減できる、改良されたIC(集積回路)チップのシールリング構造を提供する。

【解決手段】IC用のシールリング構造は、ICの周辺に沿って設けられ、少なくとも第一部分と、アナログ及び/またはRF(無線周波数)回路ブロックに対向して同アナログ及び/またはRF回路ブロックを雑音から遮蔽するように設けられる第二部分に分けられたシールリングと、第二部分の下に位置し、P型基板の中に設けられるP+領域と、P+領域を囲み、第二部分の導電壁の下で横方向に延びるSTI(シャロートレンチアイソレーション)構造とを含む。

(もっと読む)

半導体装置

【課題】半導体装置の小型化を推進することができるとともに、配線間のカップリングを低減することができる技術を提供する。

【解決手段】半導体チップの短辺を縮小するために、半導体チップCHPのLCD制御部6にも最上層配線である配線L5を形成する。すなわち、半導体チップCHPの長辺方向に沿って延在するように配線L5を形成する。そして、配線L5の一層下層に形成される配線L4の延在方向を工夫する。具体的には、LCD制御部6を除く他の機能ブロックでは、配線L4を半導体チップCHPの長辺方向に沿って延在するように配置する。一方、LCD制御部6では、配線L4を半導体チップCHPの短辺方向に沿って延在するように配置する。

(もっと読む)

半導体集積回路装置

【課題】高電位電源配線と低電位電源配線との間の電位差の平面分布を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】高電位電源に接続されるパッド11と、上位の配線層に配置され、パッド11と接続され、幅の広いL字形を組み合わせた十字形を有する幹配線13と、幹配線13と同じ配線層に配置され、幹配線13より狭い幅を有し、幹配線13と接続され、幹配線13を2辺として形成する矩形に含まれる領域にそれぞれ分布する枝配線15と、低電位電源に接続されるパッド21と、下位の配線層に配置され、パッド21と接続され、幅の広いL字形を有し、投影面上で幹配線13に対向する位置に配置された幹配線23と、幹配線23と同じ配線層に配置され、幹配線23より狭い幅を有し、幹配線23と接続され、幹配線23を2辺として形成する矩形に含まれる内側の領域にそれぞれ分布する枝配線25とを備える。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】所定の配線層に形成されたCMP用のダミーパターンを有効に活用して、電源強化等の機能を有する半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板上部の配線層M2に形成されたダミーパターン24と、配線層M2と積層方向で対向する配線層M3に形成され所定の固定電位(電源電圧/グランド)が供給される固定電位用配線30、31、32と、ダミーパターン24と固定電位用配線30、31、32とを電気的に接続するビア40とを備えて構成される。

(もっと読む)

半導体集積回路装置およびその設計方法、半導体集積回路装置の製造方法

【課題】基板上に形成される、ワード線長およびビット線長が異なるSRAMの動作速度を、簡単な構成により最適化する半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、基板上の第1の領域に形成された第1のSRAM20Aと、基板上の第2の領域に形成された第2のSRAM20Bと、を備え、第1のSRAM20Aでは、ワード線WLの方がビット線BLよりも長く、第2のSRAM20Bでは、ビット線BLの方がワード線WLよりも長く、第1のSRAM20Aでは、ワード線WLが、ビット線BLを構成する配線層よりも下の配線層に形成され、第2のSRAM20Bでは、ビット線BLが、ワード線WLを構成する配線層よりも下の配線層に形成される。

(もっと読む)

半導体集積回路

【課題】トランジスタが励起する電磁波を有効利用することによって、電源ノイズを発生させず高い性能を有する半導体集積回路を提供する。

【解決手段】 オンチップインバータは孤立電磁波を励起すると見なすと考える孤立電磁波コンセプトにより、半導体集積回路内の金属配線を設計し解析する。設計や解析には孤立電磁波のアナライジングモデル又は、オンチップインバータのゲート遅延時間に円周率を掛けた値の逆数として求められる周波を有する一つの正弦波を有する単一正弦波を92%以上の確かさで使用する。孤立電磁波コンセプトを適用すると半導体集積回路内のオンチップ電源分配回路を電磁波理論に基づいてほぼ理想的に設計することが出来る。本発明において、オンチップ電源分配回路は低インピーダンス損失線路を使用して構成される。低インピーダンス損失線路は陽極導体、陰極導体、および損失を有する絶縁膜で構成される。

(もっと読む)

121 - 140 / 325

[ Back to top ]