Fターム[5F033VV05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 接地線 (304)

Fターム[5F033VV05]に分類される特許

141 - 160 / 304

半導体集積回路装置およびその設計方法、半導体集積回路装置の製造方法

【課題】基板上に形成される、ワード線長およびビット線長が異なるSRAMの動作速度を、簡単な構成により最適化する半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、基板上の第1の領域に形成された第1のSRAM20Aと、基板上の第2の領域に形成された第2のSRAM20Bと、を備え、第1のSRAM20Aでは、ワード線WLの方がビット線BLよりも長く、第2のSRAM20Bでは、ビット線BLの方がワード線WLよりも長く、第1のSRAM20Aでは、ワード線WLが、ビット線BLを構成する配線層よりも下の配線層に形成され、第2のSRAM20Bでは、ビット線BLが、ワード線WLを構成する配線層よりも下の配線層に形成される。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】所定の配線層に形成されたCMP用のダミーパターンを有効に活用して、電源強化等の機能を有する半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板上部の配線層M2に形成されたダミーパターン24と、配線層M2と積層方向で対向する配線層M3に形成され所定の固定電位(電源電圧/グランド)が供給される固定電位用配線30、31、32と、ダミーパターン24と固定電位用配線30、31、32とを電気的に接続するビア40とを備えて構成される。

(もっと読む)

集積回路装置、多出力駆動IC及びそれを用いた電子機器

【課題】 バンプの形状を改良することで回路レイアウトの自由度を拡大できる集積回路装置、多出力駆動IC及び電子機器を提供すること。

【解決手段】 第1の方向Xに沿って第1の距離A1を隔てて配列された複数のバンプ1,2と、複数のバンプ1,2にそれぞれ接続される複数の配線層5と有する集積回路装置である。この集積回路装置では、複数のバンプ1,2の各々は、第1の方向Xと該第1の方向と直交する第2の方向Yの各隣接間で第1の距離A1よりも短い第2の距離A2を隔てて分割された複数のサブバンプ3を含み、複数のサブバンプ3は、下層の配線層5により共通接続されている。

(もっと読む)

半導体装置

【課題】複数の電源電圧を使用する半導体装置において、安定的な電源電圧の供給、および設計の自由度を確保しつつ、回路面積の増大を抑制する。

【解決手段】第3固定電位線が平行に複数配線されている。第3固定電位線と直交する方向に、第1固定電位線および第2固定電位線を含む高電位側固定電位線群が、所定間隔で複数配線されている。隣接する一対の第3固定電位線と、隣接する一対の高電位側固定電位線群とで囲まれ、第1素子または第2素子が配置される配置領域において、一対の第3固定電位線間に、第1固定電位線または第2固定電位線のいずれかが配線されている。第2素子用の配置領域では、その配置領域を形成する一対の第3固定電位線間に、その配置領域を形成する一対の高電位側固定電位線群にそれぞれ含まれる、一対の第2固定電位線間が結ばれて第2固定電位線が配線されている。

(もっと読む)

クロストーク防止回路

【課題】 微細化、集積度向上に影響を与えない方法で、クロストークを減少または除去する回路を提供する。

【解決手段】 クロストーク防止回路は、ほぼ平行して形成されている少なくとも2本の信号線、たとえば、マスタスロック用線とスレーブクロック用線l1,l2の間に、これら2本の信号線の少なくとも一方に印加される信号が存在しないとき、たとえば、テスト用信号が印加され、前記2本の信号線に信号が印加されるとき接地状態になる第3の信号線l3を生成する。好ましくは、第3の信号線にドライバ回路を接続し、該ドライバ回路の出力トランジスタのNチャネルトランジスタとPチャネルトランジスタの電流駆動能力の比率をほぼ2:1にする。

(もっと読む)

不具合検出機能を備えた半導体装置

【課題】層間絶縁膜の剥離を検出する半導体装置を提供する。

【解決手段】半導体チップ2の外周に沿って層間絶縁膜の剥離を検出するための信号を伝送する検査配線3が形成されている。検査配線3に検出信号を供給するための検出回路4と、検査配線3を流れた検出信号を出力するための出力端子5と、半導体チップ2に設けられた内部回路6と、内部回路6からの出力信号と、検査配線3を流れた検出信号とのいずれか一方を選択して出力端子5に供給する出力切替回路7を備える。検査配線3は適当な間隔毎に切断され、層間配線10を通して最上層配線8に載せ替えて接続されている。以上の構成により、測定端子数を増やすことなく層間絶縁膜の剥離を容易に検出することが可能となり、さらに層間絶縁膜の接着を補強することができる。

(もっと読む)

半導体装置

【課題】信号配線を高密度に配置しつつ、ノイズの影響を確実に抑えるシールド構造を小さい面積で実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置10は、拡散層12が形成される半導体基板11の上部に少なくとも2層の配線層M2、M3が積層され、所定電位を保持する信号を伝送するために2層の配線層M2、M3に形成された信号配線20、30と、信号配線20,30を遮蔽するために一定の電位に固定され2層の配線層M2、M3に信号配線20、30と隣接して形成されたシールド配線21、31と、半導体基板11の上部に絶縁膜を挟んで形成されるゲート電極13とを備え、下層の配線層M2に形成された信号配線20が、積層方向に対向するゲート電極13と電気的に接続されている。

(もっと読む)

不揮発性半導体メモリ

【課題】信頼性の高い不揮発性半導体メモリを提供できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、複数のメモリセルが配置されるメモリセルアレイ領域100と、メモリセルアレイ領域100の周囲を取り囲む周辺回路領域と、周辺回路領域とメモリセルアレイ領域100との境界部分であるセルアレイ隣接領域105と、メモリセルアレイ領域100内に層間絶縁膜を介して設けられる複数の第1導電線SLと、セルアレイ隣接領域105内に層間絶縁膜を介して設けられる複数の第2導電線M2とを具備し、複数の第2導電線M2はその配線内にスリット50が形成されていることを備える。

(もっと読む)

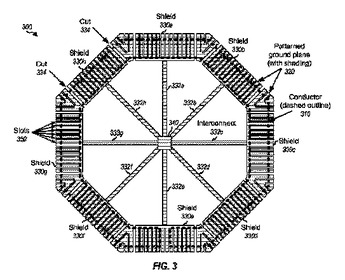

パターン化された接地平面を有するインダクタ

パターン化された接地平面を有するインダクタが、説明される。一設計においては、インダクタは、第1の層上に形成された導体と、その導体の下の第2の層上に形成されたパターン化された接地平面と、を含む。パターン化された接地平面は、オープンな中心エリアと、導体の形状に整合した形状と、を有する。パターン化された接地平面は、複数のシールド、例えば、八角形の形状の導体の8つの辺についての8つのシールド、を含んでいる。各シールドは、導体に垂直に形成された複数のスロットを有する。パターン化された接地平面を別個のシールドへと分割することと、各シールド上にスロットを形成することとは、パターン化された接地平面上の渦電流の流れを防止するのに役立ち、これは、インダクタのQを改善することができる。複数の相互接続は、複数のシールドを回路接地へと結合し、この回路接地は、導体の中心に位置することができる。  (もっと読む)

(もっと読む)

クロック配線構造、半導体装置、及び半導体装置の製造方法

【課題】配線形状のばらつきを効果的に抑制することのできる配線構造、半導体装置、及び半導体装置の製造方法を提供すること

【解決手段】本発明にかかる配線構造は、クロック配線11と、クロック配線11と同層において、クロック配線11に沿ってその両側に設けられた一対の第1シールド配線12と、クロック配線11と絶縁層を介した異なる層において、クロック配線11及び一対の第1シールド配線12の対向する領域を覆うように設けられた第2シールド配線13と、一対の電極(上部電極17、下部電極18)が絶縁層を介して対向配置されたMIM容量30と、を備え、MIM容量30の一対の電極のうち少なくとも一方が、第2シールド配線13と同層に設けられているものである。

(もっと読む)

半導体装置

【課題】従来の半導体装置に比べてさらなる小型化を可能とする、複数の半導体素子が並列に接続された半導体装置を提供する。

【解決手段】半導体装置1は、ソース領域15と、ドレイン領域17と、ゲート領域16とを有するJFET10を複数個備えている。複数個のJFET10は、ソース領域15同士を接続するソース電極25と、ドレイン領域17同士を接続するドレイン電極27と、ゲート領域16同士を接続するゲート電極26とにより並列に接続されている。ソース電極25は、ソース電極25を外部と接続するソース電極パッド25Aを含んでいる。ドレイン電極27は、ドレイン電極27を外部と接続するドレイン電極パッド27Aを含んでいる。そして、ソース電極パッド25Aおよびドレイン電極パッド27Aは、絶縁体からなる絶縁保護膜28を挟んでゲート電極26の上側に突出するように形成されている。

(もっと読む)

半導体チップ及び半導体装置

【課題】半導体基板の裏面側から効率よく放熱する半導体チップを実現できるようにする。

【解決手段】半導体チップ10は、基板11と、基板11の素子形成面側に形成され、複数の半導体素子を含む集積回路12と、基板11における複数の半導体素子のうちの所定の半導体素子30と対応する領域に形成さた放熱プラグ31とを備えている。放熱プラグ31は、素子形成面と反対側の面に開口する非貫通孔に埋め込まれた基板11と比べて熱伝導率が大きい材料からなる。

(もっと読む)

半導体基板接続ビア

第1導電層(104)とシリケートガラス層(106)の縁部を互いに隣接させて、半導体基板(41)まで延在するビア(164)に沿って延在させる。導電体(114/116)は、ビア(164)を通り延在して、半導体基板(41)と接触する。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】ワイヤボンディングで実装されるチップとバンプ電極で実装されるチップとで、製造工程を共通化できる技術を提供する。

【解決手段】バンプ電極によりチップ1が外部との電気的接続を行う場合においても、ボンディングワイヤによりチップ1が外部との電気的接続を行う場合においても、1本の最上層の配線7にバンプ接続部15およびボンディングパッド16の両方を設ける。バンプ電極を用いる場合にはバンプ接続部15上の絶縁膜に開口部を設け、ボンディングパッド16上は絶縁膜で覆う。一方、ボンディングワイヤを用いる場合にはボンディングパッド16上の絶縁膜に開口部を設け、バンプ接続部15上は絶縁膜で覆う。

(もっと読む)

半導体装置

【課題】静電保護素子のクランプ能力を十分に発揮し、内部回路を静電気によるサージから保護することができる半導体装置を提供することを目的とする。

【解決手段】半導体基板上に、内部回路と、前記内部回路と接続配線及び接地配線により接続される接続パッド及び接地パッドと、前記接続パッドと前記接地パッドとの間に接続される静電保護素子とが設けられ、前記半導体基板と前記接地配線とが、前記接地配線に所定の密度で形成されたコンタクトにより電気的に接続されている半導体装置であって、前記所定の密度は、前記接続パッドから前記静電保護素子を経由して前記接地パッドに至る部分のインピーダンスが、前記接続パッドから前記内部回路を経由して前記接地パッドに至る部分のインピーダンスよりも低くなるように設定されていることを特徴とする。

(もっと読む)

集積回路装置のレイアウト方法、集積回路装置のレイアウトプログラム、集積回路装置のレイアウトシステム、集積回路装置及び電子機器

【課題】チップ面積の増加を伴わずに電源補強を実現することができる集積回路装置のレイアウト方法等を提供すること。

【解決手段】本発明の集積回路装置のレイアウト方法は、機能セルが配置されていない未配置領域を探索するステップ(ステップS12)と、未配置領域に、少なくとも一部が第1、第2のポリシリコン配線パターンによりそれぞれ形成された第1、第2の電源補強線を含む第1、第2の電源補強セルを配置するステップ(ステップS14)と、を含む。ステップS14において、第1、第2のポリシリコン配線パターンを第2、第1の電源供給線とそれぞれ交差させて、第2の方向に沿って、第1、第2の電源補強線を介してそれぞれ2つの第1の電源供給線及び2つの第2の電源供給線を接続する2つの配線パターンの少なくとも一方が形成されるように、少なくとも2つの第1、第2の電源補強セルの少なくとも一方を第2の方向に沿って並べて配置する。

(もっと読む)

集積回路装置のレイアウト方法、集積回路装置のレイアウトプログラム、集積回路装置のレイアウトシステム、集積回路装置及び電子機器

【課題】チップ面積の増加を伴わずに電源補強を実現することができる集積回路装置のレイアウト方法等を提供すること。

【解決手段】本発明の集積回路装置のレイアウト方法は、機能セルが配置されていない未配置領域を探索するステップ(ステップS14)と、未配置領域に、少なくとも一部が第1及び第2のポリシリコン配線パターンによりそれぞれ形成された第1及び第2の電源補強線と、を含む電源補強セルを配置するステップ(ステップS16)と、を含む。ステップS16において、第1及び第2のポリシリコン配線パターンを第2の電源供給線及び第1の電源供給線とそれぞれ交差させて、第2の方向に沿って、第1の電源補強線及び第2の電源補強線を介してそれぞれ2つの第1の電源供給線及び2つの第2の電源供給線を接続する2つの配線パターンの少なくとも一方が形成されるように、少なくとも2つの電源補強セルを第2の方向に沿って並べて配置する。

(もっと読む)

半導体チップ

【課題】周辺部に外部接続用パッドが3列以上千鳥状配置された半導体チップにおいて、チップ面積を抑えつつ、電源またはグランドを安定供給する。

【解決手段】最外列に配置された外部接続用パッド11が、内部コア回路の電源用またはグランド用パッドとして用いられている。この外部接続用パッド11には、外側から2列目に配置された外部接続用パッド12がパッド用メタルと同層のメタル15で接続されている。内部コア回路への電源供給配線の抵抗は、パッド11からの抵抗R2とパッド12からの抵抗(R3’+R3”)との並列抵抗となり、その値は抵抗R2に比べて格段に小さくなる。これにより、内部コア回路の電源のIRドロップに起因する回路の誤動作を防止することができる。しかも、必要となるI/Oセル9a,9bは2個のみである。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は受動素子を備えた半導体装置及びその製造方法に関し、装置の小型化を図りつつ、かつ誘電損失の発生を抑制することを課題とする。

【解決手段】半導体チップ11と、半導体チップ11を貫通して形成された15,16とを有した半導体装置であって、半導体チップ11の第1面35A(主面)に対する反対側の第2面35Bに、貫通電極15と接続したグランド層28と、貫通電極16に接続したパッチアンテナ33とをSiO2又はSiNよりなる無機絶縁層30を介して積層した構成とする。

(もっと読む)

半導体装置

【課題】配線に係る抵抗を低減することができるため、半導体セルの面積を縮小することができる。

【解決手段】本発明に係る半導体装置は、半導体基板1と、半導体基板1表面に形成されたコンタクト領域4と、半導体基板1上に形成された層間絶縁膜21とを備える。層間絶縁膜21には、コンタクト領域4まで達する線状に延設された開口溝が設けられる。そして、開口溝内に埋設され、コンタクト領域4と電気接続された導電層8をさらに備える。

(もっと読む)

141 - 160 / 304

[ Back to top ]