Fターム[5F033VV05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 接地線 (304)

Fターム[5F033VV05]に分類される特許

61 - 80 / 304

半導体チップ及びそれを搭載した半導体モジュール

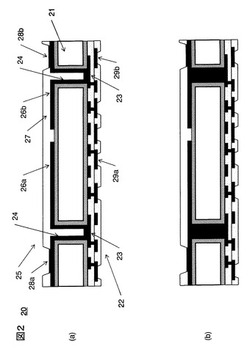

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

半導体装置

【課題】MEMSキャパシタとその制御用集積回路を反りの抑えられた1枚の基板上に有する半導体装置を提供する。

【解決手段】貫通孔を含む貫通孔領域を有する基板と、前記基板の上方のMEMSキャパシタと、前記MEMSキャパシタの下方の前記MEMSキャパシタの制御用集積回路とを有する半導体装置を提供する。前記制御用集積回路は、前記基板上のトランジスタを含む。前記MEMSキャパシタの真下の前記基板上の領域と前記貫通孔領域とは、少なくとも一部において重なる。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増加を抑制しつつ、ウェハ状態でのスクリーニング時に電源電圧低下(IRドロップ)を抑えることができる半導体装置を提供する。

【解決手段】本発明の一形態に係る半導体装置50は、半導体チップ100と、半導体チップ100上面の中央部のチップ中央領域120に形成された複数の外部接続用パッド102及び複数の検査用パッド104と、複数の外部接続用パッド102上に形成されたバンプ105とを備える。

(もっと読む)

半導体装置の配線構造及びそれを備えた半導体装置

【課題】信号配線が電源配線と長距離に亘って並走することを回避して、信号配線の寄生容量を低減してノイズの影響を低減する半導体装置の配線構造及びそれを備えた半導体装置を提供すること。

【解決手段】第1方向X1に延びる複数の第1配線1Vから構成される第1配線層110と、第1配線層110の上に配設され、第1方向X1に交差する第2方向X2に延びる複数の第2配線2Vから構成される第2配線層120とを備え、第1配線層110および第2配線層120は、第1方向X1および第2方向X2により規定される平面内に設定された配線領域R内に配設され、第1配線1Vは、配線領域Rの第1方向X1における一端から他端までの全長よりも短い長さでそれぞれ形成され、第2配線2Vは、配線領域Rの第2方向X2における一端から他端までの全長よりも短い長さでそれぞれ形成されている半導体装置100の配線構造。

(もっと読む)

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体装置

【課題】機能修正を行う場合でも速やかに製造することができるとともに、仕掛品の廃棄量を削減することが可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、レビジョン信号発信回路が形成されたベース層と、前記ベース層上に積層された3層以上の配線層と、最上位の配線層に形成された電源配線あるいはグランド配線と、前記レビジョン制御回路を前記最上位の配線層の電源配線あるいはグランド配線にのみ接続するレビジョン信号線と、を備えている。

(もっと読む)

半導体集積回路装置

【課題】回路ブロックの面積を増大しないで容量セルを構成すること。

【解決手段】一対の拡散領域15、14を有する基板構造層10と、一対の電源配線41、42を有する配線層40と、第1電極21、誘電体22、第2電極23が積層するとともに、基板構造層10と配線層40との間にて、スタンダードセルが配置されるスタンダードセル領域1の外枠に沿って枠状に形成される容量20と、スタンダードセル領域1外において一方の電源配線41と一方の拡散領域15とを電気的に接続する第1基板コンタクト31と、スタンダードセル領域1外において他方の電源配線42と他方の拡散領域14とを電気的に接続する第2基板コンタクト32と、スタンダードセル領域1内において第1電極21と他方の拡散領域14とを電気的に接続する第1容量コンタクト34と、スタンダードセル領域1内において第2電極23と一方の電源配線41とを電気的に接続する第2容量コンタクト33と、を備える。

(もっと読む)

ドライバー集積回路チップの電源連結構造

【課題】本発明は、ドライバー集積回路チップの電源連結構造に関し、より詳細には、ドライバー集積回路チップ内部のルーティングパターンをLOGと並列で配置して、チップの両端に配置された電源を連結することで配線を簡素化してライン抵抗を減少させることができるドライバー集積回路チップの電源連結構造を提供する。

【解決手段】本発明によるドライバー集積回路チップの電源連結構造によると、ドライバー集積回路チップの入出力端子の配線数を減少させて配線を簡素化して、これによりチップサイズを減らして及び製造費用を減少させることができる効果があり、チップ内部のルーティングパターンとLOGを並列で連結することでライン抵抗が減少されて、信号の遅延を減らすことができる長所がある。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】下層の配線層にMTJ素子を形成しつつ、MTJ素子に熱が加わることを抑制する。

【解決手段】基板10上に絶縁層220を形成する。次いで絶縁層220上にMTJ素子100を形成する。次いで、MTJ素子100上に配線242を形成する。次いで配線242上に絶縁層250を形成する。次いで絶縁層250の表層に配線252を形成する。そして配線252を光照射により熱処理する。そして配線252を形成する工程において遮蔽導体254を形成する。

(もっと読む)

半導体装置

【課題】電源電圧の電圧降下を抑制しつつ、信号配線リソースを大きく確保可能な電源配線構造を実現する。

【解決手段】第1配線層に、電源電位配線101a〜101dおよび基板電位配線102a〜102dが形成されており、配線層全体の真ん中より下層側の配線層に、電源ストラップ配線103a,103b,104a,104bが形成されている。上方ビア部114は、下方ビア部112よりも、電源ストラップ配線103a,103b,104a,104bが延びる方向における配置密度が低くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

伝送線のためのシールド構造体

シールド構造体は、集積回路上の第1金属化層に形成された櫛状構造体が複数の歯を備え櫛状構造体の歯は他方の櫛状構造体に向かって延びる第1、第2櫛状構造体と、第1櫛状構造体から上方に延びる複数の第1導電性ビアと、第2櫛状構造体から上方に延びる複数の第2導電性ビアと、第1金属化層の上方の第2金属化層に配置された第1、第2平面構造体と、第1平面構造体から複数の第1導電性ビアに向かって下方に延びる複数の第3導電性ビアと、第2平面構造体から複数の第2導電性ビアに向かって下方に延びる複数の第4導電性ビアとを備え、第1、第2櫛状構造体、第1、第2平面構造体及び第1〜第4導電性ビアは全て同電位であり接地されることが好ましい。ある実施形態では1つ以上の信号線が第1、第2平面構造体間の第2金属化層に配置され、他の実施形態では1つ以上の信号線が第1、第2平面構造体間の第3金属化層に配置される。 (もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

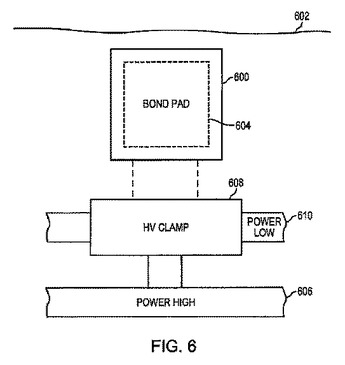

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

電子基板に組み込まれたビア構造

基板に配置されたビア構造のシステム。当該システムは、基板に配置された外側導電層と、内側絶縁層と、内側導電層とを備える第1ビア構造を有する。外側導電層は内側絶縁層と基板とを分離し、内側絶縁層は内側導電層と外側導電層とを分離する。第1相補的対の第1信号が内側導電層を通過し、第1相補的対の第2信号が外側導電層を通過する。別の実施形態では、電子基板にビア構造を形成する方法が提供される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 セルサイズが小さく、かつ配線接続の自由度が向上できるスタンダードセルを用いた半導体装置を提供する。

【解決手段】 半導体装置はメモリ回路と周辺回路を備え、周辺回路を分割した回路ブロックのそれぞれを、同じ高さを有した矩形で、それぞれが基本論理回路として機能するように構成された複数のスタンダードセルを、同じ高さになるように配置したセルブロックとして構成し、スタンダードセルへの入力信号配線が、メモリセルトランジスタと容量下部電極を接続する容量コンタクトパッド配線を用いて配線される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パッケージ端部の樹脂層の一部が剥離し、耐湿性が悪化するという問題があった。

【解決手段】本発明の半導体装置では、シリコン基板2の一主面側に再配線層5、5Aと剥離防止層6が配置され、それらを被覆するように樹脂層3が形成される。剥離防止層6は、再配線層5、5Aの無配置領域であり、半導体装置1の外周端部近傍に配置されることで、樹脂層3の樹脂量が低減される。この構造により、樹脂層3の熱収縮力に起因する樹脂の反り上がりが防止し、樹脂層3が、シリコン基板2上から剥離することが防止され、半導体装置1の耐湿性が向上される。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

半導体装置

【課題】電源配線やグランド配線に流れる電流の周波数が上がってもインピーダンスが上がるのを抑えられる半導体装置を提供すること。

【解決手段】トランジスタ20、21の近傍に配線された電源配線11a及びグランド配線11cを備え、電源配線11a及びグランド配線11cは、それぞれ、分割した構造となっており、所定間隔をおいて一方向に配線された複数本の分割配線11a、11cよりなる。

(もっと読む)

61 - 80 / 304

[ Back to top ]