Fターム[5F033VV05]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 接地線 (304)

Fターム[5F033VV05]に分類される特許

21 - 40 / 304

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】大電流を流す第1ビアおよび第1配線を有し、且つ、当該第1ビアおよび第1配線が形成された第1面が平坦な半導体装置を提供する。

【解決手段】第1基板100と、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420と、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続する第1配線440と、を備えている。また、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

(もっと読む)

半導体チップ及びその製造方法、並びに半導体パッケージ

【課題】再配線形成前のウエハテストを適切に実施する。

【解決手段】半導体チップ1は、周辺電極パッド30内又はV/G配線20において周辺電極パッド30に相対的に近い位置にある第1の再配線接続部61と、V/G配線20において周辺電極パッド30から相対的に遠い位置にあり、再配線60の形成前における電位が第1の再配線接続部61よりも小さい第2の再配線接続部62とが、再配線60により接続されたものである。半導体チップ1は、第2の再配線接続部62、V/G配線20上の第2の再配線接続部62の近傍で再配線60の形成前における電位が第1の再配線接続部61よりも小さい部分、又は、V/G配線20から第2の再配線接続部62の近傍に引き出され、再配線60の形成前における電位が第1の再配線接続部61よりも小さい導電部に、ウエハテスト用の検査部80を備えている。

(もっと読む)

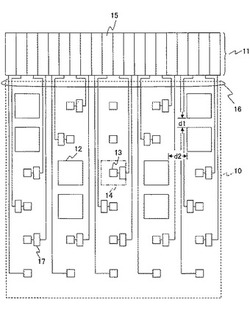

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】情報が読み取られることを防止する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置10は、コンタクト15aを有する第2絶縁層15と、コンタクト17aを有する第3絶縁層17と、第2絶縁層15と第3絶縁層17との間に配置された第2配線層16と、を備え、コンタクト15aとコンタクト17aとの間の第2配線層16の部分には配線が配置されておらず、コンタクト15aとコンタクト17aとの間の距離は、コンタクト15a又はコンタクト17aと、第2絶縁層15及び第3絶縁層17及び第2配線層16内の他のコンタクト又は配線との間の距離よりも短い。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

半導体装置

【課題】半導体部材同士が強固に接合された半導体装置、電子機器、及び、半導体装置の製造方法を提供することを目的とする。

【解決手段】第2配線層9に接合させる第1配線層2を、第1層間絶縁膜3と、第1層間絶縁膜3内に埋め込まれ、一方の表面が第1層間絶縁膜3の表面と同一面上に位置した第1電極パッド4と、一方の表面が第1層間絶縁膜3の表面と同一面上に位置し、第1電極パッド4の周囲に配設された第1ダミー電極5と、によって構成する。また、第2配線層9は、第1層間絶縁膜3の第1電極パッド4の表面側に位置した第2層間絶縁膜6と、一方の表面が第2層間絶縁膜6の第1層間絶縁膜3側の表面と同一表面上に位置し、かつ第1電極パッド4に接合された第2電極パッド7と、一方の表面が第2層間絶縁膜6の第1層間絶縁膜側3の表面と同一面上に位置し、第2電極パッド7の周囲に配設され、第1ダミー電極5に接合された第2ダミー電極8と、により構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高周波配線を含む半導体装置において、エロージョンやディッシングを効果的に防いで半導体装置を安定的に製造するとともに、高周波配線への周囲のダミーメタルからの影響を低減して特性を向上させる。

【解決手段】半導体装置100は、半導体基板上の多層配線層中に設けられた高周波配線102と、多層配線層中の半導体基板と高周波配線102が設けられた層との間の第2の配線層122bに設けられたダミーメタル104とを含む。ダミーメタル104は、平面視で、高周波配線102の外縁で囲まれる第1の領域106とその周囲の第2の領域108とを含む高周波配線近傍領域110と、それ以外の外部領域112とにそれぞれ分散配置され、高周波配線近傍領域110のダミーメタル104間の平均間隔が、外部領域112のダミーメタル104間の平均間隔よりも広い。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、半導体装置のレイアウト方法

【課題】新たな要因に起因したクラックの発生を抑制すること。

【解決手段】第1のAl配線31と絶縁膜33とを含む第1のAl配線層30と、第2のAl配線41と絶縁膜43とを含む第2のAl配線層40と、複数の第3のAl配線51と絶縁膜52とを含む第3のAl配線層50と、第1のAl配線31と第2のAl配線41とを接続する第1のビア32と、第2のAl配線41と第3のAl配線51とを接続する第2のビア42とを有し、少なくとも一部の第3のAl配線51は隣り合う第3のAl配線51同士の間隔Bが2.25μm以下である隙間60を形成しており、平面視で隙間60の中の少なくとも一部は第1のAl配線31及び第2のAl配線41と重ならない領域を有し、隙間60を形成するように対峙した第3のAl配線51の対峙方向の配線幅Cは15μmより大きく、第2のビア42同士の間隔Fは第2のビア42の径Gの3倍以上である半導体装置。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体集積回路

【課題】製造コストを増大させずに、半導体集積回路の電源配線、接地配線の電圧降下を減少させる。

【解決手段】半導体チップ1上の第1の方向に延びる電源配線12Aが配置され、半導体チップ1上の第2の方向に延びると共に、第2の方向から第1の方向に屈曲し、電源配線12Aの一部と重畳する屈曲部24Aを有する電源引き出し配線22Aが配置されている。また、第1の方向に延びる接地配線12Bが配置され、第2の方向に延びると共に、第2の方向から、第1の方向とは逆方向の第3の方向に屈曲し、接地配線12Bの一部と重畳する屈曲部24Bを有する接地引き出し配線22Bが配置されている。電源引き出し配線22Aと接地引き出し配線22Bを覆う第1の層間絶縁膜13の中には、電源配線12Aと屈曲部24Aを接続する電源配線ビアコンタクト14Aと、接地配線12Bと屈曲部24Bを接続する接地配線ビアコンタクト14Bが配置されている。

(もっと読む)

半導体装置

【課題】規格により規定された速度による信号の転送を実現し、半導体装置やそれを内蔵した電子機器の誤動作を防止する。

【解決手段】第1の半導体素子101の導体配線層106に、パッケージ基板100の信号端子103と第2の半導体素子102の信号端子117とを接続する信号線導体113aと、パッケージ基板100の電源端子104と第2の半導体素子102の電源端子118とを接続する電源導体114とを、信号線導体113aが導体配線層106において、信号線導体113aとの間に水平方向に一定の間隔をあけて隣接する電源導体114に挟まれるように形成する。

(もっと読む)

21 - 40 / 304

[ Back to top ]