Fターム[5F033VV13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | マイクロマシン (48)

Fターム[5F033VV13]に分類される特許

1 - 20 / 48

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

バッチ製作された3D相互接続

【課題】ウェハ貫通ビア(TWV)を使用した相互接続において、ダイ区域の消費を低減し、ダイ区域を利用可能とする、バッチ製作された3D相互接続を提供する。

【解決手段】1つまたは複数の垂直相互接続を製作する。ウェハ積層体を形成するために複数のウェハをパターニングおよび積層するステップを含む。ウェハ積層体の1つまたは複数の切断刃の通り道内でウェハ積層体に複数の開口を形成し、導電性材料を複数の開口の側壁に堆積させる。ウェハ積層体は、側壁の導電性材料が、結果として得られる積層ダイの縁部部分に露出されるように、1つまたは複数の切断刃の通り道に沿い、複数の開口を通ってダイシングする。

(もっと読む)

半導体装置

【課題】プロセス数を増大させることなく、応力を緩和できる構造を有する半導体装置を提供する。

【解決手段】一方の面に埋め込み酸化層と半導体層がこの順で積層される半導体基板10を加工して作製され、前記一方の面側で他の基板に接合される半導体装置であって、前記埋め込み酸化層及び前記半導体層を加工して形成される半導体素子20と、前記埋め込み酸化層及び前記半導体層を加工して形成され、前記半導体素子に接続される配線部と、前記配線部の端部に連続する前記半導体層によって構成され、当該半導体層の下側の埋め込み酸化層が除去されて前記半導体基板との間に空隙が形成されるパッド部40と、前記パッド部と前記他の基板を接合する接合部とを含む。

(もっと読む)

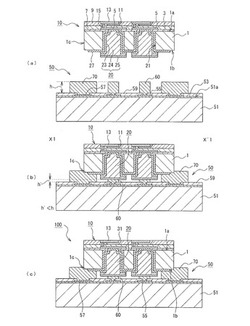

半導体装置およびその製造方法

【課題】センシング部を複数の基板で封止した半導体装置において、基板の平面方向に配線を設けたとしても、配線のレイアウトを簡略化することができる構造、およびその製造方法を提供する。

【解決手段】キャップ部300は、センサ部100に設けられた第1固定部と第2固定部とを電気的に接続したクロス配線部323を備え、クロス配線部323はキャップ部300の一面301に配置されたクロス配線322を備えている。また、キャップ部300は、キャップ部300を貫通し、一端がクロス配線322に電気的に接続され、他端がキャップ部300の他面302に配置された貫通電極344を備えている。これにより、貫通電極344を介してクロス配線322の電位、すなわち、センサ部100の第1固定部および第2固定部の電位をキャップ部300の他面302に取り出すことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法に係り、浮動構造体の支持基板への当接を他の当接を生じさせることなく実現させて、浮動構造体と支持基板との電気的接続を確保することにある。

【解決手段】半導体からなる支持基板と、支持基板上に設けられる絶縁層と、絶縁層上に設けられる活性層と、を備える半導体装置において、絶縁層の一部がエッチング除去されることにより活性層の一部に浮動構造体を形成し、その後、導電性部材を少なくとも浮動構造体を含む活性層に押し付けることで、その浮動構造体を支持基板に当接させて、浮動構造体と支持基板とを導通させる。

(もっと読む)

マスクおよびその製造方法、半導体ウエハ

【課題】半導体ウエハ面内における金属配線の抵抗分布のばらつきを抑え、得られるデバイスの特性や精度を面内で均一化させることが可能なマスクを提供する。

【解決手段】本発明のマスクは、金属配線を有するデバイス10を基板2の一面上に多数形成する際に、該基板の一面に対向配置されて用いられるマスクであって、個々の前記デバイスが配される前記基板上の位置に応じて、それぞれのデバイスが有する前記金属配線に対応する部位の形状を変えたこと、を特徴とする。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

半導体装置

【課題】MEMSキャパシタとその制御用集積回路を反りの抑えられた1枚の基板上に有する半導体装置を提供する。

【解決手段】貫通孔を含む貫通孔領域を有する基板と、前記基板の上方のMEMSキャパシタと、前記MEMSキャパシタの下方の前記MEMSキャパシタの制御用集積回路とを有する半導体装置を提供する。前記制御用集積回路は、前記基板上のトランジスタを含む。前記MEMSキャパシタの真下の前記基板上の領域と前記貫通孔領域とは、少なくとも一部において重なる。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

充填用基材及びそれを用いた充填方法

【課題】充填時の溶融温度が低く、凝固後は高い融点を確保することができ、しかも、作業操作性に優れた充填用基材及びそれを用いた充填方法を提供すること。

【解決手段】充填用基材5は、第1金属層21と第2金属層22とを含む金属層2を支持基体1の一面上に設けた構造になっている。第1金属層21は、その融点よりも低い温度で溶融可能なナノ金属粒子の集合したものでなり、第2金属層22は、その融点が第1金属層21の融点よりも低い金属粒子の集合したものでなる。充填用基材5の一面側を、微細空間30の開口する基板3の一面上に重ねる。そして、充填用基材5を加熱し、かつ、加圧F1して、金属層2の溶融物を微細空間30内に充填する。

(もっと読む)

半導体装置の製造方法

【課題】複数の顧客による各々異なるLSIが共同で作製された基板を、守秘性が得られた状態で各々の顧客に提供できるようにする。

【解決手段】特定の顧客への提供対象とするLSIチップ領域331以外の領域が開放した開口部307aを備えるマスクパターン307を形成する。次に、マスクパターン307をマスクとし、開口部307に露出しているLSIチップ領域332をエッチング除去し、ブラインド領域301aを形成する。ブラインド領域301aの形成では、第1配線層302,第2配線層303,および第3配線層304を除去し、これらの下層の一部までを除去する。

(もっと読む)

貫通孔配線基板の製造方法

【課題】めっき反応速度を調整することでめっき未着を防ぐことが可能な貫通孔配線基板の製造方法を提供することである。

【解決手段】微小デバイスを構成する貫通孔配線基板の製造方法であって、基板40の両表面を貫通する貫通孔41を形成する工程と、貫通孔41の少なくとも内表面にNiめっきを成長させる工程と、を備え、貫通孔41の少なくとも内表面にNiめっきを成長させる工程では、Niめっきの析出レートを50nm/min未満にしてめっきを成長させる。

(もっと読む)

1 - 20 / 48

[ Back to top ]