Fターム[5F033WW07]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | エネルギー (197)

Fターム[5F033WW07]に分類される特許

141 - 160 / 197

フラッシュメモリ素子の金属配線およびコンタクトプラグ形成方法

【課題】深さの異なるコンタクトプラグ形成方法において、コンタクトプラグの抵抗増加を防止し、半導体基板のエッチングされる量を最小にする方法を提供する。

【解決手段】相異なるエッチングターゲットt1,t2を有する、均一でない厚さの反射防止膜34およびゲートを露出させるコンタクトプラグが形成される領域と半導体基板を露出させるコンタクトプラグが形成される領域に、反射防止膜の厚さの不均一を利用した第1エッチング工程、エッチング停止膜26をエッチング停止膜として利用した第2エッチング工程、およびWSi18をエッチング停止膜として利用した第3エッチング工程を行う。

(もっと読む)

集積回路においてソフト・エラー率を低下させるための方法および構造体

【課題】 集積回路においてソフト・エラー率を低下させるための改良された方法および構造体を提供する。

【解決手段】 集積回路においてソフト・エラー率を低下させるための構造体および方法。この構造体は、半導体基板と、最下部の配線レベルから最上部の配線レベルまで積層された1つ以上の配線レベル積層であって、最下部の配線レベルが最上部の配線レベルよりも半導体基板に近い、配線レベル積層と、1つ以上の配線レベルの最上部の配線レベルの上面上のアルファ粒子ブロック層と、を含む。ブロック層は金属配線および誘電材料を含む。ブロック層は、このブロック層に当たる選択されたエネルギ以下のアルファ粒子の所定の割合が1つ以上の配線レベル積層内または基板内に侵入することを阻止するのに充分な前記ブロック層の厚さおよび前記ブロック層内の金属配線の体積百分率の組み合わせを有する。

(もっと読む)

半導体素子の製造方法

【課題】ゲートパターン形成後に行うライト酸化時に、タングステンシリサイド膜などのシリサイド膜の側面が膨出する現象を防止することができる半導体素子の製造方法を提供すること。

【解決手段】半導体基板21上にゲート絶縁膜23を形成するステップと、ゲート絶縁膜23上にポリシリコン膜24、シリサイド膜25及びハードマスク形成用膜の順に積層するステップと、ハードマスク26を形成するステップと、ハードマスク26をエッチングバリアとしてシリサイド膜25をエッチングし、側面にアンダーカット状凹部25Aを形成するステップと、ハードマスク26をエッチングバリアとして、ポリシリコン膜24をエッチングして、ゲートラインを形成するステップと、ライト酸化により、ポリシリコン膜24及びシリサイド膜25の側面を酸化するステップとを含む。

(もっと読む)

半導体素子のコンタクト孔の形成方法

【課題】ハードマスクとして用いられる窒化膜とその下部にILD膜として用いられる酸化膜との間の応力差により発生するリフティング現象を防止して、半導体素子の特性を改善させ得る半導体素子のコンタクト孔の形成方法を提供すること。

【解決手段】下地層(10〜16)が形成された基板を提供するステップと、下地層(10〜16)を覆う絶縁膜(17)を形成するステップと、絶縁膜(17)上にSRON膜でハードマスク(18)を形成するステップと、ハードマスク(18)上にフォトレジストパターンを形成するステップと、フォトレジストパターンを利用した第1エッチング工程により、ハードマスク(18)をエッチングするステップと、フォトレジストパターンを利用した第2エッチングにより、絶縁膜(17)をエッチングし、下地層の一部を露出させるコンタクト孔(19)を形成するステップとを含む。

(もっと読む)

プラズマエッチング方法及びプラズマエッチング装置

【課題】エッチング能力およびエッチング均一性に優れた平行平板型プラズマエッチング方法を提供すること。

【解決手段】このプラズマエッチング装置は、下部電極16を電気的にカソードカップリング配置としている。下部電極16には、それぞれ第1および第2の整合器36,38を介して第1および第2の高周波電源40,42が電気的に接続されている。第1の高周波電源40は、主としてプラズマの生成に寄与するための好ましくは10MHz〜30MHzの周波数を有する第1の高周波RFsを所望のパワーで出力する。第2の高周波電源42は、主として自己バイアスVdcの調整に寄与するための好ましくは2MHz〜6MHzの周波数RFbを所望のパワーで出力する。

(もっと読む)

最新のLow−k材料のための紫外線硬化法

【課題】最新のLow−k材料のための紫外線硬化法の提供。

【解決手段】改善された弾性率及び材料硬度を有する低誘電率材料。このような材料の製造方法は、誘電材料を準備すること、及び、該材料を紫外線(UV)硬化させて、UV硬化誘電材料を製造することを含む。UV硬化は、改善された弾性率及び材料硬度を有する材料をもたらす。改善は、それぞれ、典型的には、50%より大きいか、又は約50%である。UV硬化誘電材料は、所望により、UV後処理され得る。UV後処理は、LIV硬化誘電材料と比べて、材料の誘電率を低下させ、更に、改善された弾性率及び材料硬度を維持する。UV硬化誘電体は、更に、炉での硬化法よりも、硬化において、より低い総熱量を示し得る。

(もっと読む)

半導体素子の導電配線形成方法

【課題】素子の動作特性及び信頼性を向上させることができる半導体素子の導電配線形成方法を提供することである。

【解決手段】導電層及びハードマスク層を備えた半導体基板の上部に導電配線領域を定義する感光膜パターンを形成する段階と、前記感光膜パターンをマスクとして前記ハードマスク層をエッチングしてハードマスク層パターンを形成する段階と、前記感光膜パターンを取り除く段階と、前記ハードマスク層パターンをマスクとして導電層をエッチングする段階とを含み、これらの段階は、インサイチュー(In-situ)工程で進める。

(もっと読む)

low−k誘電体膜を処理するためのイオン注入を使用する方法およびとシステム。

【課題】 low−k誘電体膜を処理するためのイオン注入を使用するための方法とシステム。

【解決手段】 基板上の機械的に強化されたlow−k誘電体膜を形成するシステムおよび方法は、基板上にlow−k誘電体膜を形成するスピオン誘電体(SOD)技術か、化学的気相成長のいずれか使用することを含む。low−k誘電体膜の上部表面は、そこで、膜の機械的強度を増やすか、またはその誘電率を低下させるために処理される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】良好な抵抗値を示すコンタクトプラグを備えた半導体装置の製造方法を提供する

こと。

【解決手段】

コンタクトプラグを備えた半導体装置の製造方法であって、半導体シリコン基板表面に設けられた高濃度N導電型拡散層の表面部分および層間絶縁層により形成されたコンタクトホールを通じて、加速エネルギーを30〜120keVの範囲とし、注入量を1.0×1013〜5.0×1014/cm2の範囲としてインジウムイオンを注入するこにより、前記コンタクトホール下部の前記高濃度N導電型拡散層の表面部分にインジウム含有層を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体素子の製造方法

【課題】接続層の形成が完了した下部構造物の上に形成される金属配線のステップカバレッジ特性を改善して信頼性を向上可能な半導体素子の製造方法を提供すること。

【解決手段】接触口(23)に沿って層間絶縁膜(22)上にTiNバリア金属膜(44)を形成するステップと、TiNバリア金属膜上にタングステン膜を形成するステップと、タングステン膜に対して過度エッチングを伴う第1エッチングを行い、接触口の内部に埋め込まれるタングステンプラグ(45A)を形成するステップと、露出したTiNバリア金属膜に対して第2エッチングを行い、第1エッチング時に生成された接触口のトップ部の側壁の垂直プロファイルをスローププロファイル(45D)に緩和させるステップと、全面にアルミニウム膜を形成するステップと、該アルミニウム膜を選択的にパターニングし、アルミニウム金属配線を形成するステップとを含む。

(もっと読む)

導電膜修正方法、積層構造物及び薄膜トランジスタ

【課題】 導電膜の修正において、修正箇所周辺における導電膜の連続性を確保する。

【解決手段】 下地層5の表面に形成された第1の導電膜6の端部を緩斜面状に整形する工程と、この緩斜面と下地層5の露出部とに渡って第2の導電膜10を形成する工程とによって修正を行う。

(もっと読む)

平行電磁放射線を用いて薄膜内の引張応力を増大させる方法及びシステム

基板上に形成された例えば窒化シリコン膜などの薄膜において、その引張応力を増大させる方法及びシステムが提供される。薄膜は平面状の膜であってもよいし、例えばNMOSゲート上に形成された窒化膜などの非平面状の膜であってもよい。薄膜は該膜を非等方的に曝す平行電磁(EM)放射線に曝される。EM放射線は約500nm未満の波長を有する成分を有する。EM放射線源は多周波放射線源を含み得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】層間膜にSiOC膜を用いた半導体装置の信頼性を向上することのできる技術を提供する。

【解決手段】Si−CH3結合とSi−O結合との結合比が2.50%未満のSiOC膜で層間膜を形成する、あるいはSiO−O結合に対するSi−OH結合の強度比が0.0007を超える、SiO−O結合に対する波長2230cm−1におけるSi−H結合の強度比が0.0050を超える、およびSiO−O結合に対する波長2170cm−1におけるSi−H結合の強度比が0.0067を超えるSiOC膜で層間膜を形成することにより、層間膜の比誘電率を3以下とすると共に、硬度または弾性率の低下を抑えて層間膜の機械的強度の向上を図る。

(もっと読む)

機械的特性を改善するためのその場に埋め込まれたナノ層を有する低k誘電体CVD膜の形成方法(誘電体スタック及び該形成方法、並びに該誘電体スタックを含む相互接続構造体)

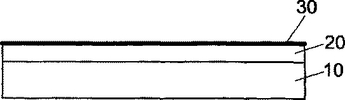

【課題】 機械的特性を改善するために内部に埋め込まれたナノ層を有する低k誘電体CVD膜の形成方法を提供すること

【解決手段】 約1×10−10m/秒又はそれ以上の亀裂速度を有する1つ又は複数の膜(14)と、この1つ又は複数の膜(14)内にあるか又はそれに直接接触した少なくとも1つのナノ層(16)を含む材料スタック(12)が提供され、ここで少なくとも1つのナノ層(16)は、材料スタック(12)の亀裂速度を1×10−10m/秒より小さな値に減少させる。1つ又は複数の膜(14)は、低k誘電体に限定されず、金属のような材料を含むことができる。好ましい実施形態においては、約3.0又はそれ以下の有効誘電率kを有する低k誘電体スタック(12)が提供されるが、そのスタック(12)の機械的特性は、少なくとも1つのナノ層(16)を誘電体スタック(12)内に導入することによって改善される。機械的特性の改善は、スタック(12)内の膜の誘電率を著しく増大させることなく、また本発明の誘電体スタック(12)に何らかの後処理ステップを施すことを必要とせずに、達成される。

(もっと読む)

超低k(ULK)SiCOH膜および方法

【課題】 誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および、かかる膜の製造方法を提供すること。

【解決手段】 本発明は、弾性係数および硬度が改善した多相超低k膜、ならびにこれを形成するための様々な方法を提供する。多相超低k誘電膜は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。  (もっと読む)

(もっと読む)

半導体素子の配線形成方法

【課題】トレンチ内に主金属配線材料の占有体積を十分確保すると同時に、Fアタック問題およびWボルカーノ問題を防止することが可能な半導体素子の配線形成方法を提供する。

【解決手段】所定の構造物が形成された半導体基板に層間絶縁膜を形成する段階と、前記層間絶縁膜に半導体基板の一定の領域を露出させるトレンチを形成する段階と、前記トレンチを含んだ全表面上に接着層と第1バリア金属膜を順次形成する段階と、前記トレンチの下部に第2バリア金属膜を形成する段階と、前記トレンチ内に配線を形成する段階とを含んでなる。

(もっと読む)

原子層堆積のための表面のプラズマ前処理

集積回路内のデュアルダマシン構造のコンフォーマルなライニングのための方法および構造を提供する。好ましい実施形態は、多孔性物質で形成された開口を覆うコンフォーマルなライニングの提供に向けられる。トレンチが絶縁層内に形成される(100)。その後、その層が、特別のプラズマプロセスで適切に処理される(101)。このプラズマプロセスに引き続き、自己制限的、自己飽和的原子層堆積(ALD)反応(115)が、細孔の著しい埋め込みなしに起こり、改善された相互接続を形成する。 (もっと読む)

薄膜の製造方法

【課題】LISの更なる高集積化に伴って要求されている超微細化孔への埋め込み特性や、精密な段差被覆性の実現が可能な薄膜の製造方法を提供すること。

【解決手段】プラズマCVD法によって基体上に金属原子含有薄膜を製造する方法であり、基体にパルスバイアス電圧を印加しながら該金属原子含有薄膜を形成する薄膜の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 貫通配線などの導電体層と半導体基板とを絶縁する絶縁体層を安定して形成することができ、かつ導電体層と表面電極との電気的接続を確実に行なうことのできる半導体装置の製造方法を提供する。

【解決手段】 表面電極23およびレジストパターン24をマスクとして半導体基板21をエッチングするとともにレジストパターン24のレジスト開口部24aを広げるエッチングと、エッチング後に露出する半導体基板21、表面電極23およびレジストパターン24などの表面部にポリマ膜26を形成する重合とを繰返し行ない、半導体基板21に孔部25を形成する。次いで、ポリマ膜26を除去して表面電極23を露出させ、絶縁材料を表面電極23に接するようにして孔部25に供給し、孔部25の側壁部に側壁絶縁膜を形成する。

(もっと読む)

高度な低誘電率の有機シリコン・プラズマ化学気相堆積膜

【課題】 良好な電子特性及び機械的特性を示す、多孔質の低k又は超低k誘電体膜を提供すること。

【解決手段】 約3.0未満の誘電率と、より度合いが大きい結晶結合相互作用と、従来技術のSiCOH誘電体と比べて、より多くのメチル末端基などの炭素と、より少ないメチレン、−CH2−架橋基とを有する、共有結合三次元ネットワーク構造において、Si、C、O及びHの原子(以下、「SiCOH」)を含む多孔質低k又は超低k誘電体膜が提供される。SiCOH誘電体は、約1.40未満のCH3+CH2伸縮についてのピーク面積と、約0.20未満のSiH伸縮についてのピーク面積と、約2.0より大きいSiCH3結合についてのピーク面積と、約60より大きいSi−O−Si結合についてのピーク面積とを含むFTIRスペクトルと、約20%より大きい多孔度とを有するものとして特徴付けられる。

(もっと読む)

141 - 160 / 197

[ Back to top ]