Fターム[5F033WW07]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | エネルギー (197)

Fターム[5F033WW07]に分類される特許

181 - 197 / 197

半導体素子の製造方法

【課題】 シリコンを含むN型の導電領域と直接接続される導電パターンの形成時に、N型の導電領域と接続される部分のコンタクト抵抗の増大を防止し、バリア膜の厚さ増大に伴う導電パターンの寄生容量の増大を防止できる半導体素子の製造方法を提供すること。

【解決手段】 シリコンを含むN型の導電領域(207)にN型の不純物をドープして、N型の高濃度不純物拡散領域(212)を形成する工程と、CVD法を用いて高濃度不純物拡散領域(212)上にバリア用第1金属膜を蒸着し、高濃度不純物拡散領域(212)のシリコンと前記第1金属膜の金属とを反応させて、高濃度不純物拡散領域(212)と前記第1金属膜との間の界面に金属シリサイドを形成する工程、前記第1金属膜上に導電膜を形成する工程、及び、前記導電膜と前記第1金属膜とを選択的にエッチングして、導電パターンを形成する工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

微細構造の作製方法及び作製装置

【課題】 電子線によるガスデポジション法で作製したものと同サイズ(ナノメートルオーダー)の微細構造を、位置とサイズを自由に制御しつつ、任意の材料、結晶性にて作製することができる新規な作製方法及び作製装置を提供する。

【解決手段】 マスクの原料となる元素を含んだガスを材料上に流しながら、電子線を材料上の所望位置に向かって照射してマスクを形成した後、エネルギービームを照射してマスクで被覆された部分以外の材料部分を取り除くことにより、材料に微細加工を行う。

(もっと読む)

半導体デバイスにおけるレベル内またはレベル間誘電体としての超低誘電率材料を製造するための改良した方法およびこれによって作成される電子デバイス

【課題】 誘電率が低く、熱安定性を有する誘電材料を提供する。

【解決手段】 プラズマ化学気相成長(PECVD)プロセスを利用して、平行板化学気相成長プロセスにおいて、Si、C、O、およびH原子を含む熱的に安定した超低誘電率膜を製造するための方法を開示する。更に、この方法によって作成された熱的に安定した超低誘電率材料の絶縁層を含む電子デバイスを開示する。熱的に安定した超低誘電率膜の製造を可能とするため、例えばジエトキシメチルシラン(DEMS)のようなシラン誘導体、および、例えばビシクロヘプタジエンおよび酸化シクロペンテンのような有機分子等、特定の前駆物質材料を用いる。

(もっと読む)

フルオロカーボン化学エッチングにおけるH2添加物を使用しての炭素ドープ酸化ケイ素エッチング

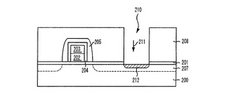

実施例はエッチング材料の供給(210)、水素を含む混合ガスの適用(230)、プラズマの発生(240)、エッチング材料のエッチング(250)を含むエッチング方法(200及び1600)を含む。エッチング材料は低k誘電性材料を含み得る。混合ガスは水素ガス、水素非含有フルオロカーボン、窒素ガスを含み得る。また、1つ以上のハイドロフルオロカーボンガス、不活性ガス、及び/又は一酸化炭素を含み得る。水素ガスとしては、H2、CH4、C2H4、NH3、及び/又はH2Oガスを含む、二原子水素、炭化水素、シラン、及び/又はフッ素非含有水素ガスであってもよい。水素非含有フルオロカーボンガスはCxFyガス(x≧1、y≧1)、ハイドロフルオロカーボンガスはCxHyFzガス(x≧1、y≧1、z≧1)であってもよい。混合ガスは酸素非含有であってもよい。実施例は減圧、低流量水素、1つ以上のプラズマ周波数を含み得る。

(もっと読む)

(もっと読む)

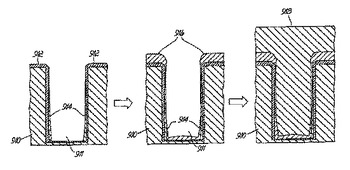

イオン化物理蒸着方法

iPVDシステム(200)は、真空チャンバー(30)内で突出部(14)を最小化または除去しながら、フィールド(10)と底部(15)被覆と比較して側壁(16)被覆性を向上させる処理を用いて、障壁層材料(912)のような均一な材料を半導体基板(21)上の高いアスペクト比のナノサイズの開口部(11)に蒸着するために調整される。そのiPVDシステム(200)は、そのターゲットから材料をスパッタするために、低いターゲットパワーと50mTより高い圧力で動作される。RFエネルギーは、高密度プラズマを生成するそのチャンバーに連結される。小さなRFバイアス(数ボルト未満)は、特に、底部における被覆性を高めることを助けるために印加されることができる。  (もっと読む)

(もっと読む)

低誘電率ナノ細孔性膜の多段階硬化

本発明に従った実施形態は、化学気相堆積された低誘電率材料の多段階硬化プロセスに関する。特定の実施形態では、電子ビーム放射および熱暴露ステップの組合せが、膜に組み込まれているポロゲンの選択的脱ガス化をコントロールするために採用されてもよく、ナノ細孔の形成をもたらす。一具体的な実施形態によると、シリコン含有成分と、不安定基を特徴付ける非シリコン含有成分との反応に起因する低誘電率層は、電子ビーム形態の放射印加が続く熱エネルギーの初期印加によって硬化されてもよい。 (もっと読む)

配線構造の形成方法及び半導体装置

下層配線(101)と不図示の上層配線とを接続するためのビア孔(102)を絶縁膜(103)にエッチングストッパー膜(104)及びハードマスク(105)を用いて形成した後、本発明の1ステップの低パワー・バイアス・スパッタ法によりビア孔(102)の内壁を覆うように絶縁膜(103)上にTaからなる下地膜(106)を形成する。ここで、ビア孔(102)の内壁面から絶縁膜(103)上にわたって薄く均一な膜厚の下地膜(106)が得られる。このように、比較的簡素な工程により、配線形成上の不都合を生ぜしめることなく、開口の内壁面、即ち側壁面から底面にかけて薄く均一に下地膜を成膜することを可能とし、信頼性の高い極微細な配線構造を実現する。

(もっと読む)

(もっと読む)

プラズマ処理システムにおける選択性の制御方法

プラズマ処理システムにおける、半導体基板上の所定の層を介して機能をエッチングするための方法。本方法は、上記プラズマ処理システムのプラズマ処理室に基板を置くことを含む。また本方法は、上記プラズマ処理室内へエッチャント混合気を流し込むことも含み、上記エッチャント混合気は所定の層をエッチングするように構成されている。本方法はさらに、エッチャント・ソース・ガスからのプラズマを打撃することを含む。さらに本方法は、上記基板にバイアスRF信号を印加しながら、上記機能を少なくとも部分的に所定の層を介してエッチングすることを含む。上記バイアスRF信号は約27MHz乃至約75MHzの範囲のバイアスRF周波数と、バイアスRF電力成分とを有し、上記バイアスRF電力成分は、エッチ機能を、基板の第2の層への、予め決められた選択性しきい値より高いエッチング選択性でエッチングさせるように構成され、または上記機能を、バイアスRF周波数における予め決められたエッチ速度パラメータ及びエッチ・プロファイル・パラメータに従ってエッチングさせるように構成される。  (もっと読む)

(もっと読む)

半導体基板導電層表面の清浄化方法

残渣有機物や自然酸化物を十分に除去でき、且つ、ビアホールの側壁絶縁膜にダメージを与えることなく、k値に悪影響を与えることがない半導体基板導電層表面の清浄化方法を提供する。

半導体基板の導電層1表面上に絶縁膜2,3が形成され、絶縁膜3には

導電層1の一部を露出するビアホール4が形成された半導体装置を反応容器内に搬入し、反応容器内に水素を含むプラズマを発生させて、ビアホール4底部の導電層1上を清浄化し、アッシングにより残渣有機物6を分解除去し、導電層1表面上の銅酸化膜7をCuに還元する。

(もっと読む)

トレンチエッチングのためのラインエッジ粗さ低減

【課題】基板上の誘電体レイヤにおいてトレンチ深さまでトレンチをエッチングする方法を提供する。

【解決手段】ARCが前記誘電体レイヤ上に設けられる。厚さを有するフォトレジストマスクが前記ARC上に形成される。前記ARCがエッチングされる。1:1および2:1の間であるフォトレジストに対する誘電体のエッチング選択性で、トレンチが前記誘電体レイヤ中へエッチングされる。

(もっと読む)

ウエハのエッチング技術

半導体材料(102)のウエハ(100)上に貫通ビア(116、118)をエッチングするための方法(10)であって、ウエハ(100)が前側表面(110)と裏側表面(106)を有する方法を記載する。フォトレジスト材料の層(104)を裏側表面(106)に施用する。その後、フォトレジストの層(104)を、予め選択されたパターンを有するマスクを介して光源に暴露し、ここにおいて、現像されたフォトレジストを除去して、残存フォトレジスト層(104’)に少なくとも1つのビア(112、114)を形成させる。その後、残存フォトレジスト層(104’)を焼き付けて、硬化した残存フォトレジスト層(104’)を形成させる。その後、少なくとも1つのビア(112、114)に隣接する半導体材料(102)をガスプラズマエッチングして、裏側表面(106)と前側表面(110)の間に貫通ビア(116、118)を形成させる。その後、硬化した残存フォトレジスト層(104’)を除去し、続いて伝導性材料の層(120)を貫通ビア(116、118)の表面に施用して、裏側表面(106)と前側表面(110)の間に電気接続性を確立する。 (もっと読む)

金属の化学的機械的研磨用の新規なスラリー

一般に集積回路の製造に有用な、金属を取り除くための、及び、特に貴金属の化学的機械的研磨用の、スラリーは、過ヨウ素酸、研磨剤、及び緩衝系を組み合わせることによって、形成されてもよく、ここでそのスラリーのpHは、約(4)と約(8)との間にある。

(もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

銅メタライゼーションのためのALD窒化タンタルの集積

窒化タンタル/タンタルバリア層を堆積させるための方法および装置が、集積処理ツールでの使用のために提供される。遠隔発生プラズマによる洗浄ステップの後、窒化タンタルは原子層堆積法で堆積され、タンタルはPVDで堆積される。窒化タンタル/タンタルは、堆積された窒化タンタルの下の導電性材料を露呈するために、誘電体層の部材の底部から除去される。場合によって、さらなるタンタル層が、除去ステップの後に物理気相堆積法で堆積されてもよい。場合によって、窒化タンタル堆積およびタンタル堆積は同一の処理チャンバで生じてもよい。シード層が最後に堆積される。 (もっと読む)

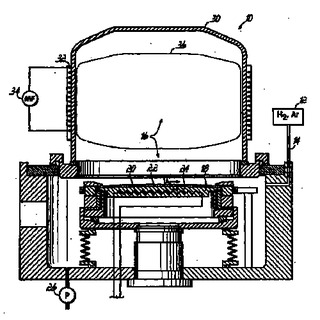

高温水素含有プラズマによるチャンバ及びウェーハ表面から物質を除去する方法及び装置

半導体ウェーハ処理装置(10)のチャンバ(16)と、清掃されるべき表面にバイアス電圧を掛けることなくガス混合物中に高密度プラズマを生成するためのみのICP電源と、に供給される、水素及び不活性ガスから成る清掃ガス混合物、例えば、水素含有量が体積で20%から80%の間にある混合物を使用する清掃方法が提供される。本発明の実施形態では、Si及びSiO2汚染物質又はCFx汚染物質は引き続く金属被着に先立ってシリコン・コンタクト(46)から清掃される。本発明の別の実施形態では、基準酸化物エッチング速度を回復するために酸化物をエッチングする以前にシリコン残留物は内部チャンバ表面から清掃される。

(もっと読む)

(もっと読む)

配線構造とその製造方法

【課題】 誘電率の低い有機物を主成分とする層間絶縁膜層に接して金属又は化合物の薄層からなる拡散障壁層の相互間の結合が強く、その界面で剥離・脱離が発生することのない配線構造及びその製造方法を提供すること。

【解決手段】 誘電率の低い有機物を主成分とする層間絶縁膜層に接して金属又は化合物の薄層からなる拡散障壁層を堆積・被覆し、該拡散障壁層に接して導電部分を配設することによって構成される配線構造であって、層間絶縁膜層(有機絶縁膜層)30と拡散障壁層との界面付近に高速粒子照射により両側の部材を構成する原子又は分子が互いにミキシングされた状態のミキシング領域(ミキシング層31)を形成した。

(もっと読む)

181 - 197 / 197

[ Back to top ]