Fターム[5F033WW07]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | エネルギー (197)

Fターム[5F033WW07]に分類される特許

161 - 180 / 197

半導体装置およびその製造方法

【課題】 ポリイミド等の有機絶縁膜の表面荒れを抑制しつつ、効果的に有機絶縁膜上の変質層を除去して、半導体装置の表面リークを防止する。

【解決手段】 半導体装置に接続電極を形成する。前記接続電極の中央部が露出するように、隣接する接続電極間を連続的に覆う有機皮膜を形成する。露出した接続電極の表面をドライエッチングで処理する。前記表面処理により有機皮膜の表層に形成された変質層を、酸素を用いないドライ工程により除去する。

(もっと読む)

機能性基板の製造方法、機能性基板、微細パターンの形成方法、導電膜配線、電子光学装置および電子機器

【課題】 液体プロセスによる微細パターンの薄膜の形成を確実に行うことが可能な機能性基板を提供すること、当該機能性基板の製造方法を提供すること、所望のパターンの薄膜を確実に形成することが可能な微細パターンの形成方法を提供すること、断線、短絡等のない微細なパターンの導電膜配線を提供すること、当該導電膜配線を備えた電子光学装置、電子機器を提供すること。

【解決手段】 本発明の機能性基板の製造方法は、基板本体に第1の処理を施す第1の工程と、第1の処理が施された基板本体上に自己組織化膜を形成する第2の工程とを備え、自己組織化膜の所定の液滴に対する後退接触角をA[°]、自己組織化膜の前記液滴に対する前進接触角をB[°]としたとき、A/B≦0.60の関係を満足するように、第1の処理の処理条件および自己組織化膜の形成条件を設定することを特徴とする。

(もっと読む)

半導体デバイスの製造方法

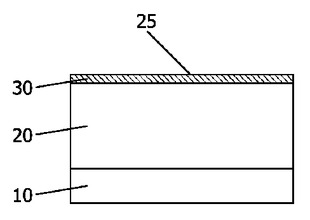

本発明は、半導体デバイスの製造方法に関するものである。この方法では、半導体デバイスは、基板(10)を具え、この基板(10)は、表面(25)を有する低−kの前駆物質層(20)で覆われている。この工程の後、部分硬化工程が行われ、前記低−kの前駆物質層(20)の表面(25)またはその近くに緻密層(30)が形成される。この緻密層(30)は、保護層(30)として作用することができる。前記低−kの前駆物質層(20)は、未硬化、または部分的に硬化された状態で適用できる特性を有する材料の群から選択される。この方法の主な利点は、前記緻密層(30)が、前記低−kの前駆物質層(20)自体から形成されるため、別個の保護層(30)を低−kの前駆物質層(20)に設ける必要がない点である。したがって、前記緻密層(30)は、前記低−kの前駆物質層(20)に対して良好な接着性を有する。  (もっと読む)

(もっと読む)

CMOSFET内の歪みを最適化するための構造体及び方法

【課題】 CMOSFET内の歪みを最適化するための構造体及び方法を提供すること。

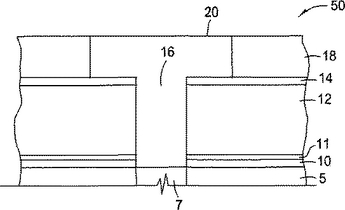

【解決手段】 MOSFET内の歪みを最適化し、より具体的には、1つの種類(P又はN)のMOSFET内の歪みを最大にし、かつ、別の種類(N又はP)のMOSFET内の歪みを最小にし緩和する、PMOSFET及びNMOSFETの両方を含む歪みMOSFETの半導体構造体、及び歪みMOSFETを製造する方法が開示される。元の完全な厚さを有する歪み誘起CA窒化物コーティングが、PMOSFET及びNMOSFETの両方の上に形成され、この歪み誘起コーティングは、1つの種類の半導体デバイス内に最適化された十分な歪みをもたらし、別の種類の半導体デバイスの性能を劣化させる。歪み誘起CA窒化物コーティングは、別の種類の半導体デバイスの上で減少した厚さまでエッチングされ、減少した厚さの歪み誘起コーティングは、他方のMOSFET内でより少ない歪みを緩和し、他方のMOSFET内により少ない歪みをもたらす。

(もっと読む)

半導体装置の製造方法

【課題】機械的強度が十分に強く、しかも、比誘電率が極めて低い絶縁膜を有する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に多孔質の第1の絶縁膜38を形成する工程と、第1の絶縁膜上に、第1の絶縁膜より密度の高い第2の絶縁膜40を形成する工程と、第1の絶縁膜上に第2の絶縁膜が存在している状態で、電子線、紫外線又はプラズマを照射し、第1の絶縁膜を硬化させる工程とを有している。緻密性の高い第2の絶縁膜を介して第1の絶縁膜に電子線等を照射するため、第1の絶縁膜に大きなダメージが加わるのを防止しつつ、第1の絶縁膜を硬化させることができる。第1の絶縁膜にダメージが加わるのを防止することができるため、吸湿性の増大や密度の増大を防止することができ、ひいては、比誘電率の増大を防止することができる。従って、比誘電率が低く、しかも機械的強度の高い絶縁膜を有する半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法とそのような方法により得られる半導体装置

この発明は、半導体本体(1)と基板(2)とを備えた半導体装置(10)であって、少なくとも一つの半導体素子(3)を備え、そして、少なくとも一つの接続領域(4)と、接続領域(4)に接続された上部に横たわる帯状接続導体(5)とが設けられ、帯状接続導体と接続領域とが共に誘電体材料内に窪んでおり、続いて、第一の誘電体層(6)と、第一のハードマスク層(7)と、そして、第二の誘電体層(8)とが半導体本体(1)上に堆積され、接続領域(4)が形成される部位において、炭素とフッ素との化合物を含むプラズマを用いたプラズマエッチングにより第一の誘電体層(6)内にバイア(44)が形成され、そして、この構造の上部に堆積されたパターンニングされたフォトレジスト層が存在している状態で、接続導体(6)が形成される部位において、プラズマエッチングにより第二の誘電体層(8)内にトレンチ(55)が形成され、接続領域(4)と接続導体(5)とをそれぞれ形成するために、バイア(44)及びトレンチ(55)が導電材料で満たされ、そして、トレンチ(55)が形成される前に、既に形成されたバイア(44)が有機材料(2)で満たされる半導体装置の製造方法に関する。この発明では、バイア(44)のエッチング中にバイア(44)が同時にほぼ完全に有機材料(20)で満たされるように、第一の誘電体層(6)の材料と、プラズマエッチングによる第一の誘電体層(6)内のバイア(44)の形成中のエッチング条件とが選ばれ、この構造及びプラズマ内に既に存在する有機材料から有機材料(20)が形成される。エッチングの間にレジスト層が存在することと、そこで炭素とフッ素との化合物を用いること以外に、関わる条件は、第一(そして第二)の誘電体層(6,8)とこれら層(6,8)のエッチングの間の電力の選択に関する。  (もっと読む)

(もっと読む)

半導体デバイスの多重波長レーザ微細加工

【課題】高品質の加工及び多重波長でのレーザエネルギーがレーザエネルギープロファイルに重なることができるより小さい可能なスポットサイズを達成するために半導体デバイス微細加工に対して目標とされる実質的にジッタのない多重波長レーザエネルギープロファイルを提供する。

【解決手段】異なる時間で異なるレーザ波長によって特徴付けられる特別に成形されたレーザパルスエネルギープロファイル(98,104,156)は、高品質加工及びより小さい可能なスポットサイズを達成する半導体デバイスの微細加工を可能にするために軽減制御ジッタを提供する。

(もっと読む)

半導体素子の製造方法

【課題】MLM(Metal Layer Metal)工程の際に絶縁膜に発生するクラック(crack)の抑制に適した半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、(a)第1絶縁膜の形成された基板上にメタルラインを形成する段階と、(b)前記メタルラインをパターニングする段階と、(c)前記メタルライン上に第2絶縁膜を形成する段階と、(d)熱処理工程を行う段階とを含んでなる半導体素子の製造方法において、前記(b)段階の完了後、前記(c)段階を行う前に熱処理工程により前記メタルラインの応力を緩和させる(e)段階を行う。

(もっと読む)

低誘電率ナノ粒子膜の形成技術

【課題】ナノ粒子の発生自体を制御し、効果的に基板上に低誘電率膜を堆積させる。

【解決手段】低誘電率膜を形成する方法であって、有機Siガスと不活性ガスからなる反応ガス容量結合方式のCVD装置の反応器へ導入する工程、該有機Siガスから気相中に生成する微粒子のサイズを該反応器内におけるプラズマ放電時間の関数として、nmオーダーに調整する工程、及び生成した該微粒子を該反応器内に載置された基板上に堆積する工程、を包含する。

(もっと読む)

半導体装置の製造方法

【課題】 疎水性の低誘電率絶縁膜を用いて、信頼性および電気的特性に優れた半導体装置を製造する方法を提供する。

【解決手段】 アンモニアプラズマ14によって、SiOC膜8の表面に形成された疎水性のダメージ層を親水性の改質層15に変える。改質層15はフッ酸水溶液などに可溶であるので、改質層15を除去することによって、表面に清浄なSiOC膜8を露出させることができる。改質層15の膜厚は0.5nm〜10nmであることが好ましく、1nm〜5nmであることがより好ましい。

(もっと読む)

半導体のための引張り及び圧縮応力をもたせた物質

応力をもたせた膜が基板上に形成される。基板が処理ゾーンに置かれ、処理ゾーンに与えられたシリコン含有ガス及び窒素含有ガスを有する処理ガスのプラズマが形成される。窒素の如き希釈ガスを加えることもできる。堆積直後のままの応力をもたせた物質を、紫外線又は電子ビームに対して露出させることにより、その堆積物質の応力値を増大させることができる。それに加えて、又はそれとは別に、堆積中にその物質の応力値を増大させるために、窒素プラズマ処理を使用することができる。応力をもたせた物質を堆積させるためのパルス化方法も開示する。 (もっと読む)

プラズマエッチングのパフォーマンスを改善する方法

【課題】 エッチングマスクを通して層内にフィーチャをエッチングする方法を提供する。

【解決手段】 前記エッチングマスクの曝露された表面、および前記フィーチャの垂直側壁上に保護コーティングが保護膜形成ガス混合物で形成される。前記フィーチャは、前記エッチングマスクを通して、少なくとも1つのエッチング化学物質および少なくとも1つの保護膜形成化学物質を含む反応性エッチング混合物でエッチングされる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 Cu電極層と有機樹脂膜との密着性寿命を、従来よりも向上させることができる半導体装置およびその製造方法を提供する。

【解決手段】 パワーデバイスと、パワーデバイス上の厚いCu電極層2と、Cu電極層2を覆う有機樹脂膜3とを備える半導体装置において、Cu電極層2の表面(上面2aと側面2b)の全領域を覆うように、Cu窒化膜8を配置する。ここで、Cu電極層2と有機樹脂膜3との密着性を低下させる主原因は、有機樹脂膜3を通過した酸素がCu電極層2と反応して、Cu電極層2の表面に酸化膜が生成することである。そこで、Cu電極層2と有機樹脂膜3との間の領域に、酸素の透過を抑制することができるCu窒化膜8を配置することで、Cu電極層と有機樹脂膜との密着性寿命を、従来よりも向上させることができる。

(もっと読む)

フッ素ドープ低誘電率絶縁膜を形成する方法

【課題】低誘電率及び高熱安定性を有するフッ素ドープ低誘電率シリコン酸化膜を形成する方法を与える。

【解決手段】容量結合プラズマCVDにより、低誘電率シリコン酸化膜を形成する方法は、シリコンソースガスとしてSiH4、フッ素ソースガスとしてSiF4、及び酸素ソースガスとしてCO2から成る処理ガスを、(SiH4+SiF4)/CO2が約0.02から約0.2の範囲となるような流量比で、かつ、全圧が約250Paから約350Paとなるように反応チャンバへ導入する工程と、約10MHzから約30MHzの周波数の第1RF電力及び約400kHzから約500kHzの周波数の第2RF電力を印加する工程であって、2つのRF電力を重畳させることにより、反応チャンバ内部にプラズマ反応場を生成するところの工程と、それぞれのガスの流量及びそれぞれのRF電力出力を制御する工程と、から成る。

(もっと読む)

絶縁膜形成用組成物、絶縁膜、およびその形成方法

【課題】 本発明は、半導体素子などにおいて好適に用いられる膜形成用組成物、ならびに絶縁膜およびその形成方法を提供する。

【解決手段】 本発明にかかる絶縁膜形成用組成物は、(A)ゼオライトのMFI構造を有し、前記MFI構造を構成するシロキサンの10員環によって形成される孔内に含窒素化合物が存在する、ポリオルガノシロキサン化合物と、(B)ポリカルボシラン化合物とを、有機溶媒の存在下で混合し、加熱することにより得られる化合物を含有する。

(もっと読む)

多孔質膜の堆積方法

【課題】基板上に多孔質膜を堆積させる処理方法を提供する。

【解決手段】多孔質シリカ膜及びドープシリカ膜を堆積させる処理方法。本方法は、循環方式を用い、各サイクルは、最初にシリカをシリコンと共に共堆積させる段階と、次に選択的にシリコンを除去して多孔質構造体を形成する段階とを含む。好ましい実施形態では、共堆積は、プラズマ強化化学気相蒸着によって行われる。反応剤給送流れは、共堆積反応剤と選択的シリコン除去反応剤との混合物を含む。RF電力変調を使用して、共堆積段階及び選択的シリコン除去段階を制御し、後者は、RF電力が切られるか又は低レベルに低減される度に進行する。本発明を用いて、高度に均一な小さな孔隙及び望ましい空隙率プロフィールを有する多孔質膜を取得することができる。本方法は、半導体集積回路製造のための広範囲の低−k誘電体を形成するのに有利である。本方法はまた、他の用途のための他の多孔質膜を形成するのにも有利である。

(もっと読む)

半導体素子のキャパシタ形成方法

【課題】半導体素子のキャパシタの形成方法を提供する。

【解決手段】この方法は、フッ素および酸素を含む環境で金属窒化膜をエッチングしてキャパシタ電極を形成する段階を含む。そして、前記金属窒化膜はフッ素プラズマを含む環境でプラズマエッチングされるようにしてもよい。また、前記フッ素はCF4及びCHF3のうちで少なくとも一つであるようにしてもよい。さらに、前記金属窒化膜はチタン、タンタル及びタングステンのうちで少なくとも一つを含むようにしてもよい。また、前記金属窒化膜は600W以下のパワーが供給された環境でプラズマエッチングされるようにしてもよい。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】レジストを「焦げ」の発生を防ぎつつ除去し、さらにプラズマ酸化珪素膜を半導体ウェハ内部の不純物の再分布を抑制しながら高速に形成する半導体素子の製造方法及び半導体素子を提供する。

【解決手段】レジスト301の灰化時には低めのRF電力を用いることで、レジスト301の「焦げ」の発生を防いで灰化する。レジスト301の灰化が終了した時点から高めのRF電力に切り替えることで酸化レートの高いプラズマ酸化を行い、ポリシリコンからなるN型配線部103、P型配線部104の表面に不純物の外方拡散防止膜としてのプラズマ酸化珪素膜401を形成する。熱工程を行うことなくポリシリコンをくるむようにプラズマ酸化珪素膜401を形成するため、半導体ウェハ101中の不純物を殆ど再分布させない。

(もっと読む)

半導体素子のパッシベーション膜形成方法及び半導体素子のパッシベーション膜構造

【課題】 本発明は、選択ソースラインと共通ソースライン間の漏れ電流を著しく減少させることが可能な半導体素子のパッシベーション膜形成方法及び半導体素子のパッシベーション膜構造を提供することを目的としている。

【解決手段】 半導体基板上に金属配線を形成する段階と、前記金属配線上にプラズマによる損傷を緩衝することが可能な第1パッシベーション膜のバッファ酸化膜を形成する段階と、前記バッファ酸化膜上に第2パッシベーション膜の高密度プラズマ(HDP)膜を形成する段階と、前記第2パッシベーション膜上に第3パッシベーション膜を形成する段階とを含んで半導体素子のパッシベーション膜を形成する構成としたことを特徴とする。

(もっと読む)

耐酸化性が良好な次世代ダマシンバリヤ適用のための二層膜

基板を処理する方法であって、フェニル基を含む有機シリコン化合物を含む処理ガスを処理チャンバに供給するステップと、処理ガスを反応させて低k誘電物質によるダマシン又はデュアルダマシン適用においてバリヤ層として用いられる低kシリコンカーバイドバリヤ層を堆積させるステップとを含む、前記方法が提供される。低kシリコンカーバイドバリヤ層上に酸素を含まない有機シリコン化合物を含む処理ガスからのシリコン原子にフェニル基がほとんど結合されていないシリコンカーバイドキャップ層を堆積する方法が提供される。  (もっと読む)

(もっと読む)

161 - 180 / 197

[ Back to top ]