Fターム[5F033XX03]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 微細化 (1,181)

Fターム[5F033XX03]の下位に属するFターム

高アスペクト化 (211)

Fターム[5F033XX03]に分類される特許

141 - 160 / 970

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

導電膜用エッチング液およびエッチング方法

【課題】従来の蓚酸系エッチング液のような界面活性剤配合に伴う泡や蓚酸に由来する残渣の発生を生じることなく、界面活性剤を一切使用しなくても、濡れ性、泡切れ性が優れ、高精度で透明導電膜をエッチングすることができるエッチング液およびエッチング方法を提供すること。

【解決手段】少なくとも蓚酸を主成分とする導電膜用エッチング剤(A)と、(B)群および(C)群から選ばれる少なくとも1種とを含有し、界面活性剤を一切含有しないことを特徴とする導電膜用エッチング液。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の内壁に絶縁膜を形成することにより、接続孔の径を小さくする場合において、接続孔内に導電膜を十分に埋め込むことができるようにする。

【解決手段】接続孔210,220の内壁上に絶縁性の第1膜300を形成し、接続孔210,220の径を細らせる。次いで、第1膜300が形成された接続孔210,220内に、第2膜50を埋め込む。次いで、絶縁膜200の表層を、CMP法を用いて除去する。次いで、接続孔210,220から第2膜50を除去する。次いで、接続孔210,220の第1膜300上および接続孔210,220の底面上にバリアメタル膜330を形成し、さらに接続孔210,220内に導電膜からなるコンタクト310,320を埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

パターンの製造方法

【課題】本発明は、パターンの製造方法に関し、特に、レーザーを用いてパターンを製造する方法に関する。

【解決手段】パターンの製造方法は、基板上に金属有機インク層(20)を形成する第1の段階;前記金属有機インク層(20)を半固体状態に硬化させる第2の段階;前記半固体状態の金属有機インク層(20)にレーザー光を照射し、照射された部分が固体状態に硬化されてパターンが形成される第3の段階、および、前記半固体状態の金属有機インク層(20)を除去して、前記パターンだけを残す第4の段階を含む。

(もっと読む)

パターン製造方法およびパターン形成体

【課題】複数の段差を備えた微細な3次元構造パターンの製造に好適なパターン製造方法を提供すること。

【解決手段】ハードマスク層12の1段目の段差部15’’のパターン位置から所望の距離をずらした位置のレジスト膜13を露光させレジストパターン14’を形成し、レジストパターン14’をマスクとしてハードマスク層12をエッチングすることで、所望の位置に3次元構造の2段目の段差部19を形成出来る。また、ハードマスク層12は基板11に対してエッチング選択比が高い材料であるため、形成する3次元構造パターンに対応する2段目の段差部19の段差は、所望する3次元構造パターンよりも、深さを小さく出来る。また、ハードマスク層12に2段目の段差部19を形成するにあたり、ハードマスク層12を基板11の表面を覆うように残存させることにより、複数段のパターン形成において、基板11の帯電(チャージアップ)を抑制出来る。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

半導体装置及びその製造方法

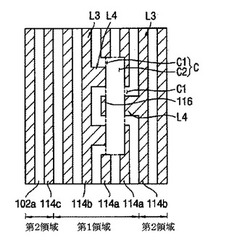

【課題】周期的に配列された複数本の配線と導電部材が設けられ、導電部材に配線よりも高い電圧を印加することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、一方向に延び、周期的に配列された複数本の第1配線と、前記複数本の第1配線からなる群の外側に配置され、前記一方向に延びる第2配線と、前記群と前記第2配線との間に設けられた第3配線と、前記第2配線から見て前記群の反対側に配置された複数の導電部材と、を備える。そして、前記第1配線と前記第3配線との最短距離、及び前記第3配線と前記第2配線との最短距離は、前記第1配線間の最短距離と等しく、前記第2配線と前記導電部材との最短距離は、前記第1配線間の最短距離よりも長い。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体装置の製造方法

【課題】チップ面積の削減が可能な側壁加工プロセスを用いた半導体装置の製造方法を提供すること。

【解決手段】実施形態の半導体装置の製造方法は、基板301上に被加工膜302を形成し、被加工膜の上に芯材膜304を形成し、芯材膜の一部であって被加工膜の加工時まで残存させる残存部分とそれ以外の芯材膜である除去予定部分との間が所定距離の間隙となるように芯材膜をパターニングする。パターニングの後に芯材膜の側面に側壁305を形成して除去予定部分および残存部分の側面を側壁で覆うとともに残存部分と除去予定部分との間の所定距離の間隙を側壁で閉塞する。さらに、側面が側壁で覆われた残存部分の上面を覆うようにレジスト306を形成し、レジストの形成後にウェットエッチングを行うことにより除去予定部分を除去し、ウェットエッチングの後にレジストを除去する。レジストを除去した後に側壁および残存部分をマスクとして被加工膜を加工する。

(もっと読む)

パターン形成方法および積層構造体

【課題】所望のパターンが形成でき、製造工程の迅速化を図ることが可能なパターン形成方法を提供する。

【解決手段】本実施形態のパターン形成方法は、下地10の上に第1の膜11を選択的に形成する工程と、前記第1の膜11および前記第1の膜に覆われていない前記下地10の上に、第2の膜13を形成する工程と、前記第2の膜13の平均結晶粒径を前記第2の膜13の膜厚以上に調整する工程と、前記第1の膜11のエッチャントを前記第2の膜13の表面に晒し、前記第1の膜11の上に形成された前記第2の膜13を前記下地上から選択的に除去する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】プロセスマージンを大きく取れる配線配置構造を提供する。

【解決手段】基板上に形成された複数の第1配線6を含む第1配線層と、第1配線層上に形成され、第1配線6に接続された複数のビアコンタクト10を含むコンタクト層と、コンタクト層上に形成され、ビアコンタクト10に接続された複数の第2配線14を含む第2配線層とを備える半導体装置において、コンタクトピッチは、第1配線6の最小配線ピッチ、又は、第2配線14の最小配線ピッチ、よりも大きくなるようにする。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

回路基板及び表示装置

【課題】 配線の特性の劣化を生じさせることなく、額縁面積を削減することが可能な回路基板、及び、該回路基板を備える表示装置を提供することを目的とする。

【解決手段】 支持基板上にトランジスタ及び外部接続端子が載置されたトランジスタ基板と、該トランジスタ基板上に取り付けられた外付け部材とを含んで構成される回路基板であって、上記外付け部材は、導電部材を介して外部接続端子と電気的かつ物理的に接続されており、上記トランジスタは、外部接続端子と横並びに配置されている回路基板である。

(もっと読む)

半導体装置及び製造方法

【課題】少ない層間接続プロセス工程数で、コンタクト部分の面積を小さくすることのできる半導体装置及び製造方法を提供する。

【解決手段】多層導体配線10は、スルーホール15は、導体13の一部は、ひさし部13Cとしてスルーホール15の内側に露出する。そして、スルーホール15のスルーホール用孔の内側に埋め込まれた埋め込み金属16とひさし部13Cとで、側面コンタクト構造を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に伴うLERやLWRに起因する配線の抵抗率の増大を抑制し得る手法を提供する。

【解決手段】半導体装置は、基板101と、基板上において同一の配線層内に形成された複数の配線111と、配線間に埋め込まれるよう形成された複数の絶縁膜112とを備える。そして、これら複数の配線は、両側面のLER(Line Edge Roughness)の相関係数が正である配線が、連続して2N本(Nは4以上の整数)以上並んだ配線群を含む。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備える。

(もっと読む)

141 - 160 / 970

[ Back to top ]