Fターム[5F033XX03]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 微細化 (1,181)

Fターム[5F033XX03]の下位に属するFターム

高アスペクト化 (211)

Fターム[5F033XX03]に分類される特許

121 - 140 / 970

パターン化金属膜及びその形成方法

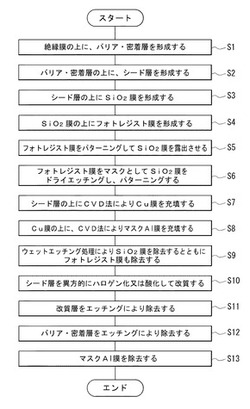

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

半導体装置の製造方法

【課題】 接続孔のホールサイズについて制御性良い半導体装置の製造方法を提供する。

【解決手段】 実施形態の半導体装置の製造方法では、半導体基板上に上層絶縁膜が形成され、前記上層絶縁膜上にSiを含む非晶質膜が形成される。前記非晶質膜上に第1のレジスト膜が形成され、前記第1のレジスト膜に第1のレジストパターンが形成される。前記第1のレジスト膜をマスクとして、前記非晶質膜が加工され、前記上層絶縁膜が露出される。前記第1のレジストパターンが除去され、前記非晶質膜および露出した前記上層絶縁膜上に遷移金属膜が形成される。前記非晶質膜および前記遷移金属膜の熱反応により、前記非晶質膜よりも体積が大きいシリサイド膜が形成される。前記遷移金属膜が除去され、前記シリサイド膜をマスクとして、前記上層絶縁膜を加工し、前記上層絶縁膜に第1の溝が形成される。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積の増大を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1領域、第2領域、及び複数のワード線を備える。第1領域は、電気的に書き換え可能な複数のメモリトランジスタを有する。第2領域は、第1領域の周辺に位置する。複数のワード線は、複数のメモリトランジスタのゲートに各々接続されている。複数のワード線は、各々、配線部、及び接続部を備える。配線部は、第1領域から第2領域に向かうように第1方向に延び且つ第1方向に直交する第2方向に所定距離をもって配列されている。接続部は、配線部から延びて第2領域に設けられ且つ積層方向に延びるコンタクトと電気的に接続されている。複数の接続部の端部は、第2方向に延びる直線に沿って形成されている。

(もっと読む)

半導体装置

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板

【課題】パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板を提供する。

【解決手段】本発明によるパターン転写方法は、基板上にパターン物質を形成する第1段階と、パターン物質を固相状態に硬化させる第2段階と、硬化された固相状態のパターン物質にレーザー光を照射して、パターン物質をパターニングする第3段階と、パターニングされた固相状態のパターン物質と柔軟基板をお互いに突き合わせて加圧して、パターン物質から柔軟基板方向に、または柔軟基板からパターン物質方向にレーザー光を照射して、パターン物質と柔軟基板を突き合わせた部位で発生する柔軟基板の粘性力によって、パターン物質を柔軟基板に転写する第4段階と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

装置

【課題】ボイドが存在しても高い信頼性を確保可能な配線構造を提案する。

【解決手段】実施形態に係わる装置は、第1の溝10を有する絶縁層13と、第1の溝10内に形成され、上部に凹部16を有する銅を含む第1の配線層15と、第1の配線層15の凹部16の内面上に形成され、少なくとも1つのグラフェンシートから構成されるグラフェン層17とを備える。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線間のリークを抑制しつつ、再配線のピッチを微細化するとともに、再配線上のビア開口時のマージンを上げる。

【解決手段】緩衝層4上には再配線7bが形成され、再配線7b上には表面層8bが形成されている。表面層8bは、再配線7bから幅方向にはみ出すようにして再配線7bに沿うように配置され、再配線7bよりもエッチング耐性が高い。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、ヒューズの微細化を図ること。

【解決手段】シリコン基板1に素子分離絶縁膜2を形成する工程と、素子分離絶縁膜2の上に第1の絶縁膜13を形成する工程と、第1の絶縁膜13にスリット13xを形成する工程と、スリット13xを通じて素子分離絶縁膜2をウエットエッチングして凹部2bを形成する工程と、凹部2bとスリット13xの各々の内面に第2の絶縁膜24を形成することにより、第2の絶縁膜24によりスリット13xを塞ぎつつ、凹部2b内にボイド24aを形成する工程と、ボイド24aの上の第2の絶縁膜24にホール25bを形成し、ホール25b内にボイド24aを露出させる工程と、露出したボイド24aとホール25bのそれぞれの中に導電膜27を形成することによりヒューズFを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

多重膜のエッチング液組成物及びそのエッチング方法

【課題】Cu/Mo積層金属膜、Cu/Mo合金積層金属膜、Cu合金/Mo合金積層金属膜のような、銅又は銅合金の1層以上の銅層と、モリブデン又はモリブデン合金の1層以上のモリブデン層とを含む多重膜を、効率的で優秀に同時に一括してエッチングすることができるエッチング液組成物及びこれを用いた多重膜のエッチング方法を提供する。

【解決手段】エッチング液組成物は、総重量に対して、リン酸50〜80wt%;硝酸0.5〜10wt%;酢酸5〜30wt%;イミダゾール0.01〜5wt%;及び残量の水を含む。添加剤イミダゾールは、銅/モリブデンガルバニック反応調節剤として機能する。

(もっと読む)

121 - 140 / 970

[ Back to top ]