Fターム[5F033XX03]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 微細化 (1,181)

Fターム[5F033XX03]の下位に属するFターム

高アスペクト化 (211)

Fターム[5F033XX03]に分類される特許

201 - 220 / 970

マスクの製造方法、及び半導体装置の製造方法

【課題】開孔径が均一で開孔径の制御が容易な、微細化に適した開孔パターンを有するマスクを製造する。

【解決手段】第1及び第2のマスク層内に開孔を設ける。この後、第1のマスク層内の開孔の径よりも第2のマスク層内の開孔の径を、Xの量だけ大きくする。この後、第2のマスク層内の開孔内にマスク材料を形成することによって第2のマスク層内の開孔内に、Xの径の空洞部を形成する。この空洞部を開孔として有する第2のマスク層及びマスク材料を、マスクとして形成する。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ダマシン配線形成時に、シード膜を配線用溝の側壁に確実に形成する。

【解決手段】下地絶縁膜1の上にプラズマシリコン窒化膜2、プラズマTEOS酸化膜3を形成する。プラズマTEOS酸化膜3は、高周波電源および低周波電源を用いる2周波励起プラズマCVD装置により、膜密度が上部に行くほど小さくなるように形成される。配線用溝をRIE法により形成した後、ウェットエッチングで膜密度が小さい部分を速くエッチングすることでテーパ形状の配線用溝3aを形成する。スパッタでバリアメタル膜4を形成する際に配線用溝3aの側壁にも確実に形成でき、銅膜5のメッキをボイドなしに形成できる。

(もっと読む)

半導体装置の製造方法

【課題】内部接続端子にクラックを生じさせない、信頼性を高めたパッケージの製造方法を提供する。

【解決手段】電極パッドを有する半導体集積回路を含む半導体チップが複数配置された半導体基板と、半導体基板上の再配線層とを有する半導体装置の製造方法であって、半導体集積回路の領域の間に位置するスクライブ領域の中に溝部を加工するため、溝部以外の領域を保護する保護マスクを半導体基板に張り付ける、保護マスク張り付け工程(S101)と、溝部を加工する溝部加工工程(S102)と、保護マスクを第1絶縁層の形成のためのスクリーンマスクとして使用して、溝部を覆うように第1絶縁層を形成する、第1絶縁層形成工程(S103)とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】パターン不良を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】被加工膜上に、ラインアンドスペース部と前記ラインアンドスペース部の外側に形成された第一のパターンとを有する第二のパターンを形成し、側壁パターンを前記第二のパターンの側壁に形成し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と反対側の側壁に形成された側壁パターンを除去し、前記第一のパターンの側壁のうち、前記ラインアンドスペース部と対向する側の側壁に形成された側壁パターンに基づき、回路パターンを形成する。

(もっと読む)

半導体装置

【課題】半導体装置において、パッド下方の絶縁膜におけるクラックの発生を抑制する。

【解決手段】半導体装置10は、基板4上に形成された絶縁膜3と、絶縁膜3中に形成された複数の配線20を含む配線層と、絶縁膜3上に形成されたパッド1とを備える。パッド1下方の少なくとも一部を含む領域において、該領域外に比べて隣り合う複数の配線20同士の間隔が狭くなった狭配線間隔領域が構成されている。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ法の露光解像限界未満のラインアンドスペースパターンとなる被加工膜のパターンの上層に、その被加工膜のパターンと接続するコンタクトを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に形成された第2の膜14を、複数の線状部とそれぞれの線状部の一端に形成された線状部よりも幅の広い端部を有するパターンへと加工し、このパターンをスリミングして第1のパターン16を形成し、第1のパターン16の端部141a上を横断する第1の開口180を有する第2のパターンを形成し、第1の開口180内に露出する第2の膜14をエッチングし、端部141aを線状部140aに近い第1の端部142aと、線状部140aと遠い第2の端部143aとに分割することを含む。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

歪み材料を有する半導体デバイス

歪み材料を有する半導体デバイスが開示される。特定の実施形態では、半導体デバイスは、第1ドレインと第1ソースとの間に第1ゲートを含む第1セルを含む。半導体デバイスはまた、第1セルに隣接する第2セルを含む。第2セルは、第2ドレインと第2ソースとの間に第2ゲートを含む。半導体デバイスはさらに、第1ソースと第2ソースとの間にシャロートレンチ分離領域を含む。第1ソースおよび第2ソース上の第1量の歪み材料は、第1ドレインおよび第2ドレイン上の第2量の歪み材料より多い。  (もっと読む)

(もっと読む)

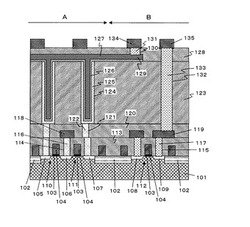

半導体装置及び半導体装置の製造方法

【課題】パッドピッチに対応させてプローブ針の間隔を狭くすることができるようにする。

【解決手段】この半導体装置は、絶縁膜110上に形成されたパッド120と、パッド120に形成された凹部121と、凹部121内に形成された金属層122とを備える。パッド120は接続領域126及びプローブ領域124を備えている。接続領域126にはボンディングワイヤやバンプなどの接続部材が接続される。プローブ領域124は、半導体検査装置のプローブ針が接する領域である。そして金属層122はプローブ領域124に設けられている。パッド120は矩形であり、プローブ領域124は、パッド120のうち半導体装置の内側を向いている辺を含むように形成されている。金属層122は、パッド120よりもイオン化傾向の小さい金属により形成されている。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

半導体装置の製造方法。

【課題】本発明は、埋込みビットラインの抵抗を減少させ高速動作に有利な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、ハードマスク膜をバリアとして半導体基板をエッチングし、複数の活性領域を画定するトレンチを形成するステップと、ハードマスク膜が突出部となるように前記トレンチ内部を一部ギャップフィルするギャップフィル膜を形成するステップと、突出部の両側側壁を覆うスペーサを形成するステップと、ドープドエッチング障壁膜をエッチングバリアとしてスペーサのうち何れか1つのスペーサを除去するステップと、残留するスペーサをエッチングバリアとして前記ギャップフィル膜をエッチングし、活性領域の一側側壁を露出させる側壁トレンチを形成するステップと、を含む。

(もっと読む)

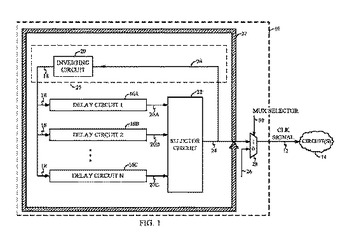

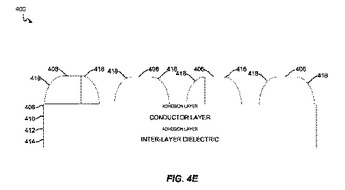

4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いたメモリ線および構造を形成する装置および方法

本発明は、4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いてメモリ線および構造を製作する装置、方法およびシステムを提供する。本発明は、基板の上方に配される第1のテンプレート層からフィーチャを形成することと、フィーチャに隣接してハーフピッチの側壁スペーサを形成することと、ハーフピッチの側壁スペーサをハードマスクとして用いることによって第2のテンプレート層内により小さいフィーチャを形成することと、より小さいフィーチャに隣接して4分の1ピッチの側壁スペーサを形成することと、4分の1ピッチの側壁スペーサをハードマスクとして用いることによって導体層から導体フィーチャを形成することとを含む。多数の追加の態様が開示される。  (もっと読む)

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

半導体装置及びその製造方法

【課題】基板の内部であって、活性領域と素子分離領域との境界領域にコンタクトホールが形成された場合に、基板に流れるリーク電流を抑制できるようにする。

【解決手段】半導体基板10の上部に形成された素子分離領域10a及び活性領域10bと、半導体基板10の上に形成された絶縁膜12と、絶縁膜12に少なくとも活性領域10bを露出するように形成され、且つ、素子分離領域10aにおける活性領域10bとの境界領域を含む領域に形成されたコンタクトホール13と、コンタクトホール13における、活性領域10bの上に位置する第1の底面の上に形成された第1のバリアメタル膜14と、コンタクトホール13における、最下端に位置する第2の底面と第1の底面とをつなぐ壁面上に形成された第2のバリアメタル膜17とを備える。第2のバリアメタル膜17は、第1のバリアメタル膜14よりも比抵抗が高いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】Ruバリア上にダイレクトにめっきするプロセスにおいて、ボイドフリーの埋め込みを実現する半導体装置の製造方法を提供する。

【解決手段】半導体装置100の製造方法は、半導体基板上の絶縁膜101に凹部102を形成する工程(a)と、凹部102の側壁及び底部を覆うようにバリアメタル膜103を形成する工程(b)と、第1の電界めっき処理により、バリアメタル膜103の表面に沿ってコンフォーマルな第1の導電膜104を形成する工程(c)と、工程(c)の後、第2の電界めっき処理により、凹部内に第2の導電膜105を形成する工程(d)とを有する

(もっと読む)

コンタクト形成方法及び半導体装置の製造方法

【課題】自己組織化材料を用いて制御性の良いコンタクトを形成可能なコンタクト形成方法及び半導体装置の製造方法が提供する。

【解決手段】基板上に形成され、異なる層を電気的に接続するコンタクトの形成方法であって、第一の層上に形成された層間絶縁膜をエッチングし、前記第一の層の一部を露出させるコンタクトホールを形成する工程と、前記コンタクトホール内に導電性高分子ブロック共重合体を含む高分子膜を形成する工程と、前記高分子膜を相分離させ、前記コンタクトホール内の露出した前記第一の層上に導電性の配列構造からなるコンタクトを形成する工程と、前記コンタクト上に第二の層を形成する工程と、を備える。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

201 - 220 / 970

[ Back to top ]