Fターム[5F033XX33]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 製造工程の簡略化 (781)

Fターム[5F033XX33]に分類される特許

141 - 160 / 781

半導体装置の製造方法

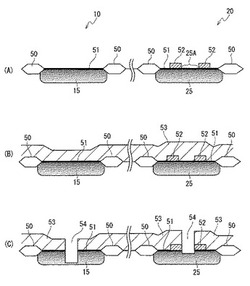

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置の製造方法

【課題】内部接続端子にクラックを生じさせない、信頼性を高めたパッケージの製造方法を提供する。

【解決手段】電極パッドを有する半導体集積回路を含む半導体チップが複数配置された半導体基板と、半導体基板上の再配線層とを有する半導体装置の製造方法であって、半導体集積回路の領域の間に位置するスクライブ領域の中に溝部を加工するため、溝部以外の領域を保護する保護マスクを半導体基板に張り付ける、保護マスク張り付け工程(S101)と、溝部を加工する溝部加工工程(S102)と、保護マスクを第1絶縁層の形成のためのスクリーンマスクとして使用して、溝部を覆うように第1絶縁層を形成する、第1絶縁層形成工程(S103)とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

電子装置の切断方法

【課題】半導体装置を含む電子装置の製造コストの増大を抑制可能であり、かつ、低誘電体膜の損傷を防止可能な電子装置の切断方法を提供すること。

【解決手段】本電子装置の切断方法は、基板上に複数の絶縁層及び複数の配線層が積層されている電子装置を準備する第1工程と、ブラスト処理を含む工程により、前記電子装置の切断可能領域に存在する全配線層及び全絶縁層を除去して前記基板を露出させる第2工程と、前記切断可能領域に露出する前記基板をブレードにより切断する第3工程と、を有する。

(もっと読む)

半導体装置

【課題】 貫通穴の開口寸法が小さく小型化や微細化を容易にでき、貫通穴全体の金属層形成速度を向上する事が容易で、金属層形成工程に要する時間を短縮する事が容易な貫通穴形状を構成した半導体装置を提供することを目的とする。

【解決手段】 基板の表面と裏面とを接続する貫通穴内に金属層を設けた半導体装置において、貫通穴側壁に表面と裏面とを結ぶ向きに複数の突起を設けた事を特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜を備えた半導体装置において、膜剥がれの発生及びリークパスの形成を抑制する。

【解決手段】半導体装置は、複数の空孔を含む層間絶縁膜16を備えている。層間絶縁膜16は、単層構造の膜である。層間絶縁膜16における、下面領域に含まれる空孔の空孔径及び上面領域に含まれる空孔の空孔径は、上面領域と下面領域との間に介在する中央領域に含まれる空孔の空孔径よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】少ない工程数で樹脂コア及び樹脂保護膜を精度良く形成する。

【解決手段】電極パッド2が形成された基板(半導体基板1)上に、電極パッド2を露出させる開口3aを有する保護絶縁膜3を形成した後、感光性樹脂膜4を形成する。感光性樹脂膜4を多階調マスク5を用いて露光した後で現像する。この現像により、感光性樹脂膜4により構成される樹脂保護膜7と、樹脂保護膜7よりも厚膜の感光性樹脂膜4のパターンにより構成される樹脂コア6と、を一度に形成する。次に、樹脂コア6上から電極パッド2上に亘って配線8を形成する。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

基板製造方法及び基板

【課題】CMPの処理時間を短縮する。

【解決手段】基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

電極基板の製造方法、電極基板、及び薄膜トランジスタ

【課題】製造工程の複雑化と製造コストの高価格化を招くことなく、多層電極間の接続を容易に行うことが可能な電極基板の製造方法、電極基板、及び薄膜トランジスタを提供する。

【解決手段】下地層の上に、下層電極、層間絶縁膜、上層電極がこの順番で積層され、下層電極と上層電極とが層間絶縁膜に形成された開口部を介して電気的に接続された電極基板の製造方法であって、下地層の上に、電極材料を含有する溶液を塗布した後、乾燥させて下層電極を形成する工程と、下層電極が形成された下地層の上に、開口部を有する層間絶縁膜を形成する工程と、開口部に溶液の溶媒を滴下し、開口部に位置する下層電極を溶解した後、乾燥させることにより、電極材料を開口部の内壁に沿ってコーヒーステイン形状に形成する工程と、電極材料が開口部の内壁に沿ってコーヒーステイン形状に形成された層間絶縁膜の上に上層電極を形成する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置の製造方法

【課題】高密度のカーボンナノチューブを容易に配線に用いることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜7にビアホール9を形成し、ビアホール9内及び絶縁膜7上に触媒部12を形成する。絶縁膜7上の触媒部12を不活化し、ビアホール9内の触媒部12を起点としてビアホール9内にカーボンナノチューブを成長させる。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】少ない工数の追加でロジック回路とメタル容量素子とを混載し、かつ、ロジック動作特性の劣化を生じることがない半導体装置の製造方法を提供する。

【解決手段】基板11上に第1層間絶縁膜13を形成し、第1層間絶縁膜13に導電体柱14A、14Bを形成する。第1層間絶縁膜13の上面に溝配線部絶縁膜15を形成する。導電体柱14Bの上方において溝配線部絶縁膜15を除去して容量用開口部151を形成し、第1層間絶縁膜15の上面に容量素子用絶縁膜16を形成する。導電体柱14Aの上方において容量素子用絶縁膜16および第1層間絶縁膜15を除去して配線用溝152を形成する。容量用開口部151および配線用溝152に金属体17A、17Bを埋め込む。容量用開口部152の金属体17Aを容量素子の上部電極とし、配線溝152の金属体17Bをロジック配線とする。

(もっと読む)

エッチング処理装置

【課題】保守作業を簡易化してエッチング処理の効率を向上させることが可能なエッチング処理装置を提供する。

【解決手段】エッチング液を収納するエッチング槽12と、エッチング槽12に接続される駆動部20、22、24と、駆動部の駆動部材の少なくとも一部に洗浄水を供給する洗浄部28、34とを備える。また、ひとつの実施形態で駆動部20、22、24は、エッチング液を揺動させる揺動機構の揺動軸36であり、前記揺動軸36は軸受けプレート35に覆われており、前記洗浄部28、34が、前記軸受けプレート25の内部に前記洗浄水を供給する。

(もっと読む)

電子部品の製造方法

【課題】側壁転写プロセスにより複数層に形成された配線層を有する電子部品を簡便且つ安価な方法で得ること。

【解決手段】パターン27の側壁に沿った閉ループを有する側壁膜30を形成し、このパターン27を除去して前記側壁膜30を残存させた後この側壁膜30をマスクとして下地材料を選択的に除去する側壁転写プロセスを用いて下層配線層21を形成する第1の工程と、前記下層配線層21の上層に、前記側壁転写プロセスを用いて1層以上の上層配線層41,51を他の層22,23,24,42,43,44を介して形成する第2の工程と、前記下層配線層21および前記上層配線層41,51のそれぞれを切断するエッチングを一括で行うことにより、前記下層配線層21と前記上層配線層41,51に対して閉ループカットを施す第3の工程と、を含む。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法

【課題】半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法を提供すること。

【解決手段】半導体装置のパターン構造物は、延長ラインと延長ラインの端部に連結されるパッドとを具備する。パッドは、延長ラインの幅より広い幅を有することができる。パッドは、パッドの側部から延長する突出部を含むことができる。パターン構造物は、単純化された工程を通じて製造されることができ、微細パターンとパッドを含む多様な半導体装置に適用することができる。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】高さ方向に隣接するメモリセル間でワード線またはビット線を共有する構造の不揮発性記憶装置において、この不揮発性記憶装置に設けられるコンタクトを形成するための工程数を従来に比して削減することができる不揮発性記憶装置を提供する。

【解決手段】ビット線BLのいずれかに接続される複数のビット線コンタクトBCと、ワード線WLに接続される複数のワード線コンタクトWCと、を備え、ビット線コンタクトBCとワード線コンタクトWCは、複数のメモリ層の形成位置に対応するコンタクト層を貫通して形成される複数のコンタクト部81〜83と、高さ方向に隣接するコンタクト部81〜83間を接続する接続配線部41−1,41−2と、を有し、接続配線部41−1,41−2は、ビット線コンタクトBCとワード線コンタクトWCとで同じ高さのコンタクト層に形成される。

(もっと読む)

141 - 160 / 781

[ Back to top ]