Fターム[5F033XX33]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 製造工程の簡略化 (781)

Fターム[5F033XX33]に分類される特許

121 - 140 / 781

半導体装置の製造方法

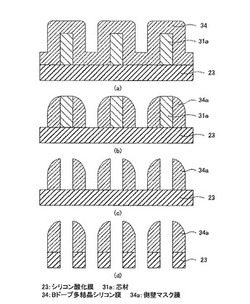

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体チップおよびこれを用いた半導体装置

【課題】接続導体との間のはんだ接合部の信頼性を確保する。

【解決手段】ジンケート法による無電解めっき法を用いて、半導体チップ1の表面側のAl電極3の上にNiめっき層5が形成される。Al電極3の上には、選択的にNiめっき層5が析出されるため、周辺耐圧構造4部分には、Niめっき層5は形成されない。また、形成されるNiめっき層5は、所定の厚さに均一に形成することができる。続いて、Niめっき層5の上にAuめっき層6が形成される。無電解めっき法を用いることによって、Auめっき層6もNiめっき層5と同様に、Niめっき層5の上に選択的、かつ均一に形成される。

(もっと読む)

半導体装置の製造方法

【課題】ホール形状を垂直として微細化を図ることができるとともに、従来に比べて工程数を削減することができ、生産性の向上を図ることのできる半導体装置の製造方法を提供する。

【解決手段】基板にホールを形成するホール形成工程と、前記ホール内にポリイミド膜を形成するポリイミド膜形成工程と、前記基板を、前記ホール内の側壁部の前記ポリイミド膜を覆うマスクを使用せずに異方性エッチングして、前記ホール内の側壁部の前記ポリイミド膜を残したまま、前記ホール内の底部の前記ポリイミド膜の少なくとも一部を除去して貫通させるプラズマエッチング工程と、前記ホール内に導体金属を充填する導体金属充填工程とを具備した半導体装置の製造方法。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】リーク電流が低く、電界効果移動度が高いなどの優れた特性を有するTFTを備え、駆動回路を内蔵して部材点数を減らすことが可能な半導体装置において、駆動回路内部における腐食などの発生を防止する。

【解決手段】本発明の半導体装置においては、駆動回路を内蔵したTFTアレイ基板100に、ゲート電極2と、ゲート絶縁膜3と、結晶性半導体部分を含んでチャネル領域4cが形成される半導体層4と、チャネル領域4cを保護するチャネル保護膜5と、半導体層4に接続されたソース電極6及びドレイン電極7を備えたTFT、並びに、ゲート電極2と同層に形成された配線層2aとソース電極6と同層に形成された配線層6aを駆動回路内部においてコンタクトホール13を介し直接接触させて接続させる配線変換部12を備えるものである。

(もっと読む)

新規有機導電性膜を使用した有機電極

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

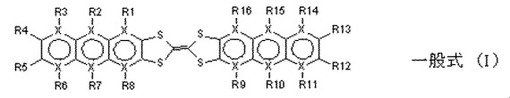

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

半導体集積回路装置及びその製造方法、並びに角速度センサ及びその調整方法及びその振動方法

【課題】電子回路とMEMSとを一般的な半導体製造技術を用いて一体化することができる半導体集積回路装置を提供する。

【解決手段】半導体基板内に設けられた電子回路と、電子回路が設けられた領域とは別の領域に設けられ少なくとも圧電体を含むMEMSを備える。電子回路の上部には多層の層間絶縁膜と、これら層間絶縁膜の所定領域に形成されたビアホールと、ビアホールに形成された第1金属プラグ、第2金属プラグ、第3金属プラグ、第4金属プラグを備える。MEMSの上部には多層の層間絶縁膜とほぼ同じ厚みを有する堆積膜を備え、堆積膜はMEMSの構造体の一部となる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化に対処しうる、製造が容易で安価な低コンタクト抵抗の半導体装置およびその製造方法を得る。

【解決手段】Si基板(1)上の不純物領域(7)を覆うように層間絶縁膜(8)が形成され、その層間絶縁膜(8)には、層間絶縁膜(8)を貫通して不純物領域(7)を掘り込むようにコンタクトホール(9)が形成されている。コンタクトホール(9)内には、金属膜(10)、バリア層(11)、金属シリサイド(12)およびソース、ドレイン配線(14)が形成されている。ソース、ドレイン配線(14)は、タングステンから形成されている。

(もっと読む)

半導体回路パターンの形成方法

【課題】スループットを短縮し、所望の回路パターンを形成することが可能な半導体回路パターンの形成方法を提供する。

【解決手段】半導体基板上に被エッチング膜を形成し、この被エッチング膜上に現像液溶解性膜を形成する。次に、現像液溶解性膜上にフォトレジスト膜を形成し、フォトマスクを介してフォトレジスト膜を露光する。さらに、現像液を用いてフォトレジスト膜を現像する。この工程では、フォトレジストパターンの下側の現像液溶解性膜を、アンダーカット状の残存部分を残すように溶解させる。次に、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程を行う。その後、現像液溶解性膜と耐エッチング膜とをマスクとして、被エッチング膜をエッチングする。

(もっと読む)

3次元半導体集積回路の製造方法及び3次元半導体集積回路

【課題】エッジ配線を用いた3次元半導体集積回路の製造方法を提供する。

【解決手段】3次元半導体集積回路の製造方法は、第1の半導体チップ10の少なくとも一つのエッジを含む表面にインクジェット機構30を用いて第1の配線14を形成する工程と、第2の半導体チップ20の少なくとも一つのエッジを含む表面にインクジェット機構30を用いて第2の配線24を形成する工程と、第1及び第2の配線14,24の位置に基づき第1の半導体チップ10と第2の半導体チップ20とを積層することにより、第1の配線14と第2の配線24とを導通させる工程と、を含む。

(もっと読む)

パターン状ポリイミド膜の形成方法、電子部品、電子部品の形成方法

【課題】 インクジェット法などの印刷手法によって、微細なパターン状ポリイミド膜を形成する方法を提供すること。さらに、容易な表面処理方法でインクジェット印刷に適した均一な基板表面を形成することができ、結果として所望のパターンのポリイミド膜が得られる塗膜形成方法を提供すること。

【解決手段】反応性の有機基を有するシランカップリング剤(A)、パーフルオロアルキル基あるいはポリシロキサン基から選ばれる基を少なくとも1つ有するシランカップリング剤(B)及びカチオン性有機基を有するシランカップリング剤(C)からなる群から選ばれる少なくとも1種を含有する表面処理剤を用いて、基板上に前記表面処理膜を形成する工程、その後に、アミド酸誘導体及びそのイミド化物から選ばれる少なくとも1種の化合物を含有するインクジェットインクを前記表面処理膜上にインクジェット塗布方法によりパターン状に形成する工程、を有する、パターン状ポリイミド膜の形成方法。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM容量素子形成時に生じる異常放電による容量絶縁膜の絶縁破壊を抑えることができて、高容量密度のMIM容量素子を得る。

【解決手段】半導体基板2上に、下部電極4−容量絶縁膜5−上部電極6からなるMIM容量素子1を有する半導体装置であって、上部電極4を構成する上部電極用金属膜は容量絶縁膜5との界面が、有機金属気相成長法(MOCVD)によりプラズマを用いないで堆積したアモルファス状のTiN膜などの金属窒化膜で構成されている。

(もっと読む)

方向転換されたカーボンナノチューブで作られた相互接続構造

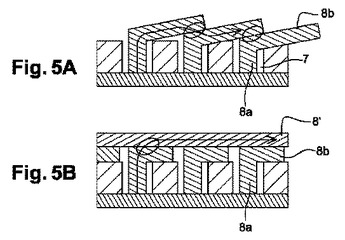

本発明は、少なくとも2つの異なる方向に沿って伸びる電気接続を含む電子デバイスであって、前記接続は本質的にカーボンナノチューブの束(CNT)(8)を用いて形成され、少なくとも2つのCNT束は、第1方向に沿った軸を有する部分(8a)と、第2方向に沿って方向転換された軸を有する部分(8b)とを含み、前記CNT束間の接続は前記少なくとも2つの束の一部分(8b)の重なりによって達成され、接続ライン(4)を形成する、電子デバイスに関する。  (もっと読む)

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

パッケージおよびその製造方法

【課題】工程時間を短縮し、平坦度(又は、ボンディングの均一性)を高め、絶縁層(絶縁基板)とチップとの間の接着力が向上したパッケージおよびその製造方法を提供することを目的とする。

【解決手段】本発明のパッケージは、パターニング層上に形成された第1導電層と、前記パターニング層上に前記第1導電層を埋め込むように形成された絶縁層と、前記絶縁層の外面に形成された第2導電層と、前記第1導電層と第2導電層とを電気的に接続するように前記絶縁層の内部に形成された第3導電層とを含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

導体トラック配列の製造方法

【課題】従来例に比べて結合容量が低下し、さらに機械的または電気的特性を向上させた導体トラック間のエアギャップの製造方法を提供する。

【解決手段】基材1、2と、少なくとも2つの導体トラック4と、空洞6と、導体トラック4を覆い、空洞6を塞ぐレジスト層5とを含む、導体トラック配列とする。導体トラック4の幅B1よりも小さい幅B2のキャリアトラックTBを形成することにより、結合容量と信号遅延を低減するためのエアギャップが、導体トラック4の下にその側面に沿ってセルフアライン技術により形成される。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

パターン形成方法及びパターン形成装置

【課題】生産性に優れたパターン形成方法及びパターン形成装置を提供することを目的とする。

【解決手段】被加工膜上の第1の領域に第1のパターン被覆率である第1のパターンを形成する工程と、第1の領域とは異なる被加工膜上の第2の領域に第2のパターン被覆率である第2のパターンを形成する工程と、を含む。第2のパターンを形成する工程は、ブロックコポリマー含有膜またはポリマー混合膜からなる第2の膜を被加工膜上に形成する工程と、第2の膜を自己組織化する工程と、自己組織化された第2の膜に含有される複数種のポリマーを、少なくとも1種類のポリマーを残すように選択的に除去することにより、第2のパターン被覆率を第1のパターン被覆率に近づけるように第2のパターンを第2の領域に形成する工程と、を有する。

(もっと読む)

121 - 140 / 781

[ Back to top ]