Fターム[5F033XX33]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 製造工程の簡略化 (781)

Fターム[5F033XX33]に分類される特許

41 - 60 / 781

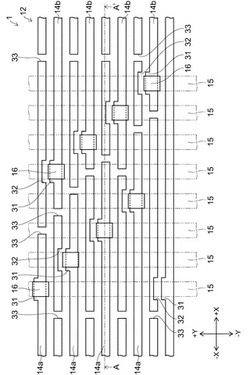

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】良好な側壁形状の開口を有する半導体装置の製造方法および半導体装置を提供する。

【解決手段】GaAs基板101上に形成された誘電体膜102の一部を誘電体膜102の表面から所定の深さまでエッチングする第1のエッチング工程と、第1のエッチング工程により誘電体膜102がエッチングされた第1のエッチング領域11において誘電体膜102をエッチングしてGaAs基板101の表面を露出し、かつ、第1のエッチング領域11を包含する第2のエッチング領域12において第1のエッチング領域11以外の領域に配置された誘電体膜102を所定の膜厚までエッチングする第2のエッチング工程とを含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 2層構造のビットライン配線において、製造工程を減少することができる半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態に係る半導体記憶装置は、半導体基板を持つ。前記半導体基板上に第1及び第2のコンタクトプラグが設けられる。前記第1のコンタクトプラグに接する第1のビットラインが設けられ、前記第2のコンタクトプラグ上には第2のビットラインが設けられる。前記第1のコンタクトプラグは、前記第1のビットラインの上面と接し、かつ前記第2のビットラインと電気的に絶縁しており、前記第2のビットラインの底面の高さは、前記第1のビットラインの上面よりも高い。

(もっと読む)

半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

高密度配線構造及びその製造方法

【課題】従来の製造方法と比べて、少ない工程数で形成可能であり、また、高精度の位置合わせ技術を必要としない、配線構造とその製造方法を提供する。

【解決手段】基板10の主表面10a上に、スペーサ絶縁膜20を形成する。次に、スペーサ絶縁膜をパターニングして、下部配線形成領域42の基板の主表面を露出させる。次に、露出した基板の主表面上、及び、スペーサ絶縁膜22の上側表面22a上に配線材料を堆積させて、基板の主表面上に下部配線52を形成するとともに、スペーサ絶縁膜の上側表面上に上部配線50を形成する。

(もっと読む)

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

金属薄膜パターンの製造方法

【課題】高温にも耐え得る矩形断面の正確な金属薄膜パターンを、簡単な工程によって製造可能とすること。

【解決手段】下記に示す感光性金属錯体を含む塗布液1を基板10に塗布し(A)マスク20を介して所定の部分のみを露光した(B)。露光によりエステル結合が切れて易溶化した可溶部1Aを(C)、TMAH水溶液により除去し(D)、不溶部1Bを金属化するまで加熱し(E)、Cu等の金属30でメッキする(F)。

【化9】 (もっと読む)

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な配線用膜を提供する。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層と、純CuまたはCu合金からなる層とを含む2層以上の積層構造を有することに要旨を有する配線用膜。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】原料である環状シロキサンの環の径を大きくすることなく、かつ空孔形成剤を用いることなく、大きな空孔を形成する多孔質層間絶縁膜を提供する。

【解決手段】トランジスタが形成されたシリコン基板10上にSiO2を主成分とする層間絶縁膜2が設けられ、さらに層間絶縁膜2の上には、多孔質層間絶縁膜1が設けられている。多孔質層間絶縁膜1には配線90およびビア91が埋め込まれている。

なお、この多孔質層間絶縁膜1は、環状シロキサンと、少なくとも1つの酸素原子を含む有機化合物と、を含む混合原料ガスを用いたプラズマCVD法により成膜している。これにより、大きな空孔径のかご型構造を有する層間絶縁膜が得られるようになる。すなわち、環状シロキサンの環の径を大きくすることなく、より大きな空孔を形成することが可能となる。大きな空孔の形成が膜密度低減に貢献し、その結果、多孔質絶縁膜の比誘電率低減が実現可能となる。

(もっと読む)

積層した接続レベルを有する集積回路装置用マスク数の低減法

【課題】3D積層メモリ装置は、各接続レベル毎に別個のマスクが使用されるので必要なマスク数は多くなるが、パターンを工夫して必要マスク数を減らす。

【解決手段】3次元積層集積回路装置は配線領域に接続レベルの積層部を有する。接続レベルの積層部で2のN乗個のレベルまで含む配線接続領域を形成するためのN個のエッチングマスクの組だけが必要とされる。幾つかの例によれば、2のX−1乗(2X−1)個の接続レベルは、連続番号Xのエッチングマスクでエッチングされ、1つのマスクがX=1であり、他の1つのマスクがX=2であり、X=Nまで付与される。当該方法は接続レベルでの形成領域に整合した配線接続領域を形成する。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】所望の微細化パターンを高精度かつ効率良く形成することができ、生産効率を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】トリミングされたフォトレジスト層104のラインパターンの上に第1の膜105を成膜する工程と、前記ラインパターンの側壁部以外にある第1の膜105およびフォトレジスト層104を除去する工程と、該除去後に残った部分の第1の膜105をマスクとして反射防止膜103とコア層102をエッチングし、コア層102をラインパターンとする工程と、ラインパターン化コア層102の上に第2の膜106を成膜する工程と、ラインパターン化コア層102の側壁部以外にある第2の膜106およびラインパターン化コア層102を除去する工程と、該除去後に残った部分の第2の膜106をマスクとして被エッチング層101をエッチングし、ラインパターンとする工程とを備えた製造方法とする。

(もっと読む)

電子デバイス及びその製造方法

【課題】バンプを排除した積層構造を備える電子デバイス、及びその製造方法を提供する。

【解決手段】本発明に係る電子デバイス1は、積層された複数枚の基板11〜13を含む。複数枚の基板は、それぞれ、板面を重ね合わせて積層され、1以上の貫通電極2を含んでいる。また、1以上の貫通電極2は、複数枚の基板11〜13のうち、2枚以上の基板11〜13にわたって延在する連続導体である。本発明に係る電子デバイス1は、このように、各基板の板面同士が重ね合わせられ、2枚以上の基板11〜13にわたって延在する連続導体である貫通電極2を備えている。したがって、本発明に係る電子デバイスは、複数枚の基板11〜13が、バンプを用いることなく、積層された構造を有している。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

41 - 60 / 781

[ Back to top ]