Fターム[5F033XX33]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 製造工程の簡略化 (781)

Fターム[5F033XX33]に分類される特許

81 - 100 / 781

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

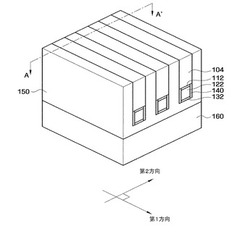

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

パターン形成体の製造方法、および有機薄膜トランジスタ

【課題】 本発明は、簡易な製造工程で高精細なパターン状に導電性パターン等を効率よく形成可能なパターン形成体の製造方法、およびその方法により形成されたパターン形成体を用いた配線基板の製造方法や有機薄膜トランジスタの製造方法等を提供することを主目的としている。

【解決手段】 上記目的を達成するために、本発明は、光触媒を含有する光触媒含有層および基体を有する光触媒含有層側基板の光触媒含有層と、撥水性を有する樹脂製基材とを対向させて配置し、パターン状にエネルギーを照射することにより、前記樹脂製基材上に水との接触角が低下した濡れ性変化パターンをパターン状に形成するエネルギー照射工程を有することを特徴とするパターン形成体の製造方法を提供する。

(もっと読む)

表示装置

【課題】画素電極上に金属膜を形成して積層構造とする際に、1つのレジストマスクを用

いて、画素電極及び金属膜を形成することを課題とする。

【解決手段】画素電極となる導電膜と金属膜を積層させる。金属膜上に半透部を有する露

光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパ

ターンを形成する。レジストパターンを用いて画素電極と、画素電極上の一部に接する金

属膜を形成する。以上により、1つのレジストマスクを用いて、画素電極及び金属膜を形

成することが可能となる。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】容量素子の良好な特性と高い信頼性を実現することが可能な半導体装置を提供する。

【解決手段】半導体基板上に第1の絶縁膜を介して形成されている下部電極と、この下部電極の周囲に形成され、下部電極の表面よりも高い表面を有するダミー電極と、下部電極上にダミー電極の最上表面よりも表面が低い位置にある誘電体膜を介して形成された上部電極と、ダミー電極に周囲を囲まれた窪みを埋める第2の絶縁膜とを具備して成る半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】第2の層間絶縁膜14に、配線の上面を露出するように、第1の開口径とされた第1の開口部16、及び第1の開口径よりも小さい第2の開口径とされた第2の開口部17を一括形成し、次いで、第1及び第2の開口部の内面を覆う高誘電率絶縁膜19を成膜し、次いで、斜めイオン注入法により、第2の開口部の底面に形成された高誘電率絶縁膜にイオンが注入されないように、少なくとも第1の開口部の底面の外周に形成された高誘電率絶縁膜にイオンを注入し、その後、ウエットエッチングにより、イオンが注入された高誘電率絶縁膜を除去し、次いで、第1及び第2の開口部内を導電膜21で埋め込むことで、第1の開口部内にコンタクトプラグ22を形成すると共に、前記第2の開口部内に、第2の開口部に高誘電率絶縁膜及び導電膜よりなるアンチヒューズ素子23を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

銅技術相互接続構造を使用する集積回路デバイス用のアルミニウム・パッド電力バスおよび信号ルーティング技術

【課題】電力バス相互接続構造の工程数を低減して製造できる半導体装置の製造方法を提供する。

【解決手段】第1のパッシベーション・スタック149を、導電性ランナ132、134および誘電体層162の上に形成する。開口を、通常のリソグラフィ技術および誘電エッチング技術によって、第1のパッシベーション・スタックを貫通して画定し形成する。露出された表面上に導電性バリア層166を形成する。アルミニウム層をブランケット堆積して、開口を充填する。パターニング、エッチング工程によって、開口内に、アルミニウム・パッド170を形成する。開口内に、ランナ134と導電性接触する導電性バイア172を形成する。アルミニウム・パッドを形成するために用いられるのと同じパターニング、エッチング工程において、アルミニウム層内に電力バス174も形成する。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

多重膜のエッチング液組成物及びそのエッチング方法

【課題】Cu/Mo積層金属膜、Cu/Mo合金積層金属膜、Cu合金/Mo合金積層金属膜のような、銅又は銅合金の1層以上の銅層と、モリブデン又はモリブデン合金の1層以上のモリブデン層とを含む多重膜を、効率的で優秀に同時に一括してエッチングすることができるエッチング液組成物及びこれを用いた多重膜のエッチング方法を提供する。

【解決手段】エッチング液組成物は、総重量に対して、リン酸50〜80wt%;硝酸0.5〜10wt%;酢酸5〜30wt%;イミダゾール0.01〜5wt%;及び残量の水を含む。添加剤イミダゾールは、銅/モリブデンガルバニック反応調節剤として機能する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作マージンを確保した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセル及び前記複数のメモリセルを選択する複数の選択配線を有するセルアレイを複数積層してなるセルアレイブロックと、第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうちの所定の第1配線が側面に接続された柱状の第1ビアと、前記第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうち前記第1配線よりも上層の所定の第2配線が側面に接続された柱状の第2ビアとを備え、前記第2配線は、前記第1配線よりも積層方向に厚く、且つ、前記第1配線よりも抵抗率が高いことを特徴とする。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

81 - 100 / 781

[ Back to top ]