Fターム[5F038AC20]の内容

Fターム[5F038AC20]に分類される特許

1 - 20 / 48

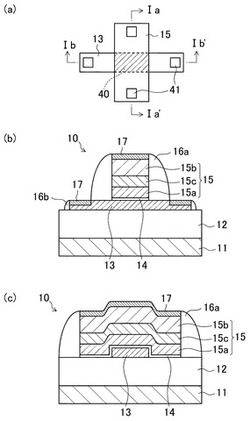

半導体装置及びその製造方法

【課題】容量値及びその変化量が大きく且つQ値の高い可変容量素子を備える半導体装置及びその製造方法を実現する。

【解決手段】半導体装置は、可変容量素子を備え、当該可変容量素子は、半導体基板11上に形成された下部電極13と、下部電極13上に形成された容量絶縁膜14と、容量絶縁膜14上に形成された上部電極15とを備える。上部電極15は、容量絶縁膜14上に位置する低濃度不純物層15aと、低濃度不純物層15a上に位置し且つ低濃度不純物層15aよりも不純物濃度が高い高濃度不純物層15bとを有する。

(もっと読む)

可変容量装置

【課題】 回路の小型化と消費電力の低減が可能な可変容量装置を提供する。

【解決手段】 容量検出回路31は、可変容量素子2の駆動容量C1のキャパシタンス値に応じた検出信号Sxと、基準となる基準信号Syとを出力する。駆動電圧制御回路21は、検出信号Sxと基準信号Syとを比較し、この比較結果に応じて駆動電圧Vcontを制御し、駆動容量C1を増加または減少させる。駆動容量C1の一端側には駆動電圧Vcontが印加され、他端側には容量検出回路31の検出用電流回路33から検出用電流Icontが周期的に入力される。このため、駆動容量C1が検出用電流回路33に接続されると、駆動容量C1のキャパシタンス値と検出用電流Icontの大きさとに応じて、駆動容量C1の他端側の電圧が上昇し、この電圧に応じた検出信号Sxが出力される。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

可変容量素子および可変容量素子の製造方法

【課題】 可変容量素子の動作不良を防止し、可変容量素子の信頼性を向上する。

【解決手段】 可変容量素子は、固定電極と、固定電極上に積層された絶縁層を含む絶縁部と、絶縁層上に絶縁層から離れる方向に移動可能に積層された可動部および可動部の一端を絶縁部に固定する固定部を含む可動電極と、可動電極に間隔を空けて対向する対向電極とを有している。

(もっと読む)

直流変換回路及び電源回路

【課題】高い信頼性を有する直流変換回路を提供する。

【解決手段】流れる電流の変化に応じて起電力が発生する誘導素子と、ゲート、ソース、及びドレインを有し、オン状態又はオフ状態になることにより、誘導素子における起電力の発生を制御するトランジスタと、トランジスタがオフ状態のときに導通状態になる整流素子と、トランジスタのオン状態又はオフ状態を制御する制御回路と、を具備し、トランジスタは、チャネル形成層として水素濃度が5×1019atoms/cm3以下である酸化物半導体層を有する構成とする。

(もっと読む)

電気化学キャパシタ

【課題】容量を高めることが可能な電気化学キャパシタを提案する。

【解決手段】基板の一平面上に正極と負極が形成される電気化学キャパシタである。また、電解質と、電解質の同一平面に接する正極及び負極とを有する。即ち、電解質の一平面上に接する正極活物質及び負極活物質と、正極活物質に接する正極集電体と、負極活物質に接する負極集電体とを有する電気化学キャパシタである。当該構成により、電気化学キャパシタの容量を増大させることができる。

(もっと読む)

半導体集積回路、及び半導体集積回路のレイアウト方法

【課題】ロジックセルを配置するためのスペースを十分に確保することのできる、半導体集積回路、半導体集積回路のレイアウト方法、半導体集積回路のレイアウトプログラム、及び半導体集積回路のレイアウト装置を提供する。

【解決手段】自動配置配線ツールにより、ロジックセル、及び前記ロジックセルに接続される信号配線をレイアウトし、ロジックセルレイアウトデータを生成するステップと、前記自動配置配線ツールにより、可変容量セル及び前記可変容量セルの容量を制御する制御配線をレイアウトし、可変容量セルレイアウトデータを生成するステップと、前記ロジックセルレイアウトデータ及び前記可変容量セルレイアウトデータに基づいて、半導体集積回路のレイアウトデータを生成するステップとを具備する。前記可変容量セルレイアウトデータを生成するステップは、前記制御配線を、同一配線層内で単位長あたりの抵抗が前記信号配線のそれと同じになるように、レイアウトするステップを含んでいる。

(もっと読む)

面積を増大させた電極を有する全電子バッテリー

【課題】改良されたエネルギー貯蔵装置を提供する。

【解決手段】2つの物理的効果を組み合わせて利用することによって、改良されたエネルギー貯蔵装置が提供される。第1の効果は、全電子バッテリー(AEB)効果と呼ぶことができるもので、キャパシタの2つの電極間で誘電体構造に埋め込まれている内包物の使用に関連する。電子は、電極と内包物との間の誘電体をトンネル現象によって通り抜け、それによって、従来のキャパシタと比べて電荷貯蔵密度を増加させることができる。第2の効果は、面積増大効果と呼ぶことができるもので、2つの電極の一方または両方で微細構造化またはナノ構造化を用い、電極幾何学的面積と比べて界面面積を向上させることに関連する。面積増大は、装置の自己放電率を低下させるのに有利である。

(もっと読む)

半導体装置

【課題】薄型化、及び小型化を達成しながら、外部ストレス、及び静電破壊に対する耐性の強化により信頼性を向上した半導体装置の提供。

【解決手段】集積回路と、共振容量部204と、を備えたICチップと、ICチップ上に設けられたアンテナ201と、アンテナ上に絶縁膜を介して少なくとも一部が重なるように設けられた導電性遮蔽体206と、を有し、アンテナと、アンテナ上に設けられた絶縁膜と、絶縁膜上に設けられた導電性遮蔽体との積層構造によって、容量素子が形成されている。

(もっと読む)

共振回路及びその製造方法並びに電子装置

【課題】振動子の構造寸法のばらつきに起因する共振周波数の変動を抑制することのできる共振回路及びその製造方法を実現する。

【解決手段】本発明の共振回路30は、基板と、該基板上に形成された固定電極12、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極13を有するMEMSレゾネータ10と、該MEMSレゾネータにバイアス電圧を印加するための電圧印加手段20と、を具備し、前記電圧印加手段は、前記可動部を構成する層と同じ層で構成され、該層の厚みで抵抗値が変化する補償用抵抗R11と、該補償用抵抗に接続され、前記可動部を構成する層と異なる構造で構成される基準抵抗R12とを分圧抵抗とし、前記補償用抵抗と前記基準抵抗の接続点電位を前記MEMSレゾネータの少なくとも一方の端子10bに出力し、前記抵抗値の変化により前記層の厚みと正の相関を有する前記バイアス電圧を前記振動子に与える分圧回路を有する。

(もっと読む)

集積回路装置、および電子機器

【課題】フィルタ回路のキャパシタ素子の容量値の適正な調整を可能にする。

【解決手段】抵抗素子の抵抗値とキャパシタ素子の容量値の積であるRC値を調整する集積回路装置100であって、少なくとも1つの抵抗素子Rfと少なくとも1つのキャパシタ素子Cfを有し、RC値によってフィルタ特性が定まるフィルタ回路150と、フィルタ回路の抵抗素子およびキャパシタ素子にそれぞれ対応する調整用抵抗素子Rおよび調整用キャパシタ素子Cを有し、調整用抵抗素子と調整用キャパシタ素子の接続ノードNrcの電圧である接続ノード電圧Vrcをモニターして、接続ノード電圧が所定電圧に達するまでの充電時間に対応する容量値設定データQcdを出力するRCキャリブレーション回路110と、を含み、フィルタ回路は、容量値設定データに基づいてキャパシタ素子の容量値を調整する。

(もっと読む)

可変容量素子、整合回路素子、および携帯端末装置

【課題】駆動電圧を小さく設定することができ、その用いられたデバイスの小型化が可能な可変容量素子を提供する。

【解決手段】基板1の表面にグランド電極3と信号が流れる信号線路2とを設け、当該信号線路2およびグランド電極3に対向し、当該信号線路2およびグランド電極3に対して接離する方向に変位可能に可動電極4を設ける。可動電極4に駆動電圧を印加することにより、信号線路2およびグランド電極3との間に静電引力を生じさせ、可動電極4を当該駆動電圧の大きさに応じて変位させる。

(もっと読む)

表面形状センサとその製造方法

【課題】信頼性が維持された表面形状センサとその製造方法を提供すること。

【解決手段】シリコン基板10と、シリコン基板10の上方に形成された層間絶縁膜40と、層間絶縁膜40の上に形成された検出電極膜44a及び静電気放電電極膜44bと、検出電極膜44a及び静電気放電電極膜44bの上に形成され、該静電気放電電極膜44bの上に第1開口51aを備えたパッシベーション膜51と、パッシベーション膜51の上に形成され、第1開口51aが露出する第1窓55aを備えたテトラヘドラルアモルファスカーボンよりなる最上層の保護絶縁膜55とを有し、静電気放電電極膜44bの最上層に第1導電性酸化金属膜45が形成された表面形状センサによる。

(もっと読む)

半導体装置およびその製造方法

【課題】エアブリッジ配線の機械的強度を向上させた高周波半導体装置を提供する。

【解決手段】半導体基板11上に形成された第1の配線層12と、この第1の配線層12の両側において、この第1の配線層12と交差する方向に配置される第2、第3の配線層13−1、13−2と、これらの第2、第3の配線層13−1、13−2間を、前記第1の配線層12上の空気層を介して相互に接続するエアブリッジ配線層14とを備え、このエアブリッジ配線層14の全体形状は上に凸のアーチ型をなしており、且つ、エアブリッジ配線14の横断面形状は下に凸状に湾曲している半導体装置。

(もっと読む)

ナノワイヤ回路構造物

ナノワイヤ回路構造物を提示する。この技術は、ナノワイヤトランジスタ(8、9)と、オープションのナノワイヤコンデンサ(12)およびナノワイヤ抵抗体(11)とを含み、2つの相互接続(1、2)だけの2レベルを使用して一体化されている。ナノワイヤ回路構造物中で、リング発振器、サンプル保持回路、比較器を実現することができる。各回路中のナノワイヤトランジスタ接続と回路入力と回路出力とは、2つの相互接続(1、2)の2レベルで提供される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】高集積化に適した、ヒューズとアンチヒューズの組み合わせ配線構造を有する半導体装置を提供する。

【解決手段】半導体基板と、この半導体基板上に設けられたアンチヒューズと、このアンチヒューズを覆うように設けられた層間絶縁膜と、この層間絶縁膜を介して前記アンチヒューズの直上に設けられ、このアンチヒューズに並列に接続されたヒューズを有する半導体装置。

(もっと読む)

電気エネルギを蓄積する装置

【課題】電気エネルギを蓄積する装置を提供する。

【解決手段】電気エネルギを蓄積する装置は、第1の磁性セクション110と、第2の磁性セクション120と、第1の磁性セクション110と第2の磁性セクション120との間に配置された誘電体セクション130と、を備える。この誘電体セクション130により電気エネルギを蓄積し、ダイポール115,125をそれぞれに有する第1の磁性セクション110および第2の磁性セクション120により電流リークを防ぐ。

(もっと読む)

センサシステム用半導体装置

【課題】小型軽量で電池交換不要なセンサシステム用半導体装置を提供する。

【解決手段】センサ(TD1,AS1,PD1,GS1)、A/D変換回路(AD1)、マイクロプロセッサ(CPU1)、メモリ(MEM1)、送信回路(RF1)、及び、電力発生装置(CM1)を備えたセンサチップ(SCHIP1)を構成する。センサ、A/D変換回路、マイクロプロセッサ、メモリ、及び、送信回路は、一方の基板面(SIDE1)上に形成し、また、電力発生装置は、前記基板面とは逆の基板面(SIDE2)上に形成する。

(もっと読む)

電気エネルギを蓄積する装置

【課題】電気エネルギを蓄積する装置を提供する。

【解決手段】電気エネルギを蓄積する装置は、第1の磁性セクション114および第2の磁性セクション118を有する第1の磁性ユニット110と、第3の磁性セクション124および第4の磁性セクション128を有する第2の磁性ユニット120と、第1の磁性ユニット110と第2の磁性ユニット120との間に配置された誘電体セクション130とを備える。誘電体セクション130により電気エネルギを蓄積し、ダイポール113,117,123,127をそれぞれに有する第1の磁性セクション114、第2の磁性セクション118、第3の磁性セクション124および第4の磁性セクション128により電流リークを防ぐ。

(もっと読む)

1 - 20 / 48

[ Back to top ]