Fターム[5F038AR01]の内容

Fターム[5F038AR01]の下位に属するFターム

抵抗体不純物濃度分布 (103)

素子分離 (60)

ピンチ抵抗、JFET効果 (9)

Fターム[5F038AR01]に分類される特許

1 - 20 / 155

半導体装置及びその製造方法

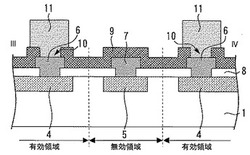

【課題】ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

(もっと読む)

半導体装置

【課題】オン抵抗を増大させることなく、ゲート−ソース間のESD耐量を向上させることのできる半導体装置を提供すること。

【解決手段】ポリシリコンゲート層を利用して形成したツェナーダイオードをESD耐量を向上させるために、並列接続させる構造を有する半導体装置とするものであって、ストライプ状または矩形状のツェナーダイオードを並列接続させて、それぞれ活性部内部に形成する半導体装置とする。

【選択図】 図3  (もっと読む)

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

半導体装置及び分圧回路

【課題】複数の抵抗の変化率差を抑制すること。

【解決手段】分圧回路11は、直列接続された2つの抵抗R1,R2を有している。第1の抵抗R1は、入力電圧Vinを供給する配線21と出力ノードN1との間に接続されている。第2の抵抗R2は、基準電圧Vsを供給する配線22と出力ノードN1との間に接続されている。第1の抵抗R1は、P型の半導体基板に形成されたN型のウェル領域(基板領域)31と、このウェル領域31に形成されたP型の拡散領域33を含む。第2の抵抗R2は、P型の半導体基板に形成されたN型のウェル領域32と、このウェル領域32に形成されたP型の拡散領域34を含む。第1のウェル領域31には、入力電圧Vinが供給される。第2のウェル領域32は、第1の拡散領域33に設定された分圧ノードNdと接続されている。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧で動作するMISトランジスタと高電圧で動作するMISトランジスタや抵抗素子等の素子とを混載した半導体装置において、不純物の導入による素子の特性のばらつきを抑える。

【解決手段】半導体装置は、第1のゲート絶縁膜4aと、第1のゲート電極6aと、第1のゲート電極6aの両側方に形成された第1のLDD領域7aと、第1のLDD領域7aの外側に位置する第1のソース/ドレイン領域13aとを有する第1のトランジスタ30を備える。第1のトランジスタ30は、第1のゲート電極6aの上面上及び側面上から第1のLDD領域7aの少なくとも一方上に亘って設けられた絶縁膜を有しており、前記絶縁膜のうち前記第1のゲート電極の側面上に設けられた部分の膜厚は、前記絶縁膜のうち前記第1のLDD領域の少なくとも一方上で最も薄い部分の膜厚よりも大きい。

(もっと読む)

半導体集積回路およびその製造方法

【課題】半導体集積回路に電源を投入後の通常の動作時にリーク電流の抑制と同時にクランプ電圧の増大防止または低下を図り、保護用MOSトランジスタのゲート電位が変動しにくい保護回路を有する半導体集積回路及び製造方法を提供する。

【解決手段】RCMOS型のESD保護回路1において、保護用MOSトランジスタ5は、内部回路6の内のチャネルの導電型が同じトランジスタに対して、仕事関数差を有する異なる電極材料からゲート電極が形成され、または、仕事関数差を設けるために異なる導電型の半導体電極材料からゲート電極が形成されることによって、単位チャネル幅あたりのリーク電流量が、より減る向きに閾値電圧が異なっている。

(もっと読む)

拡散抵抗素子およびその製造方法

【課題】ノイズおよび抵抗バラツキが小さな拡散抵抗の製造方法を提供することを目的とする。

【解決手段】半導体基板の表面付近にp型拡散層114を形成する工程と、拡散抵抗体となるp型拡散層114の第1領域の表面上に、層間絶縁膜とは異なる絶縁膜であって当該第1領域の表面を保護するカバー膜125を形成する工程と、カバー膜125を形成する工程の後、カバー膜125の前記第1領域に接する第2領域に前記第1領域よりも高い濃度で拡散抵抗体のコンタクト部となるp型拡散層116を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 シリコンビームを使用しかつダブルゲートを有する半導体装置のおけるプロセスばらつきによる抵抗値ばらつきを防止する。

【解決手段】 端部に凹部を有する基板1と、基板1の凹部に一部が埋め込まれた一対のゲート電極4と、基板1の表面であって一対のゲート電極4の間に形成された拡散層7を有し、ゲート電極4と拡散層7の間の電位を変化させることにより、拡散層7の抵抗値を変化させる。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体抵抗素子及び半導体抵抗素子を有する半導体モジュール

【課題】無駄な電流や信号の歪み等を発生させることなく、抵抗素子層の電位と、その周辺の半導体基板や電源線、信号線等の電位との電位差によって抵抗素子層の抵抗値が変化してしまうことを抑えることのできる半導体抵抗素子及び半導体抵抗素子を有する半導体モジュールを提供する。

【解決手段】抵抗素子層13は、抵抗値変化係数K1,K2によって、正極領域である領域13Aと負極領域である領域13Bとに分かれている。基準位置oから領域13Aの中心位置a又は領域13Bの中心位置bまでの間の抵抗値を量とする指標値r1,r2と、当該抵抗値R1,R2と、抵抗値変化係数K1,K2との積の総和が零になるように形成される。つまり、領域13Aの抵抗値変化成分dR1と領域13Bの抵抗値変化成分dR2とを相殺して、抵抗素子層13の抵抗値が変化してしまうのを抑えることができる。

(もっと読む)

半導体装置及びその試験方法

【課題】半導体チップに部分的に大きな電流が流れるのを抑制する技術を提供することを目的とする。

【解決手段】半導体装置は、ゲート電極5を有する半導体チップ1と、半導体チップ1の表面に設けられ、当該表面にかかる応力を検出する応力検出用素子7とを備える。そして、半導体装置は、応力検出用素子7で検出された応力に基づいて、ゲート電極5に印加される制御信号を制御する。また、平面視において半導体チップ1の中央部にかかる応力を検出する応力検出用素子7が、第1応力検出用素子7−1として設けられ、平面視において半導体チップ1の外周部にかかる応力を検出する応力検出用素子7が、第2応力検出用素子7−2として設けられることが好ましい。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離酸化膜上に所望の形状の抵抗素子を形成して、抵抗値の精度を高めて信頼性を向上させる。

【解決手段】半導体基板1の表面に形成された所定領域の素子分離酸化膜2上に複数の抵抗素子4が形成された半導体装置であって、抵抗素子4と近接する位置に活性領域3を設けた。抵抗素子4近傍の素子分離酸化膜2を必要な範囲に区切ることができ、CMP法による素子分離酸化膜2の研磨の際に素子分離酸化膜2の中央部に凹みが形成されてしまうことを抑止できるため、抵抗素子4の形状の寸法精度を向上させることが可能となる。

(もっと読む)

半導体装置

【課題】主電流Imとこれに対して比例関係にある検知電流Isとの出力用にIGBT素子44,45を備えたIGBTチップ10において、IsからIGBT素子のラッチアップを監視する。製造上のばらつきに対してIs/Imが設計値に調整可能にするとともに、調整抵抗のスペース節約や作業工数低減を図る。

【解決手段】Isを出力する原電極16とセンスパッド17と間の抵抗値を調整する調整抵抗部60は、短絡金属層67と共に作り込まれる。短絡金属層67は、調整抵抗部60の各抵抗64に対する並列接続部分により該各抵抗64の両端子を短絡している。各抵抗64は、レーザのトリミング加工により並列接続部分が切除されると、両端短絡状態を解除されて、調整抵抗部60の抵抗要素として機能する。調整抵抗部60の抵抗値は、抵抗要素となった抵抗64の接続関係及び抵抗値に応じた値になる。

(もっと読む)

保護装置

【課題】 差動信号ラインに、第1入力端子と第2入力端子を有し、ダイオードにより構成される1パッケージの保護装置を接続する場合、第1入力端子と第2入力端子間のアイソレーションを十分確保し、また、第1入力端子に接続するダイオードと第2入力端子に接続するダイオードの部品ばらつきを抑制する必要がある。また、差動信号ラインに用いる保護装置の場合、部品容量とESD破壊耐量を所望の範囲に収めるようにする必要がある。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域、第2n+型不純物領域、第3n+型不純物領域を設け、第1入力端子に接続する第1n+型不純物領域と、第2入力端子に接続する第3n+型不純物領域との間に、接地端子に接続する第2n+型不純物領域を配置して、横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

半導体装置

【課題】リードフレーム上に半導体チップが載置された半導体装置において、サージに対する耐性の向上を図る。

【解決手段】ICチップ10Aを構成するP型の半導体基板10の表面には、N型の埋め込み層11及びエピタキシャル層12と、P型の半導体層13が配置されている。半導体基板10の裏面には金属薄膜30が配置され、その金属薄膜30と、金属のアイランド51の間には銀粒子等を含む導電性ペースト40が挟まれている。半導体層13の表面に配置されたパッド電極16にサージが印加されると、半導体層13から半導体基板10に流れるサージ電流は、金属薄膜30を通って金属のアイランド51に向かう。

(もっと読む)

半導体装置

【課題】高融点金属を含む多層配線を使用してトランジスタに導入される配線がトランジスタのチャネル幅方向と垂直の方向から導入される場合においても、ESD保護用のMOSトランジスタの全体で均一に動作させることのできる半導体装置を得る。

【解決手段】複数のドレイン領域と複数のソース領域が交互に配置され、前記ドレイン領域と前記ソース領域の間にゲート電極が配置された、複数のトランジスタが一体化した構造を有するESD保護用のMOSトランジスタにおいて、ドレイン領域上に形成されるサリサイド金属領域とゲート電極との距離を、ドレイン領域上のコンタクトと基板コンタクトからの距離に応じて形成した。

(もっと読む)

1 - 20 / 155

[ Back to top ]