Fターム[5F038BH16]の内容

Fターム[5F038BH16]に分類される特許

1 - 20 / 378

半導体装置

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】複数の出力トランジスタが並列接続された構成を備え、出力トランジスタを含む各電流経路間で分担電流を高精度に均一に揃えることができる半導体装置、および当該半導体装置の駆動方法を提供する。

【解決手段】互いに並列に接続された複数の出力トランジスタを備える半導体装置であって、出力トランジスタごとに設けられ第1の制御信号を供給する駆動回路と、第1の制御信号に含める出力トランジスタのコンダクタンスの情報を有するデータを記憶するメモリと、メモリにデータを入力するための第1の外部入力端子と、各駆動回路に出力トランジスタを1つずつ入れ替わり導通させる第2の制御信号を入力するための第2の外部入力端子とを備え、各駆動回路は、メモリに記憶されている駆動対象の出力トランジスタについてのデータを読み出して、コンダクタンスの情報を含む第1の制御信号を生成する。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

温度検出回路

【課題】 消費電流を抑えるため間欠動作するようにした温度検出用半導体集積回路において、外部端子を増加させることなく回路の評価および検査が行えるようにする。

【解決手段】 発振回路(16)を備え、消費電流を抑えるため間欠動作する温度検出用半導体集積回路において、温度検出回路(11)の出力と基準電圧とを比較する電圧比較回路(13)の出力に対応した信号を出力する外部端子(DET)と、該外部端子に負電位が印加されたことを検出した場合に、温度検出回路と基準電圧回路と電圧比較回路を活性化させる信号を生成する制御回路(17)と、制御回路が活性化信号を出力しかつ温度検出回路の出力が基準電圧を超えたと電圧比較回路(13)が判定した場合に電流を流す電流回路(SW1,R0,SW2)とを設けるようにした。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

半導体装置

【課題】半導体装置の放熱効率を向上させる。

【解決手段】ぺルチェ効果によって吸熱する吸熱部(32、35、41)(37、40、43)と、ぺルチェ効果によって放熱する放熱部(31、35、41)(36、40、43)の両方が単一の半導体チップに集積化されている。このような構成によれば、半導体チップにおいて熱を拡散させ、全体としての放熱抵抗を低下させることができる。これは、放熱効率の向上に寄与する。

(もっと読む)

電圧検出回路

【課題】出力目標値の設定に別途の基準電圧源を必要とせず、かつ、出力電圧範囲の拡大と回路規模の縮小を実現することのできるレギュレータ回路を提供する

【解決手段】電圧検出回路300は、監視対象電圧Voutを分圧して第1電圧V31と第2電圧V32を生成する分圧回路(303、307〜311)と、エミッタ面積の異なるトランジスタ対(305及び306)に入力される第1電圧V31と第2電圧V32を比較して電圧検出信号S2を生成する比較回路(301、302、304〜306、312、313)と、を有する。

(もっと読む)

半導体装置

【課題】半導体基板に半導体素子と内部回路とが設けられた半導体装置において、半導体素子及び内部回路の各温度を検出するセンサを効率的に配置してレイアウトの自由度を高めることができ、且つ半導体素子及び内部回路の各温度をより正確に検出し得る構成を提供することを目的とする。

【解決手段】半導体基板5の一方面側に、スイッチング素子20と、このスイッチング素子20の配置領域から距離を隔てて内部回路30が配置されている。また、スイッチング素子20に隣接して、周囲に第1絶縁膜27が形成された第1温度検出素子24が設けられている。さらに、内部回路30よりもスイッチング素子20に近い側に、周囲に第2絶縁膜28が形成された第2温度検出素子25が設けられている。そして、第2絶縁膜28の厚さが第1絶縁膜27の厚さよりも大きくなるように構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

温度検出装置、温度検出回路およびパワー半導体モジュール

【課題】温度検出回路と絶縁素子とを同一の基板上に形成できるようにし、装置全体の小型化を容易にする温度検出装置を提供する。

【解決手段】温度検出回路200は、温度センサ35で検出された温度をデジタル値に変換するAD変換回路44とデジタル比較回路45を備えている。デジタル比較回路45の出力は、第1パルス発生器52、第2パルス発生器53を経由して絶縁トランス回路101に入力される。絶縁トランス回路101で発生する誘導電流によりパルス信号が信号復調回路102に伝達される。また、温度センサ35で検出された温度が限界温度を越えたときにコンパレータ49からパルス信号が生成され、同様に、信号復調回路102に伝達される。

(もっと読む)

半導体装置

【課題】半導体装置の定格温度(−50℃〜+150℃)において高精度の温度検出を行うことのできる半導体装置を提供すること。

【解決手段】n型基板1の第1主面に、p型ベース領域3と該ベース領域3表面層のn型エミッタ領域4と、前記基板1からなるn型ドリフト層1表面と前記エミッタ領域4表面とに挟まれるp型ベース領域3表面上にゲート酸化膜7を介して設けられるゲート電極8と、前記エミッタ領域4表面と前記ベース領域3表面に共通に接触するエミッタ電極6と、第2主面のp型コレクタ層2とを有するIGBTと、該IGBTに離間して第1主面に形成されるn型ウェル領域15表面層にn型カソード領域11とp型アノード領域12を有する温度センサダイオードを備え、前記n型ウェル領域15がp型ウェル領域16の表面層に形成され、前記温度センサダイオードのライフタイムが1μs以下に設定されている半導体装置とする。

(もっと読む)

半導体装置

【課題】半導体素子が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断できる半導体装置を提供すること。

【解決手段】半導体装置100を構成するパワー半導体素子を小さな半導体素子1に分割し、この小さな半導体素子1にそれぞれ1本のボンディングワイヤ17を接続する。小さな半導体素子1が短絡破壊したとき、破壊した小さな半導体素子1に接続するワイヤ17(ヒューズの役割をさせる)を溶断し、且つ、制御回路30からオフ信号を健全な半導体素子1に与える。このようにして、半導体装置100が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断することができる。

(もっと読む)

半導体装置

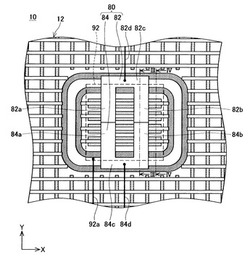

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置、及びそれを用いた装置

【課題】信頼性を向上させることができる半導体装置,半導体装置を用いた回転電機または車両を提供する。

【解決手段】ショットキ接合と、pn接合を備える半導体装置であって、pn接合は高濃度P型拡散層5とN型拡散層4で形成され、低濃度P型拡散層6と金属電極7により、ショットキ接合が形成され整流領域のpn接合部の降伏電圧を、前記ショットキ接合及びガードリング部Z2のpn接合より低くすることを特徴とする。

(もっと読む)

半導体装置及びその試験方法

【課題】半導体チップに部分的に大きな電流が流れるのを抑制する技術を提供することを目的とする。

【解決手段】半導体装置は、ゲート電極5を有する半導体チップ1と、半導体チップ1の表面に設けられ、当該表面にかかる応力を検出する応力検出用素子7とを備える。そして、半導体装置は、応力検出用素子7で検出された応力に基づいて、ゲート電極5に印加される制御信号を制御する。また、平面視において半導体チップ1の中央部にかかる応力を検出する応力検出用素子7が、第1応力検出用素子7−1として設けられ、平面視において半導体チップ1の外周部にかかる応力を検出する応力検出用素子7が、第2応力検出用素子7−2として設けられることが好ましい。

(もっと読む)

1 - 20 / 378

[ Back to top ]