Fターム[5F038CA02]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 素子配置 (1,574)

Fターム[5F038CA02]に分類される特許

201 - 220 / 1,574

光電変換装置

【課題】電圧降下が小さい整流素子を得ること、及び、コンバータ回路の作製コストを抑制することを課題とする。

【解決手段】光電変換素子と、当該光電変換素子の出力を昇圧又は降圧し、スイッチング素子及び整流素子を有するコンバータ回路と、を有する光電変換装置において、当該スイッチング素子として、ノーマリオフの第1の酸化物半導体トランジスタと、当該整流素子として、ダイオード接続されたノーマリオンの第2の酸化物半導体トランジスタとを有する光電変換装置に関する。

(もっと読む)

半導体装置及びその内部回路の制御方法

【課題】従来の半導体装置は、チップ面積を抑制しながら内部電源電圧の変動を抑制することができなかった。

【解決手段】本発明の半導体装置は、電源電圧の電圧値を他の電圧値に変換して内部電源電圧を生成する第1の電源回路PWR0、第2の電源回路PWR1と、第1の配線MT02を介して第1の電源回路PWR0から内部電源電圧VDL0の供給を受ける第1の内部回路MA0と、第2の配線MT12を介して第2の電源回路PWR1から内部電源電圧VDL1の供給を受ける第2の内部回路MA1と、第1の配線MT02と第2の配線MT12とを互いに接続するブロック間配線MT3と、第1の内部回路MA0と第2の内部回路MA1が同時に動作する期間の長さを制御する制御回路CNT0、CNT1と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体基板への高周波信号の減衰を十分に抑制し、半導体装置の特性を十分に安定させる。

【解決手段】半導体装置100は、第1導電型領域(例えばN型ウェル領域2)と、第1導電型領域の下面を覆うように配置された第1の第2導電型領域(例えばP型の半導体基板1)と、を有している。半導体装置100は、更に、第1導電型領域の側面を取り囲むように配置され、且つ、第1の第2導電型領域と接している第2の第2導電型領域(例えばP型ウェル領域3)を有している。半導体装置100は、更に、第2の第2導電型領域に電気的に接続されているとともに固定電位端子にも電気的に接続されているガードリング4と、第1導電型領域の上面を覆うように配置された絶縁膜5と、絶縁膜5上に配置されたアナログ素子(例えば抵抗素子6)と、を有する。

(もっと読む)

電流制御用半導体素子、およびそれを用いた制御装置

【課題】センス比の温度分布依存性を除去し、センスMOSFETによる電流検出の精度を向上できる電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】電流制御用半導体素子1は、同一半導体チップ上に、電流を駆動するメインMOSFET7と、メインMOSFET7に並列に接続し、メインMOSFETの電流を分流して電流検出を行うためのセンスMOSFET8とを有する。メインMOSFETは、複数のチャネルを有し、一列に配列されたマルチフィンガーMOSFETを使用して形成される。マルチフィンガーMOSFET7の中心から、最も遠いチャネルまでの距離をLとすると、マルチフィンガーMOSFETの中心から(L/(√3))の位置に最も近いチャネルを、センスMOSFET8のチャネルとして使用する。

(もっと読む)

半導体装置

【課題】ラッチ回路を有する半導体装置におけるデータの破壊を抑制する。

【解決手段】ラッチ回路に含まれる第1トランジスタP4と、ラッチ回路に含まれ、第1トランジスタP4と共通のウェル40内に形成された、第1トランジスタP4と同じ導電型の第2トランジスタP1と、第1トランジスタP4と第2トランジスタP1との間に設けられ、ウェル40を電源に接続するウェルコンタクトWCと、を備える。第1トランジスタP4側のウェル40内で発生した電荷は、ウェルコンタクトWCに流れるため、第1トランジスタP4におけるソフトエラーの影響が、第2トランジスタP1に伝搬することを抑制することができる。これにより、ラッチ回路内における2箇所のノードにおいて、同時に論理の反転が生じることを抑制することができるため、データの破壊を抑制することができる。

(もっと読む)

電界効果トランジスタの高電圧動作方法とそのバイアス回路

【課題】 ICないしLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該ICないしLSI中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートを分割してドレインにより近い分割ゲートへドレイン電位により近い電位でかつドレイン電位に応じて変化する電位を供給する手段をとる。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

インバータ回路

【課題】1チップ化しつつ、高温化による誤動作を抑制し、かつ、半導体パワー素子に流れる電流を低減し、チップサイズの増大を抑制することができるインバータ回路を提供する。

【解決手段】コンバータ電源回路部2の電源供給ライン8中、例えば、IPD20におけるパワーMOSFET220のハイサイド側に電流制限抵抗240を備える。この電流制限抵抗240によって電源供給ライン8に流れる電流の電流値を制限することができるため、パワーMOSFET220での発熱を抑制することが可能となる。したがって、インバータ回路1内の素子の定格温度を超えることを防止することが可能となり、誤動作が生じることを抑制できる。これにより、インバータ回路1の信頼性の向上を図ることが可能となる。また、パワーMOSFET220として必要な能力を軽減することが可能となり、大面積な素子としなくても済む。

(もっと読む)

半導体装置の設計方法

【課題】半導体装置を構成する回路ブロックにおけるトランジスタの信頼性劣化を考慮した半導体装置の設計方法を提供する。

【解決手段】経時劣化計算部11は、複数のトランジスタで構成される回路のネットリスト(回路記述ファイル101)、設計情報102を用いて、複数のトランジスタのうちの1つのトランジスタの回路定数を変化させて劣化後の回路動作特性(第1の特性)を算出する。解析部12は、第1の特性に変曲点があるかどうかを判定し、ある場合、変曲点に相当する回路定数を修正後の定数と決定する。変曲点がない場合、経時劣化計算部11は、更に劣化前の回路動作特性(第2の特性)を算出し、解析部12は、第1及び第2の特性に基づき、修正後の定数を決定する。解析部12は、ネットリストのうちの1つのトランジスタの回路定数を修正後の定数へ修正し、修正回路記述ファイル103を生成する。

(もっと読む)

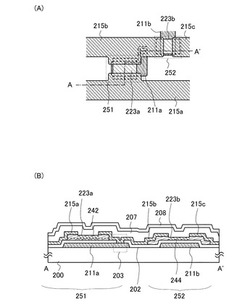

半導体装置及び製造方法

【課題】少ない層間接続プロセス工程数で、コンタクト部分の面積を小さくすることのできる半導体装置及び製造方法を提供する。

【解決手段】多層導体配線10は、スルーホール15は、導体13の一部は、ひさし部13Cとしてスルーホール15の内側に露出する。そして、スルーホール15のスルーホール用孔の内側に埋め込まれた埋め込み金属16とひさし部13Cとで、側面コンタクト構造を形成することができる。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】TXシャントトランジスタSH(TX)を構成するMISFETQN1〜MISFETQN5において、GND端子に近い側に接続されたMISFETQN5から送信端子TXに近い側に接続されたMISFETQN1になるに連れて、ゲート幅Wgが大きくなるように構成されている。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】複数の電源を使用する半導体集積回路装置において、接続対象の接続する電源配線を容易に選択ないし変更できる半導体集積回路装置及びその製造方法を提供すること。

【解決手段】半導体集積回路装置は、静電気保護素子及び入出力回路素子のうちの少なくとも1つを含む接続対象と、1以上の電源配線及びパッドから選択される2以上の要素と、同一層に形成された複数の配線と、複数の配線のうちのいずれか1つの配線と、接続対象とを電気的に接続する第1コンタクトと、を備える。複数の配線は、電源配線、パッド、又は電源配線及びパッドのうちのいずれかと電気的に接続された配線である。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

半導体装置

【課題】ダイオードセルを有する半導体装置において、ダイオードセルに隣り合う標準セルについて、光近接効果によるゲート長のばらつきを確実に抑制できるレイアウトを提供する。

【解決手段】標準セルC1は、Y方向に延び、X方向に同一ピッチで配置されたゲートパターンG1,G2,G3を有する。ダイオードセルC2は標準セルC1にY方向において隣り合っている。ゲートパターンG1,G2,G3は、各終端部e1,e2,e3がY方向において同じ位置にあり、X方向における幅が同一である。ダイオードセルC2は、ダイオードとして機能する拡散層D1〜D10に加えて、標準セルC1のゲートパターンG1,G2,G3の終端部e1,e2,e3に対向するように配置された、ゲートパターンG4,G5,G6からなる複数の対向終端部eo1,eo2,eo3を備えている。

(もっと読む)

リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法

【課題】 リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法に関し、複数種類のデバイス特性をできるかぎり同じ構造のモニタで評価する。

【解決手段】 形状或いはしきい値電圧の少なくとも一方が異なる複数種類のトランジスタを異なった領域に同じ間隔で配置するとともに、前記複数種類のトランジスタの内、設計データにおける設置頻度の比を反映した数のトランジスタのゲート電極同士、ソース電極同士、及び、ドレイン電極同士を電気的に共通に接続する。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

半導体集積回路の設計方法

【課題】フォトリソグラフィ工程で生じる光近接効果に起因するゲート長のばらつきとゲートの寄生容量のばらつきを抑制し、標準セルの実際の特性を反映させたライブラリを設計可能とし、これにより設計マージンを小さくして高性能な半導体集積回路を提供する。

【解決手段】標準セルSc1を配列して半導体集積回路を設計する方法において、標準セルSc1を構成するゲートパターン5の端部に、該ゲートパターン5と垂直な方向にダミーパターン3を配置し、該ダミーパターン3の配置により、ゲートパターン5の端部での該ゲートパターンの占有密度の低下を補う。

(もっと読む)

201 - 220 / 1,574

[ Back to top ]